基于加密USB2.0接口芯片的設計及驗證

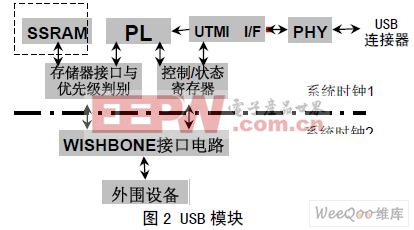

該模塊實現了符合USB2.0 規范的數據處理以及不同的外設與計算機的互連和數據通 信。 該模塊的主要功能包括:

(1) 完全支持 USB2.0 規范,提供全速模式和高速模式,其數據率分別為12Mbit/s 和 480Mbit/s。

(2) 支持 WISHBONE 接口電路和該模塊之間采用DMA 方式進行數據通信。

(3) 模塊的掛起/恢復功能。 該模塊結構如圖2 所示。其中。PHY 模塊負責將數據發送到與USB 連接器相連的計算 機,或接收來自計算機的數據;UTMI(數據通用收發宏單元接口)與PL(協議層)模塊及內部 數據存儲器、控制寄存器相連負責保持通信數據的格式符合USB2.0 規范中的協議格式; WISHBONE(主接口電路)是內部數據存儲器、控制寄存器與外部設備之間的通信橋梁。

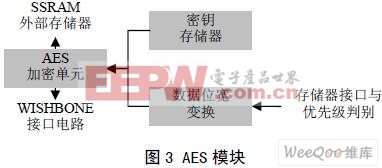

2.1.2 AES 模塊原理

該模塊負責將USB 模塊接收并解包的數據進行加密然后將加密后的數據存入外部存儲器或通過WISHBONE 接口電路送到外圍設備中。

該模塊結構圖如圖3 所示。它主要包括數據位寬變換模塊和AES 加密單元。在USB 模 塊數據接收和處理的位寬為8,而AES 加密模塊中,明文和密鑰的位寬為128,所以在USB 模塊將接收來的數據包解包后所獲得的數據不能直接加密,需要進行位寬調整后才可以加 密。數據位寬變換模塊的功能就是將PL 解包后的8 位數據連接成128 位后再送入AES 加密 單元;AES 加密單元將送入的128 位明文與密鑰存儲器中的密鑰進行十輪AddRoundkey、 SubBytes、ShiftRows、MixColumns 變換后完成明文加密,并將加密后的數據(密文)送入外 部存儲器或通過WISHBONE 接口電路送到外圍設備中。

2.2 性能分析

本文采用Stratix 系列的EP1S10F484C5 芯片對該系統進行驗證。

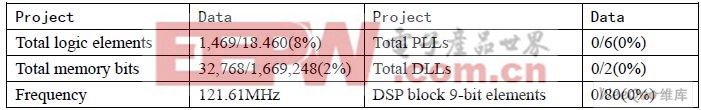

2.2.1 USB2.0 模塊的性能分析

下表為USB 模塊綜合后的性能參數:

2.2.2 AES 模塊的性能分析

當輸入信息={32 43 f6 a8 88 5a 30 8d 31 31 98 a2 e0 37 07 34},輪數Nr=10,加 密密鑰={2b 7e 15 16 28 ae d2 a6 ab f7 15 88 09 cf 4f 3c},加密結果={39 25 84 1d 02 dc 09 fb dc 11 85 97 19 6a 0b 32},經檢驗該結果是正確的,完全符合AES 加密算法。

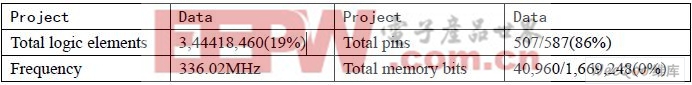

下表為AES 加密算法綜合后的數據:

2.2.3 整個系統的性能分析

下表為系統綜合后的性能參數:

由以上綜合結果分析可以得出,該系統在FPGA 上進行驗證是完全可行的,而且它的頻 率可以達到336.02MHz,完全可以實現USB480Mbits/s 的傳輸速度。

評論