誰會關心高速串行信號中的隔直電容器到底放到哪呢?

在高速串行電路中,隔直電容放到哪里好呢?一些工程師的回答無非會是兩種情況:放到驅動端或者是放到接收端。

本文引用地址:http://www.j9360.com/article/202502/467001.htm有人說放到接收端,原因是:由于信號從驅動端通過傳輸線到接收端,期間會造成衰減,上升時間也會延長,當信號最終到達接收端的電容時,大部分的高頻分量已經沒有了,反射減少了,因此能有更多的信號到達接收端。(時域)

一個SI工程師可能會告訴你:對于所有的無源鏈路,鏈路中所有的元素都是互相影響的,整個拓撲也是有關聯的,不管信號是向前傳還是向后傳都是一樣的。因此,跟電容放哪沒關系。(頻域)

為了解決這個問題,下邊用簡單的方法,通過時域和頻域的數據來分析一下這個問題。以一個簡單的拓撲為例,其中包括一段較短的傳輸線,一段較長的傳輸線,幾個過孔以及靠近其中一端的電容,如圖1所示:

圖1 簡單的拓撲結構示意圖(DC隔直電容靠近接收端)

創建每一個拓撲模型需要大量的工作,本例中,忽略了復雜的東西,僅使用簡單的集總模型來解釋這個概念。所用的理論同與精確復雜模型的一樣。

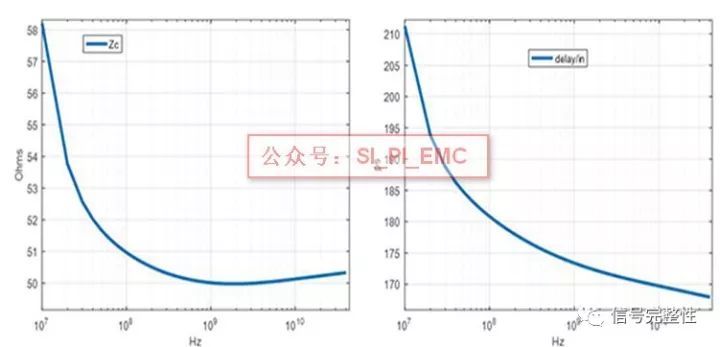

圖2顯示了一致、均勻、無源及因果性的傳輸線的RLGC參數,傳輸線的特性阻抗為50?,損耗角為0.0016,線寬為3mil,DK值為3.9,傳輸延時在1G時大約為173ps/inch。

圖2 傳輸線阻抗(左圖);傳輸線的延時(右圖)

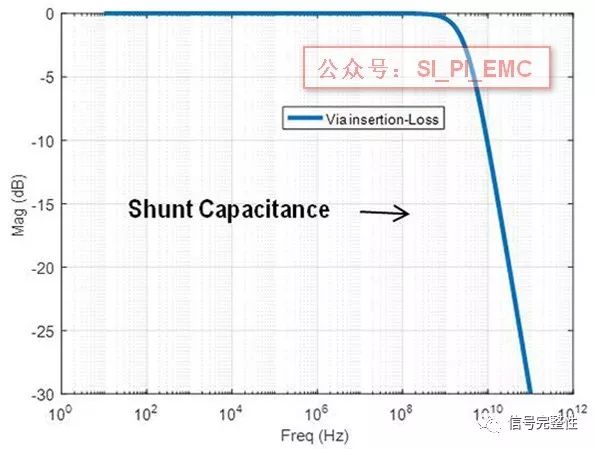

過孔賦為簡單的2pf集總并聯電容的模型,如圖3所示:

圖3 用并聯電容表示

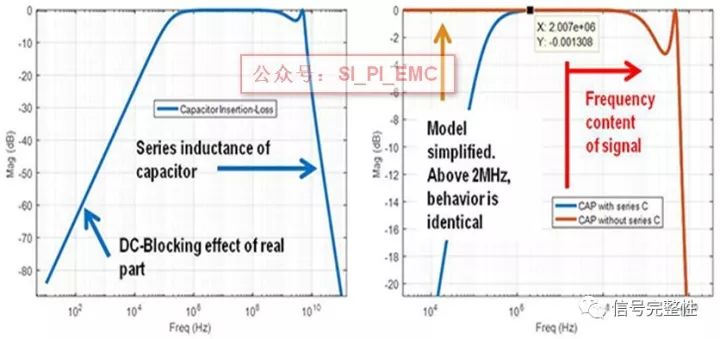

最后電容賦的模型是串聯的R-L,代替內部寄生參數,在每個末端加上一個并聯電容并連到傳輸線上,來表示焊盤和過孔,如圖4所示。

圖4

但是對于電容模型,去掉其中主要的串聯電容,這有助于建立仿真的DC路徑及進一步的TDR信號分析。即使這聽起來有點不可思議,但是大部分高速信號協議在低于100MHz的時候都是直流平衡編碼。在這些頻率點以上,在適當位置加上串聯電容或者短路的模型跟圖4中的看起來一樣,并且需要在關注的頻率點加上寄生電感和限流電容。各部分模型建好后,串聯起來,現在來回答開始的問題,如圖1,我們需要考慮兩件事:

a.Port-1是驅動端,Port-2是接收端(電容靠近接收端)

b.Port-2是驅動端,Port-1是接收端(電容靠近驅動端)

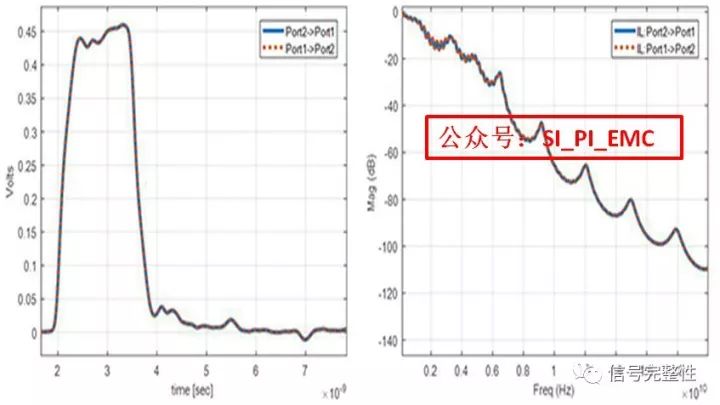

在Port-1上輸入一個脈沖,在Port-2上觀察響應,然后反向來(在Port-2上輸入信號,在Port-1上觀察響應)。如果第一個人說的對,理論上會有非常大的不連續,那么我們應該可以看到接收端波形的差別。

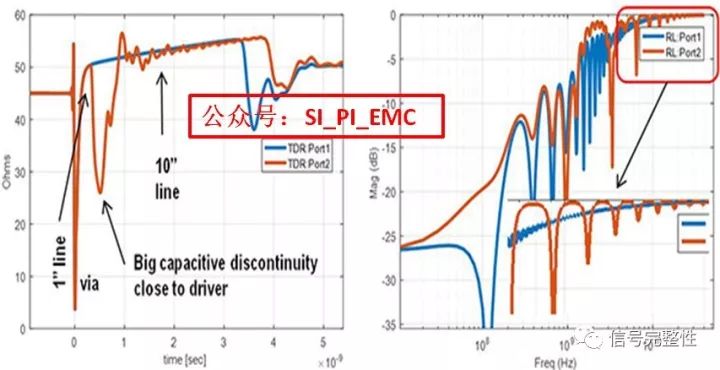

圖5 時域脈沖(左圖);前向和后向損耗(右圖)

這里問題來了,圖5中兩種情況下的結果基本上沒區別,意味著對于這個拓撲和參數來說,電容不論是放到驅動端還是接收端并沒有影響。那么第二種說法呢?S參數的相關性(對于兩端口的無源網絡,S21=S12),根據結果,在這點時域的觀點是錯的,頻域的觀點是正確的。但是,讓我們再進一步分析。

圖6顯示了TDR和兩端的回波損耗。通過TDR曲線可以清楚的看到拓撲中的每一個部分,Port-2距離隔直電容近,比Port-1的TDR不連續性大的多,類似,在頻域可以看到Port-2的回損比Port-1差好多。

由于拓撲不對稱,S11不等于S22,可能由于這個讓人覺得電容的位置會有影響,但是事實是,在這個簡單的例子中,信號向前傳輸或者是向后傳輸是一樣的,如圖5所示。

圖6 TDR曲線(端口1和2);回波損耗(S11和S22)

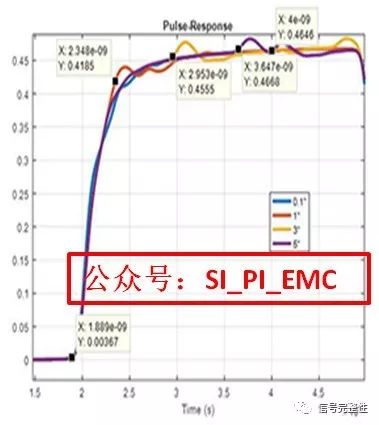

那么電容的位置到底有沒有影響?現在創建一個拓撲,總長度保持在11inch,將電容以不同的增量從一端移動到中心,理論上我們應該看不到區別。

圖7在接收端觀察到的上升時間(左圖);整個脈沖波形,放大了反射(右圖)

從圖7中可以看到一個有趣的現象,當電容從驅動端移動至傳輸線中間時,可以看到以下現象:

1.接收端的信號有變化,證明了電容在傳輸線的不同位置結果是不同的。

2.但是確定了一個位置時,不管驅動在左邊還是在右邊,在接收端產生的信號是相同的。

3.當將電容從傳輸線的中心位置移動到兩端的時候,可以觀察到兩端之間的反射脈沖在不同時刻。

4.當隔直電容分別被放到每一端時,大部分的帶寬都在上升沿,如圖7所示。

事實上簡單的看一下諧振的位置,目測每一個諧振點的起始位置,就可以找到隔直電容在某一端的大概位置。

圖8 每一類長度的1/2諧波

圖8中,通過計算后,到一端的距離為1.3243inch,近似為1inch。3.06inch近似為3inch,5.07inch和6inch近似為5inch。為什么有兩個點都近似為5inch?當把電容放到距離一端5inch的地方時,它也是距離另一端6inch的地方,因為總的線長是11inch。在5inch處,可以看到電容兩側的1/2諧波。

當然這些不連續脈沖會繼續來回幾次直到傳輸線的自然損耗將其衰減。在計算眼圖時,這些點會干擾后續的部分,最終大大降低接收端眼圖的質量。

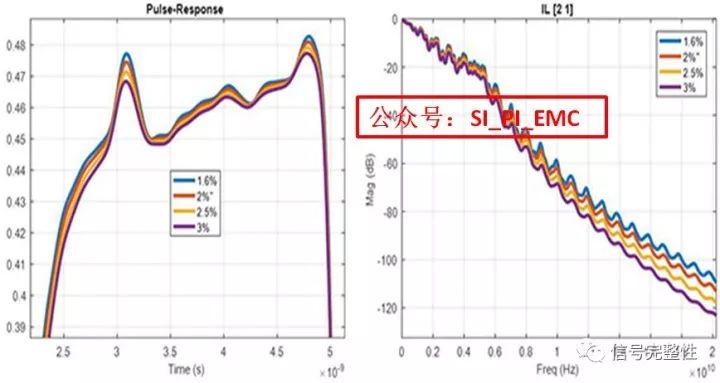

那么如果傳輸線上有更多的損耗,這些令人厭煩的諧振又會如何呢?下邊來試一下。

圖9 每一種介質損耗的諧振(左圖);損耗(右圖)

圖9中通過改變介質損耗角,可以看一下信號大體上是如何降低的,但是同樣諧振點較小,在很多情況下,可以利用損耗來衰減諧振點。

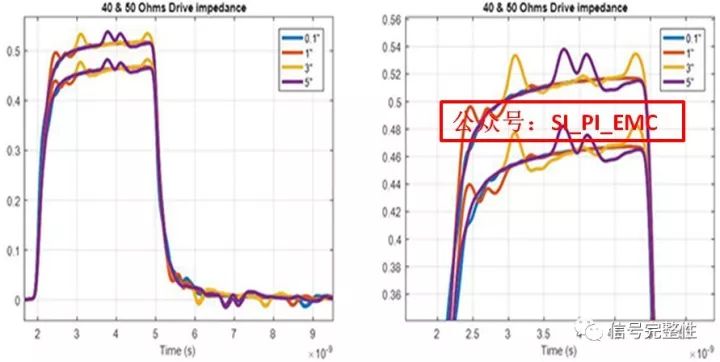

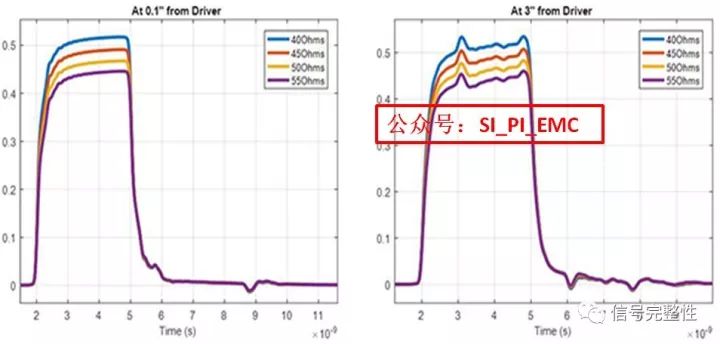

接下來再進一步的試驗,測試前,需要考慮驅動源及接收端輸入阻抗為50Ohm,完全與傳輸線的阻抗匹配。如果將電容放到驅動端會發生什么,同時改變源端阻抗,從40Ohm變到50Ohm,而接收端阻抗保持在50Ohm。

圖10 40ohm和50ohm遠端阻抗的結果

從圖10可以看出,正如預期的那樣,源端阻抗變化時電壓的穩態值,但是不連續點的大小總體上并沒有受到太大影響,不過并不是說源端和電容的不連續點不會改變信號的幅度,最終是會的。傳輸線的不連續性和兩端的不連續性之間的差異會對上邊提到的1/2諧波幅度產生直接的影響。實際上是由于該值的不連續,1/2諧波會轉化成1/4諧波。

在這個特定的例子下,源端阻抗為40-55歐姆,除了脈沖穩定狀態下的高電平像預期的一樣變化,從波形的整體上看基本上沒受太大影響。

看一下電容在兩個不同位置時所有的差分阻抗,如圖11所示,可以看出影響這些點的主要是電容的位置,不是驅動端的阻抗。

圖11 在源端0.1inch處加電容(左圖);在源端3inch處加電容(左圖)

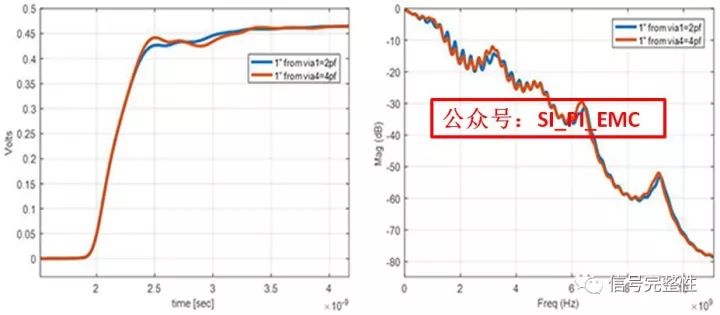

如果將里邊的電容都去掉,上邊的仿真拓撲都是對稱的,意味著在兩端均有相同數量的不連續點,那么問題是如果拓撲不是均勻的會如何呢?比如在靠近一端處有個連接器,或者其他東西,為了驗證這個問題,簡單的將一端的過孔加倍。然后同時跑兩個例子,第一個是有隔直電容的,到via4的距離為10inch,第二個的隔直電容到via4的距離為1inch。

從圖12可以看出,這兩個拓撲的結果從時域和頻域都是不一樣的。當隔直電容距離4pf的via(via4)更近時反射比較大。不要認為電容距離不連續性大的一側就是最差的選擇,可能不是,很難說這對每種情況都適用,僅僅取決于你的拓撲及不連續的類型及如何利用這些不連續點來放置電容。關鍵是嘗試通過減小反射來放置電容,從信號角度來看不管接收還是發送都沒有影響。

圖12 階躍響應(左圖);損耗(右圖)

考慮到其他因素也是很重要的,比如可拆卸接口,熱插拔,短路保護等等,都會影響放置電容的位置。但是從SI的角度看可以得出結論:

1. 電容的放置應當盡量降低傳輸線的不連續。可以想象,電容的不連續性越小,產生的反射越小。

2. 整體上電容應當離驅動端或者接收端較近,距離(Delay)最好小于1/2個UI的的長度,這樣會有利于減小對眼圖的影響,避免眼圖裕量的減少。

3. 當電容的位置確定了,就不要再考慮拓撲的外觀,跟哪端是驅動端沒關系。

現在來看最開始的問題,確實我們可以說兩種都是對的:電容在哪沒關系(從時域角度來分析),但是當我們確定了拓撲后,就不再管驅動是在哪端了,只要靠近驅動或者發送端即可(頻域)

評論