基于PC104(Plus)總線的數據接收存儲顯示系統設計

摘要:提出了一種雙通道大容量數據接收存儲顯示系統的實現方案。闡述了以PLX9054為核心、以異步FIFO為數據緩沖通道的PC104(Plus)接口電路的設計方法,同時給出了FPGA控制邏輯設計與Linux系統下基于Qt/Embedded和Framebuffer工控機存儲顯示程序的實現方法。

關鍵詞:PC104(Plus);Qt/Embedded;Framebuffer;實時存儲;同步顯示;工控機

0 引言

在現代數字信號處理領域,對于大容量高速數據的存儲和顯示是進行后續相關處理的基礎,也是信息處理系統的關鍵組成部分。隨著數字視頻視覺技術和視頻采集技術的發展,很多應用場合都需要對接收到的模擬數據進行模數轉換,然后再進行數據的實時存儲和同步顯示。為此,本文介紹了對模數轉換后的數字信號所進行的處理,提出了一種基于PC104 (Plus)總線的雙通道大容量高速數據的接收、存儲和顯示系統的設計方法。該系統通過FPGA-PC104(Plus)接口對數據進行接收和預處理,再通過FIFO數據傳輸通道來上傳數據,最后由工控機的軟件來實現數據的實時存儲和同步顯示。其中工控機軟件采用Linux(2.6內核)下Qt/Embedded的GUI來設計,并用Framebuffer的顯示技術來提供良好的人機界面交互和快速的存儲顯示操作。

1 系統結構

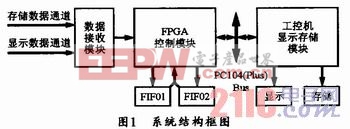

本系統由數據接收模塊、FPGA控制模塊和工控機顯示存儲模塊組成,其系統結構如圖1所示。圖中的FPGA選用Xilinx Spartan3系列的XC3S2000F456,其最大用戶IO為333個,系統門達到200萬門,并內置576KB的RAM塊;FIFO選用IDT公司的IDT72V36110,該芯片容量為512KB,可支持36位輸入、輸出數據,最高工作頻率可達166MHz;另外,PLX9054是PLX公司的總線橋接芯片,它支持多種工作模式,本系統采用C模式。在該模式下的DMA傳輸時,PLX9054對PC104(Plus)總線和本地總線都是主控制器;工控機選用Senbo公司的LX-3072PC/104 CPU模塊,該模塊搭載的AMD Geode LX800 CPU,其工作頻率高達500MHz,遵從PC/104+標準,并提供有PC104(Plus)總線,同時集成了PS/2、RT、IDE、USB2.0和10M/100M網口等接口,而且功耗低,可靠性高,可廣泛適用于數據采集、通信等領域。為了保證系統的實時性和穩定性,本工控機上運行的是Linux操作系統。

數據接收模塊的兩路輸入通道分別連向FPGA的IO端口,在FPGA模塊的控制下,兩路輸入數據同時分別進入各自的FIFO進行緩存。為了避免PLX9054控制本地端時的總線競爭以及簡化時序設計,可將兩片FIFO的輸出端復用,且經由FPGA的IO端口連向PLX9054的本地數據端,進而在FIFO產生相應狀態響應的時候,由FPGA控制模塊向PLX9054發出讀取FIFO的中斷請求,PLX9054在響應中斷后,即將數據以DMA的方式經由PC104(Plus)總線上傳至上位機,上位機通過PCI驅動讀取DMA傳輸的數據,然后進行數據分析,再分別進行存儲和顯示。

2 系統設計

2.1 數據接收模塊設計

本系統中的數據接收模塊采用J18型37針視頻通信接口,該接口協議可根據實際需求自行定義,但最大為32位。由于輸入數據為高速數字信號,因此,為防止輸入FPGA的信號產生過沖,可在視頻通信接口的后端對32位數據分別進行RC端接,并串聯33Ω的電阻和0.01μF的電容。

2.2 FPGA控制模塊設計

本系統的數據傳送采用DMA結合中斷的方式。該方式不僅能保證數據傳輸的速率,而且能提高系統的工作效率。接收高速數據時,要使用緩沖區對數據進行緩存,但是,如果等緩沖區全部存滿以后再進行DMA傳輸,那么,在數據流速率比較高的時候,就會造成數據的丟失。因此,在FIFO半滿時就必須進行數據的DMA傳輸,這樣可使工控機從FIFO讀取數據和FPGA從外部接收數據能同時進行。

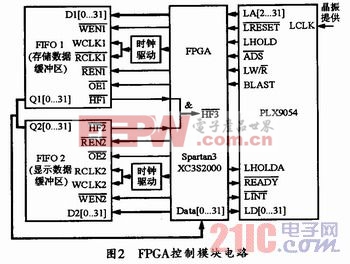

FPGA控制模塊是本系統的硬件核心,其主要功能是完成系統復位,接收數據進行緩存,控制讀取兩個FIFO數據的邏輯順序,并控制DMA傳輸。FPGA控制模塊電路如圖2所示。

在圖2電路中,為了保證FPGA與FIFO同步工作,應將兩片FIFO的各自讀寫時鐘連接在一起,且分別由FPGA輸入到時鐘驅動芯片以后獲得。

評論