下一代芯片的關鍵:芯片互連技術的創新

芯片模塊是具有明確定義功能的小型芯片,可以與其他芯片模塊結合到一個單一的封裝或系統中。芯片模塊之間密集的互連確保了快速、高帶寬的電連接。本文討論了既包括中間層技術又包括三維集成方法,旨在將互連間距縮小到 1μm 以下。

本文引用地址:http://www.j9360.com/article/202407/461494.htm這是專門討論芯片組件的兩部分系列的第一部分。本系列涉及互連技術的最新發展。

芯片模塊化技術,超越炒作

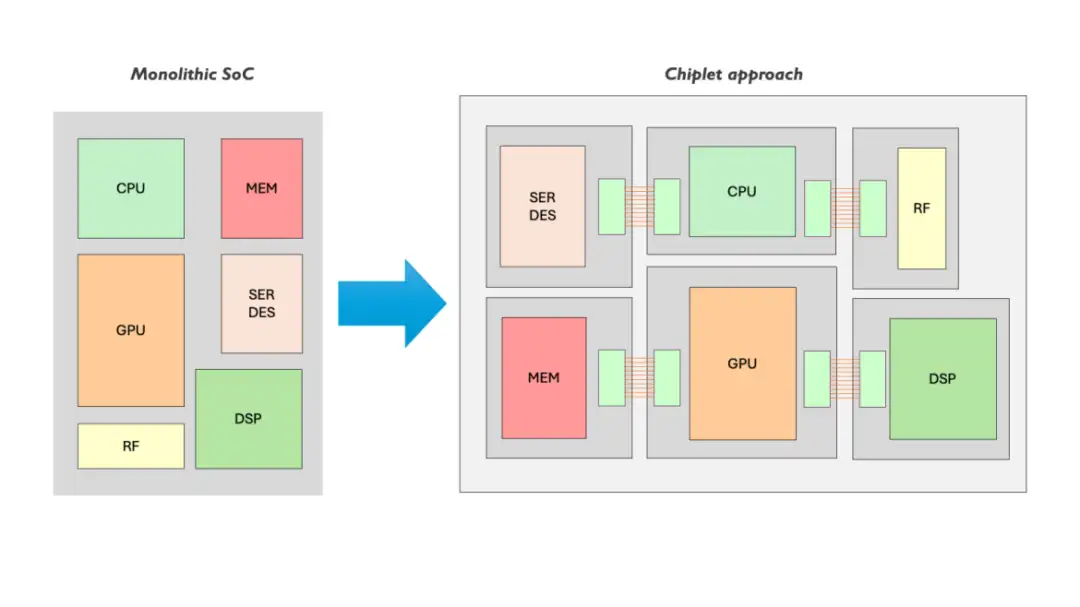

《麻省理工科技評論》將芯片模塊化技術評為 2024 年十大突破技術之一,芯片模塊化技術已經引起了半導體界的廣泛關注。芯片模塊化技術指的是小型的、專用功能的芯片模塊,例如 CPU 或 GPU,可以混合搭配組成完整的系統。這種類似樂高積木的方法賦予制造商靈活性,可以以更低的成本設計新的芯片,并提升效率和性能。芯片模塊化技術實現優化的一個方法是通過戰略性地定制技術。例如,IO 和總線芯片模塊使用可靠的傳統工藝節點,而計算芯片模塊則采用尖端技術以達到最高性能。內存芯片模塊則采納新興的存儲技術,確保適應多樣化的半導體需求。此外,基于芯片模塊的設計加速了開發過程,因為過時的芯片模塊可以更輕松、更頻繁地進行更新。且芯片模塊通常擁有較高的良率,因為它們通常體積較小、設計較簡單,在預鍵合測試后即可使用已知良好的芯片,并且可以依靠修復策略來修復有缺陷的互連。

分解大型單片式片上系統

芯片模塊化設計應對了幾十年來推動半導體行業的摩爾定律放緩。為了確保集成電路元件每兩年翻倍,芯片制造商們探索了使晶體管變小并在芯片上集成更多元件的方法,導致了龐大的單片式片上系統(SoC)設計。移動電話就是單片式設計成功的證明,它將數學功能、顯示、無線通信、音頻等集成到一個僅 100 平方毫米的芯片中。然而,進一步的縮小也使得性能優勢相對而言昂貴得多。因此,將大型復雜的 SoC 分解為更小的芯片模塊,并將它們連接起來以構建特定應用系統的想法應運而生。

汽車行業是采用芯片模塊化技術的理想候選者,提供了具有基礎功能芯片模塊的靈活電子架構,增加了特定組件,包括用于自動駕駛、傳感器融合和其他電子功能的芯片模塊。模塊化方法縮短了上市時間,相比于升級單一的單片式 SoC 所涉及的漫長過程,可以在車輛生產線的生命周期內替換或更新芯片模塊。此外,汽車銷量,特別是考慮到特定車型和類型時,通常比移動電話的銷量要小。因此,為每個車型(部分)重新設計單片式 SoC 將導致高昂的工程成本。最后,芯片模塊化還提供了靈活性,幫助汽車制造商滿足已在其他車型中證明可靠性和安全性的芯片需求。

隨著芯片模塊市場的快速增長,預計這種模塊化設計將出現在更多應用領域,例如成像器件、顯示器件、存儲器件和量子計算等。

圖 1 芯片模塊化系統將來自不同供應商和技術節點的獨立芯片組合在一起,而不是將所有功能設計集成到一個單一的片上系統中。

連接這些「積木」

芯片模塊化能否成功跟上摩爾定律的步伐,很大程度上取決于如何將芯片模塊緊密地放置在一個封裝內,以確保它們之間快速、高帶寬的電連接,就像單片式 SoC 中的功能一樣。

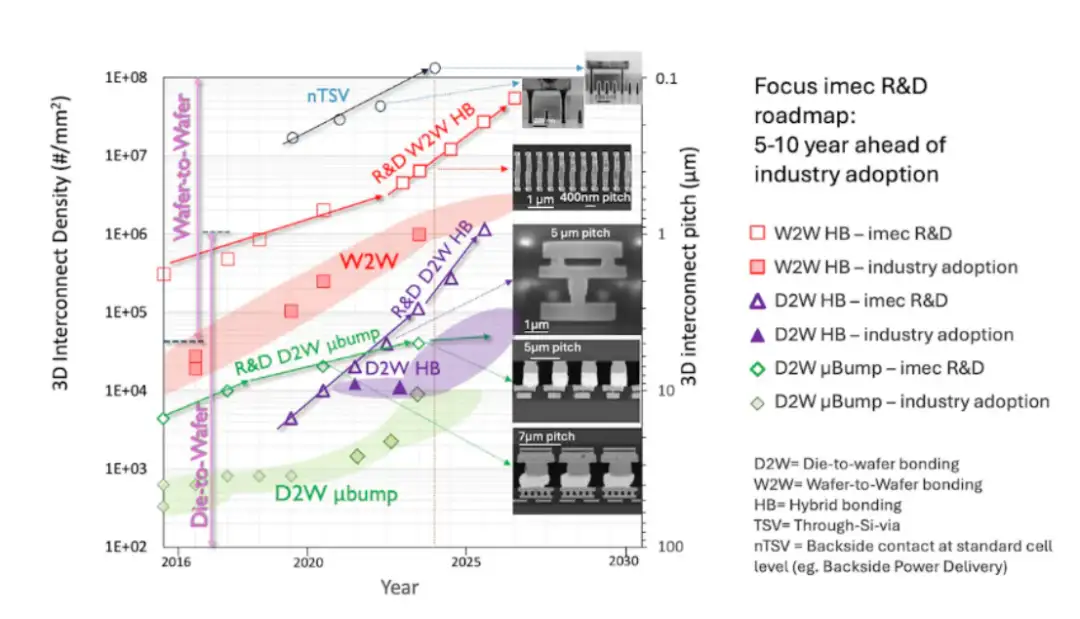

在三維系統集成中,出現了兩個主要的行業方向:2.5D 芯片模塊集成通過共同基板(也稱為中間層)將芯片并排連接在一起,而 3D-SoC 則是將芯片模塊垂直堆疊在一起。

2.5D 中間層技術

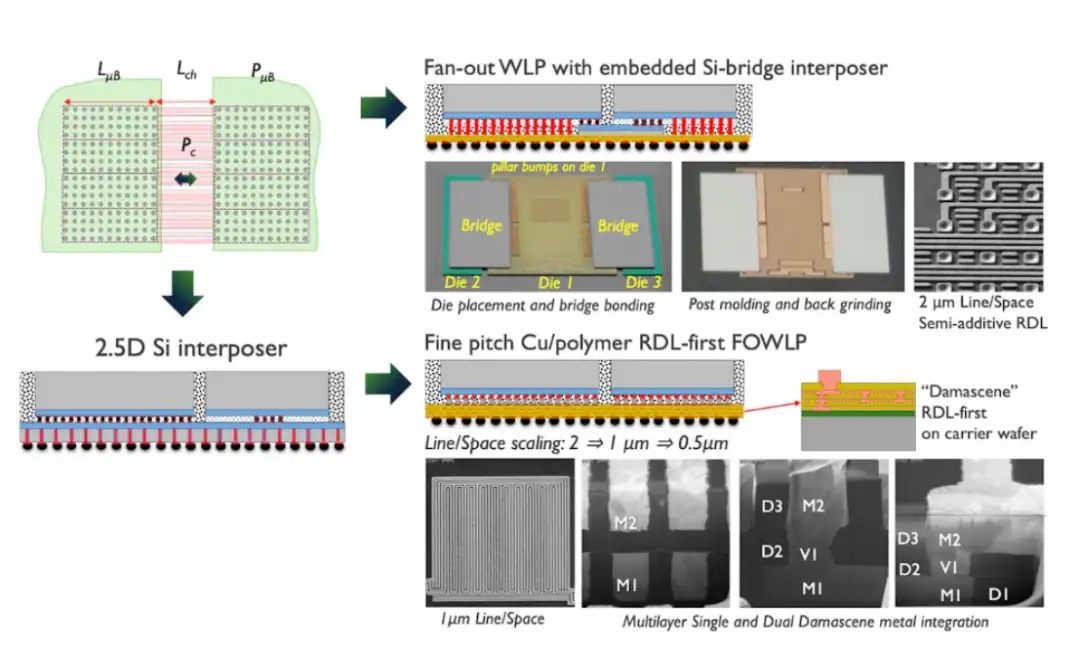

在 2.5D 集成中,芯片模塊通過共同的基座(如硅、有機聚合物、玻璃或層壓材料)進行連接。Imec 目前專注于硅和有機基座的研究和優化。雖然硅中間層在高性能應用中已經成為一種成熟的技術,具有優異的細小間距和良好的熱電性能,但其成本和復雜性也較高。因此,有機基質作為替代方案正受到研究和優化。

早期的芯片模塊集成主要集中在使用硅中間層基座在芯片模塊之間建立連接。這涉及將兩個獨立的芯片模塊非常接近地放置在共同的中間層上(間距小于 50μm),中間層上有微米級別的布線來建立連接。硅中間層利用傳統的 BEOL 銅/氧化物坑填法工藝實現微米及亞微米級別的連接間距,并具有非常高的良率。

雖然這仍然是一種有效的方法,但替代技術正在引起人們的興趣,因為它可能會帶來更具成本效益的解決方案。Imec 提供的一個選擇是硅「橋」,這是一個小型的硅中間層,只在芯片模塊的邊緣連接它們。

另一種替代方案是超細的重分配層(RDL)互連技術,它將硅替換為有機聚合物,內嵌一層銅線用于連接芯片模塊。Imec 目前正在優化這項技術,努力達到與硅相似的互連密度,并改善其與硅的兼容性。就互連間距而言,中間層仍然以亞微米級別的間距處于領先地位;Imec 正在目標 2μm 的 RDL 間距,并計劃在未來進一步減小至亞微米級別。

圖 2 芯片模塊可以通過硅中間層進行集成。Imec 也在研究諸如硅橋或有機 RDL 等替代方案。

除了探索替代硅中間層技術之外,Imec 還在研究如何通過增加額外功能使中間層成為一個更有價值的組件。例如,一個中間層可以增加額外的解耦電容器,用于保護芯片模塊免受噪聲和電源異常的影響。

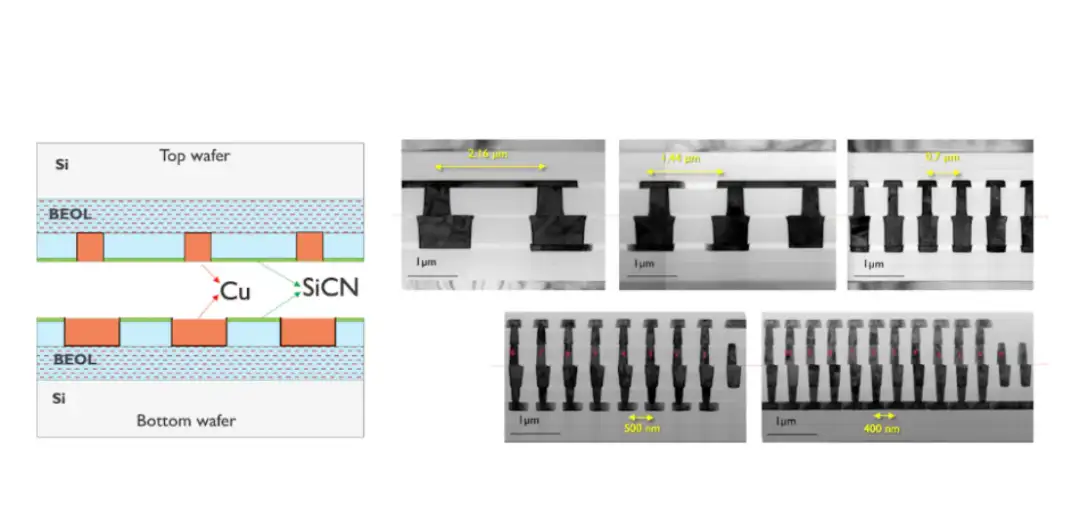

三維片上系統:混合鍵合實現亞微米間距

某些應用,如高性能計算,可能需要更高性能、更小尺寸或更高級別系統集成,因此更傾向于完全的三維方法。與建立側向連接不同,芯片模塊可以堆疊在一起,形成三維片上系統(3D-SoC)。這種方法不是添加額外的模塊,而是共同設計芯片模塊,并讓它們像同一芯片一樣運行。芯片對芯片的混合鍵合是實現三維片上系統在亞微米級互連密度水平的關鍵技術。它涉及使用低膨脹系數將兩個硅芯片模塊連接在一起。這一過程的關鍵組成部分是介電層,它使堆疊層的表面平整并激活,以實現有效的鍵合,并在堆疊的不同芯片模塊之間提供電氣絕緣。Imec 采用 SiCN 作為鍵合介電層的專有方法,將互連間距縮小至 700 納米。其技術路線圖甚至預測了 400 納米和 200 納米的間距。

圖 3 芯片對芯片的混合鍵合是實現亞微米級互連密度三維片上系統(3D-SoC)集成的關鍵技術。Imec 采用 SiCN 作為鍵合介電層的專有方法,使互連間距縮減至 400 納米。

微凸點與混合鍵合的比較

在 2.5D 技術中,芯片模塊通過小型焊料凸點放置在中間層上,實現電氣和機械連接。這些微凸點之間的間距越細,連接速度和穩定性就越高。工業中的微凸點通常達到 50μm 到 30μm 的間距。Imec 正在研究如何將這一間距減少到 10μm 甚至 5μm。

與 2.5D 中使用的微凸點相比,3D 堆疊中的混合鍵合可以實現顯著更小的間距。那么,混合鍵合可以在所有地方都使用嗎?確實,在芯片對芯片的方法(基于硅),芯片模塊可以鍵合到硅中間層上,達到幾微米的間距。不過,與目前最佳的芯片對芯片放置精度接近 250 納米相比,最前沿的芯片對芯片鍵合可以達到 100 納米的疊加精度。預計鍵合設備和相關工藝的改進將進一步減少這些數字約 50%。然而,混合鍵合涉及額外的加工步驟,如表面激活和對準,這可能會影響制造成本。

芯片對芯片鍵合、芯片對芯片鍵合和微凸點將在成本、間距、兼容性和互操作性之間進行權衡。在 2.5D 中,芯片模塊通常來自不同的供應商,并已經經歷了一系列的測試和處理。由于微凸點提供了一種無需表面準備的標準化方法,它們將是首選。此外,對于有機 RDL,由于有機聚合物在加熱時膨脹較多且不能被充分平整,微凸點仍然是首選的方法。

總結思考

隨著技術的擴展變得更加復雜,并推高了設計和加工成本,在最先進的技術節點上開發專用 SoC 變得更具挑戰性——想想汽車行業中過多的模型和類型。將功能和技術節點分離到不同的芯片模塊中,證明比在先進工藝技術中制造龐大的芯片具有更高的成本效益,并帶來了空間和性能上的優勢。

雖然模塊化方法可以解決多芯片封裝的復雜性和成本問題,但這種范式轉變也帶來了特定的技術挑戰。尺寸只是其中的一個挑戰。芯片模塊研究的一個重要方向是使互連更小化,或者探索將不同部件整合在一起的不同概念。當堆疊芯片模塊時,熱問題和電力傳輸(通過背面電力輸送網絡等新型架構解決)變得至關重要。最后,還需要進一步的標準化工作,以確保不同芯片模塊之間的兼容性和通信。

圖 4 Imec 的 3D 互連路線圖總結了互連小芯片的不同方法以及預計的互連密度和間距。

評論