從AGI 到互聯技術元年,重塑算力世界秩序

本文引用地址:http://www.j9360.com/article/202403/456496.htm

ChatGPT 誕生一年后,以Sora為代表的 AGI 實現突破性進展,再度引爆了高性能計算市場。面對以天為單位飛速迭代的算力需求,以及單個處理器性能的增長困境(Scale up),促使企業轉向擴展計算集群規模,踏上Scale out 之路。從此,行業所面臨的核心挑戰也從“單個芯片-集群”,“算力-互聯”轉變。伴隨AGI的誕生,互聯元年同步開啟。

2024年3月5日,互聯領域先行者奇異摩爾在“奇芯合粒 異往無前”2024春季發布會上正式推出了基于 Kiwi SoChiplet Platform 的全系列互聯產品及全棧式互聯解決方案。該系列產品包含“高性能互聯芯粒IO Die、高性能互聯底座 Kiwi 3D Base Die、UCIe 標準 Die2Die IP以及網絡加速芯粒NDSA Family”,全面覆蓋片內、片間直至網間的互聯場景。基于IO Die,奇異摩爾及合作伙伴Ventana宣布共同推出了全球首款服務器級的RISC-V CPU;同時,奇異摩爾也基于Base Die發布了全球首款3DIC AI芯片“AI Booster”。

UCIe Board member 陳健在發布會上表示 “在Deep Learning、大模型時代激增的算力需求、摩爾定律放緩、封裝技術演進”等多種因素的共同作用下,Chiplet和IO Die為代表的互聯芯粒因在良率、先進制程解耦、復用能力等方面所顯示出的優勢,成為了歷史的選擇。基于Chiplet架構和通用互聯標準,一個開放性、跨公司、支持規模化復用的“貨架芯片”市場正逐步成為全行業的愿景。

這一愿景依賴于模型創新和無盡的算力需求。如今,從微軟到谷歌,從阿里到字節跳動,萬卡集群儼然成為大模型訓練的標配。想支撐更大的模型,算力基礎設施和生產方式必須同步轉變。首先,異構加速和超大規模平臺,使更大規模的集群設計成為可能;其次,想通過Scale Out方式提升集群算力,必須從網絡層面著手,互聯三要素 “Bandwidth, Efficiency, Workload”缺一不可。

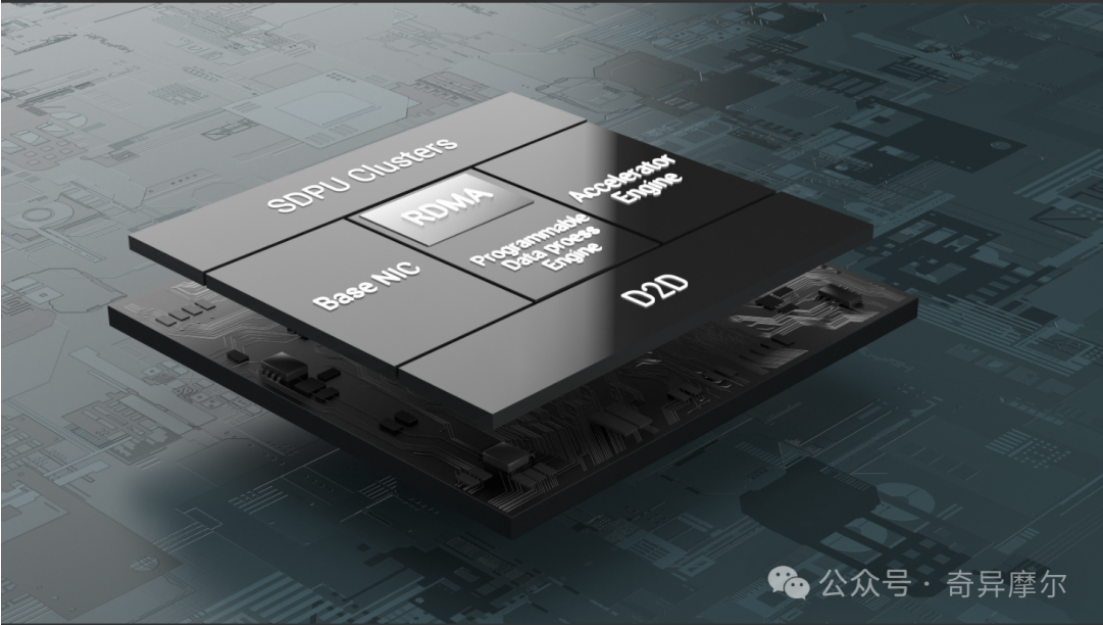

在網絡側,奇異摩爾自研的高性能網絡加速芯粒Kiwi NDSA(Network Domain Specific Accelerator)系列,內建RoCE V2 高性能 RDMA (Remote Direct Memory Access) 和數十種卸載/加速引擎,可作為獨立芯粒,實現系統不同位置的加速。同時,通過硬件可配置,軟件可編程的靈活軟硬件架構,能夠滿足客戶對復雜業務場景的多樣化需求。得益于Chiplet、RISC-V和FPGA的靈活組合,Kiwi NDSA 出色的平衡了通用與專用,性能和成本間的矛盾。

據奇異摩爾產品及解決方案副總裁祝俊東介紹,奇異摩爾NDSA家族產品之一,“NDSA-RN-F” 將于近期問世。作為全球首批200/400G的高性能FPGA RDMA網卡,“NDSA-RN-F”具備極高的集群擴展能力,可以大幅提升集群節點間的東西向流量交互效率,使得更大規模的集群設計成為可能。同時擁有us級超低延時,支持約數十 MQP高并發,性能遠超同類FPGA產品,并媲美全球標桿 ASIC產品。

NDSA家族產品之二,全球首款支持800G帶寬的RDMA NIC Chiplet產品 “NDSA-RN”。其性能更為強勁,除帶寬升級到800G之外,延時也降至ns級,并支持數十GB的超大規模數據包,性能將超越目前全球標桿ASIC產品。

網間互聯的瓶頸與痛點,并非為云服務廠商獨有。存算一體的環境中,互聯芯粒能有效提升系統性能、集成度、可擴展性和可靠性。億鑄科技副總裁李明表示,AI大算力芯片競爭核心正逐漸轉向 “存儲、算力,破除墻”等挑戰。存算一體在破除“存儲墻”方面具有先天優勢。億鑄致力于結合存算一體+Chiplet芯粒優勢,在AI算力芯片產業格局的基礎上,貢獻更具性價比、能效比、算力發展空間的AI大算力芯片發展新路徑。

芯片間互聯場景,受AI等各類大算力場景的驅動,計算架構將從異構計算進一步走向多種異構融合的超異構并行計算,片間互聯瓶頸進一步凸顯。NDSA家族產品之三,奇異摩爾自研的全球首創GPU Link Chiplet “NDSA-G2G”,通過RDMA和D2D技術,在芯片間搭建了高速數據交換網絡,可實現近TB/s的超高速數據傳輸,其性能達到全球領先水平,滿足AI芯片對于片間交換不斷增長的需求。

Die間互聯:Die-to-Die IP

Die間互聯領域,奇異摩爾宣布將正式發布全球首批支持 UCIe V1.1 的 Die2Die IP “Kiwi-Link”,互聯速度高達 32GT/s,延時低至數nS。全面支持UCIe、CXL、Streaming等主流協議,即插即用;同時支持標準封裝/先進封裝等多種封裝形態。

“為達到貨架芯粒的愿景,開放互通的D2D標準是關鍵因素” ,陳健介紹,UCIe 最新1.1標準在1.0標準基礎上進行了全方面的升級,其中包括汽車行業增強特性,全棧流協議,封裝成本優化和測試認證。作為構建開放芯粒生態的標準組織,UCIe 將通過各方面的努力促成Chiplet生態的發展和成熟。

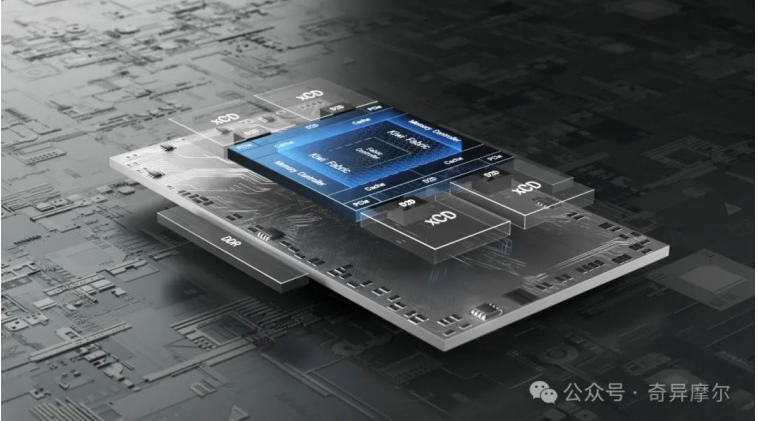

微觀層面,在摩爾定律放緩背景下,為持續提升單個芯片設計規模及能效,片內互聯技術創造了新的工程成就。作為發布會的亮點,首次登臺亮相的 Kiwi SoChiplet Platform 是奇異摩爾所發布這一系列互聯產品的基礎。其基于高性能互聯網絡Kiwi Fabric,可高效連接、調度海量高速節點,實現多Die間高帶寬、低延時的互聯。

祝俊東介紹:Kiwi SoChiplet Platform在支持芯粒數量、CPU Core、Die2Die帶寬、Memory 帶寬、Ext Interface 等關鍵指標方面,均達到國際領先水平。基于該平臺,客戶可以輕松構建多樣化的產品線,實現連接計算和存儲/連接的分離,以相對低的成本使產品及性能持續保持國際領先水準。

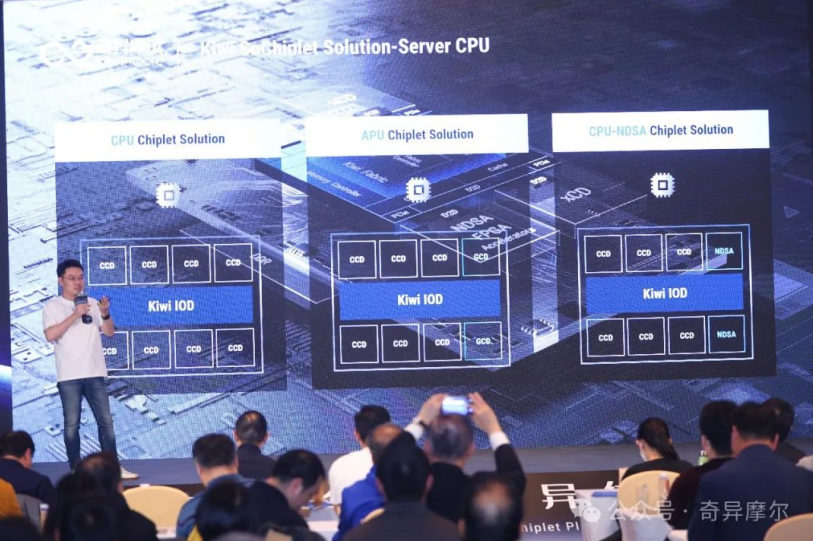

全球首款數據中心級,通用互聯芯粒Kiwi IO Die

從Kiwi SoChiplet Platform 出發,奇異摩爾推出了全球首款數據中心級通用互聯芯粒 Kiwi IO Die,內部集成了如D2DDDRPCIeCXL等大量存儲、互聯接口。客戶可以根據企業自身需求,圍繞IO Die,輕松搭建低/中/高性能的數據中心處理器。該平臺最高支持10+Chiplets、構建高達192 core CPU或1000T GPU的算力平臺。

發布會上,奇異摩爾及高性能RISC-V領域的領導者 Ventana Micro公開展示了基于Kiwi IO Die的應用方案。雙方以遠低于傳統 SoC 構建的時間和成本創建了一款高性能數據中心級RISC-V處理器,并就此打造了RISC-V CPU Chiplet Platform,實現了RISC-V與互聯技術組合的跨越性一步。

在本次發布的RISC-V CPU Chiplet中,計算單元部分,即Ventana Veyron V2處理器,在其前身V1基礎上進行了重大升級,提供更好的Performance/W。每個芯粒包括32個核心,多顆芯粒基于chiplet架構,通過UCIe接口,連接到奇異摩爾提供的高性能IO Die上,實現最高192個內核,支持包括奇異摩爾NDSA在內的多種領域加速器。

Ventana創始人兼CEO Balaji Baktha表示:Ventana 和奇異摩爾共同建立了一個可擴展架構,可將多個Ventana Veyron V2 與 奇異摩爾 的I/O Die組成不同配置的SoC,從而獲得功率、成本和SKU優化。這種方案不僅提高了靈活性,允許用戶根據需要調整AI應用的規模和性能,也能有效避免對單一供應商的依賴,使客戶在競爭激烈的市場中脫穎而出。

“RISC-V和Chiplet的目標同為構建一個成本更加低廉,更加普惠的算力世界,二者的組合充滿想象力,將會塑造全新的商業形態。” 陳健就此表示。

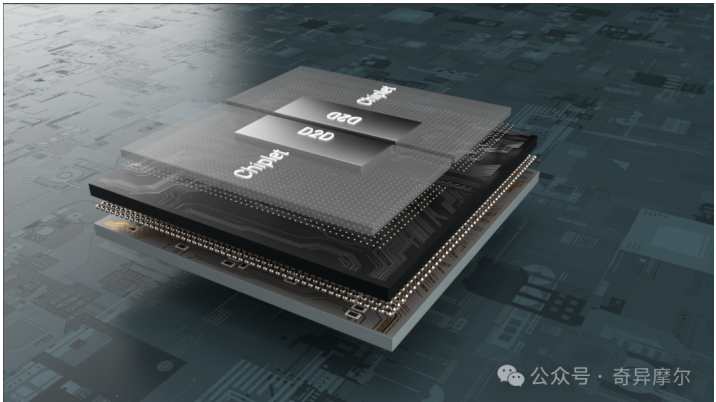

Kiwi 3D Base Die,為Edge AI提速

隨著大模型發展,推理需求不斷增長。根據 OpenAI 論文:Scaling Laws for Neural Language Models 測算,Sora 推理算力需求是 GPT-4 的 1000 倍以上。為應對不斷飛漲的推理需求,在片內,互聯趨勢已從2.5D擴展至3D層面。奇異摩爾全球首款通用高性能互聯底座 Kiwi 3D Base Die,實現了通用互聯芯粒在帶寬、能效、搭載芯片數量等多方面的突破性進展。

Kiwi 3D Base Die具有極高的互聯密度,通過3D D2D、PCIe等高速接口,能夠以20%的功耗實現8倍于2.5D結構的互聯密度;其具備卓越的通用性和靈活性,最高可實現16顆算力芯粒堆疊,并可通過高速外部接口連接不同的Host SoC單元,充分利用客戶現有硬件資源;同時集成了大容量3D Cache,在真正意義上將存儲、計算、互聯功能整合為一體。

根據自身需求,客戶無需流片,只需在Base Die上封裝不同數目的算力芯粒,外接HBM,即可快速形成應對不同場景的高性能芯片,特別適用于覆蓋多個細分垂直市場的企業。

基于3D Base Die,奇異摩爾面向Edge AI,正式推出了全球首款通用3DIC Chiplet “AI Booster”,將32顆存算一體芯粒單元整合在一起,通過底層的Base Die進行垂直互聯,從而實現性能和靈活性的完美兼容。

針對AI Booster設計方面的經驗,奇異摩爾封裝與運營總監徐健表示,Chiplet 設計可以理解為Die-interposer-Package協同設計的結果。不同于傳統的封裝設計,Chiplet的設計更為復雜,需要從系統層面定義好整體設計思路,包括架構、片內互聯方式、封裝結構和工藝等,并需要架構、電路、封裝設計和工藝團隊的緊密配合。

當然,Chiplet作為一種新的設計方式,離不開專業EDA工具的支持。芯和半導體聯合創始人代文亮博士表示,奇異摩爾本次發布的多個2.5D/3DIC產品為例,其設計正是基于芯和3DIC Chiplet 設計仿真EDA平臺,從架構探索、物理實現、分析驗證、信號完整性仿真、電源完整性仿真到最終簽核的全流程解決方案,極大地提高 了芯片設計的迭代速度,最終實現了如此出色的產品。

為實現更高密度的底層互聯,先進封裝技術也被賦予了新的、更高的期待。長電科技創新中心總經理宗華博士表示,異構集成已成為高性能計算領域的主流趨勢。2.5D/3D先進封裝技術有力的推動了高性能計算發展。長電科技目前推出了XDFO-Organic,XDFOI-Bridge,XDFOI-TSV三種先進封裝方案,其中,性價比最高的方案為XDFOI-Bridge,可以通過先進封裝技術把各種功能單元集成在一起,形成一個高性能的超異構系統,助力高性能計算未來。

奇異摩爾研發副總裁溫德鑫在發布會現場介紹了奇異摩爾的2.5D/3D design Platform。該平臺由奇異摩爾和UMC等產業鏈伙伴合作打造,全面涵蓋從系統探索、規劃,2.5D/3D 設計驗證,生產和驗證,量產管理的Chiplet方案。客戶可以基于該平臺,迅速設計、驗證、量產、加速上市時間。

奇異摩爾創始人兼CEO田陌晨表示,Scaling 已成為全行業關注的焦點。無論自然界還是人工智能,在scaling 中,個體間的交流、互聯都是促成從量變到質變的核心。

系統總算力,由算力、算力密度、互聯帶寬、IO帶寬、存儲帶寬共同決定。互聯是唯一無法通過Scaling 提升的參數。奇異摩爾作為一家專注于互聯技術的企業,致力于通過互聯技術的創新,提升互聯密度的壁壘,助力AGI 時代技術語言統一的可能性,與眾合作伙伴,共同建造AGI 時代的巴別塔。

評論