STEP-BaseBoard外設資源引腳分配說明

本節將和大家一起了解STEP-Baseboard的資源及管腳分配的明細。

本文引用地址:http://www.j9360.com/article/202311/453120.htmSTEP-Baseboard是我們針對小腳丫核心板設計的擴展板,集成了大量常見外設,同時兼容STEP-MXO2第二代和STEP-MAX10兩種小腳丫核心板,為開發者提供更多選擇。

為什么單獨將引腳分配拉出來作為單獨的一個章節呢,我們整個外設驅動后續所有章節都是只講外設驅動模塊的,在設計中往往只是作為其中的一個模塊,作為橋接系統與人機界面的模塊,很多引腳都是連接到系統的,無需分配管腳,所以就不在每個章節中談管腳分配的話題了,這里獨立一章同一說明。

引腳分配

在FPGA設計的過程中,綜合(synthesize)完成之后一定要配置FPGA的引腳到相應的外設,這樣下載FPGA程序后才能達到我們想要的效果。

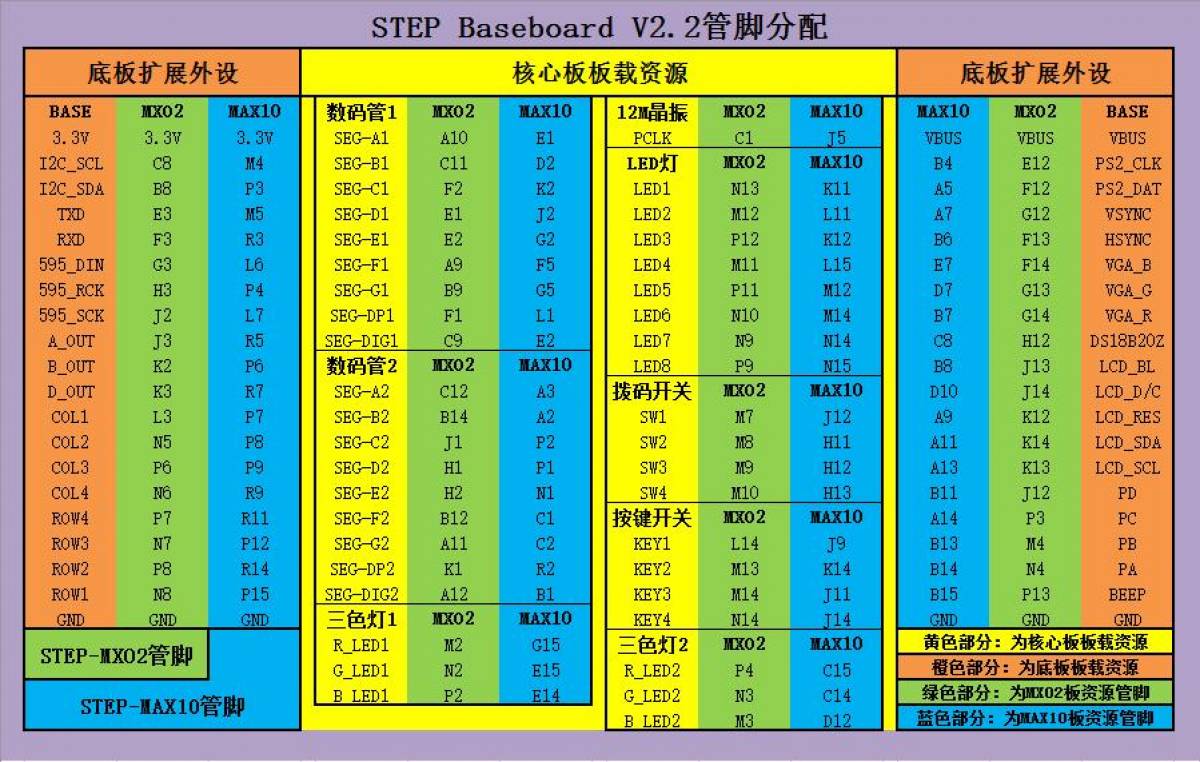

因為底板可同時兼容兩款小腳丫核心板,當使用不同的核心板時外設的管腳資源改變,為了方便快速查找各資源的管腳分配信息,我們做了下面的表格:

上圖中橙色表格中是我們底板STEP-BaseBoard集成的外設資源端口,下面為大家一一介紹:

上圖中綠色表格中是我們以上所有資源對應小腳丫核心板STEP-MXO2第二代的管腳分配信息。

上圖中藍色表格中是我們以上所有資源對應小腳丫核心板STEP-MAX10的管腳分配信息。

評論