Aurora協議的高速傳輸系統的研究與FPGA實現

基金項目:電子測量儀器技術蚌埠市技術創新中心:高性能5G增強移動寬帶通信矢量信號發生器(AHZQ3026)

本文引用地址:http://www.j9360.com/article/202307/448318.htm隨著5G 技術的不斷發展,新一代的通信技術也迎來了發展的高潮。此外,隨著智能設備的普及,對數據流量也帶來了較大的激增。5G 技術的發展對數據傳輸的實時性要求很苛刻。新一代的通信技術存在大量的研究難題,除了大帶寬、高速率以及sub6G 數據分析之外,還有微波和毫米波信號分析。5G 技術最大的挑戰就是隨著5G 高速率數據傳輸會導致信號帶寬以及基帶處理速度都將大幅度的提升,因此對高速的數據實時處理分析就變得越來越有難度[1]。

Xilinx 公司的FPGA 內部鑲嵌了Rocket IO高速串行收發器,從而能夠簡化光口傳輸的硬件電路。Aurora 協議是Xilinx 公司對外免費開放的一個高速光口傳輸協議,不僅方便了設計者自行添加上層應用,而且能夠適配大多數嵌有Rocket IO 高速串行收發器的FPGA。FPGA內部攜帶的IP 核可以提供用戶接口方便與FIFO 接口對接,其他的傳輸協議需要設計者自行設計GTP 接口的邏輯,端口的邏輯設計復雜;與此同時,Aurora IP 核在初始化時形成的Aurora 傳輸通道能夠滿足任何大小的數據幀,并且當傳輸通道被隨意打斷時,打斷空缺的地方能夠自動進行填充,從而達到滿足傳輸過來的不連續信號的要求。本文利用FPGA 自帶的Aurora 協議進行高速光口傳輸協議設計與實現,并對此方案進行測試。

1 系統架構

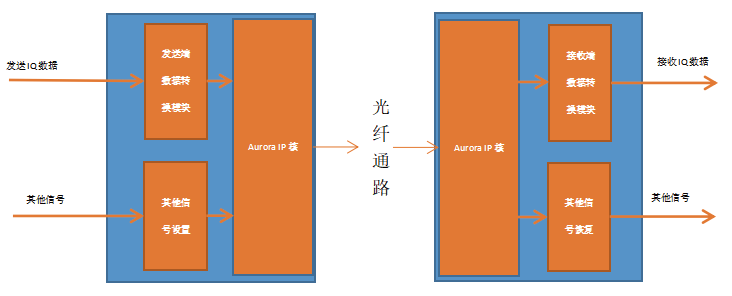

基于Aurora 協議的高速傳輸系統的結構圖如圖1所示,該系統主要是實現射頻單元與基帶處理單元之間的Aurora 協議的數據傳輸鏈路。結構圖中Aurora 傳輸協議是通過Xilinx 公司的FPGA 自帶的IP 核實現的,為了能夠滿足Aurora 協議傳輸的數據要求,設計了數據轉換模塊,此模塊主要作用是傳輸速率的匹配。在信號的發射端將采集的IQ 數據通過數據轉換模塊將數據轉換成滿足Aurora 協議傳輸的幀結構和速率;在接收端通過數據轉換模塊將Aurora 協議傳輸過來的數據恢復成規定的采樣速率的連續IQ 數據。

圖1 系統結構

2 Aurora協議

2.1 Aurora協議簡介

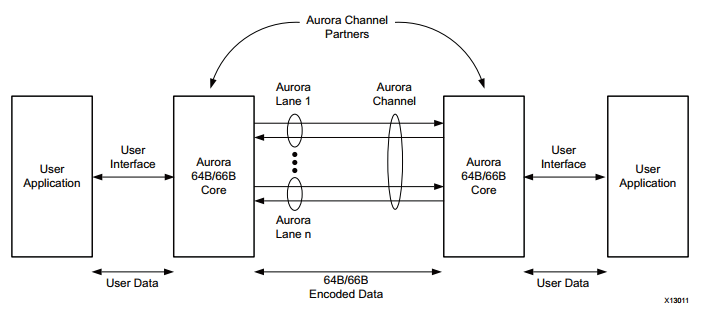

Xilinx 公司為了實現高速傳輸開發了Aurora 協議,它是一種可裁剪的輕量級鏈路層協議,實現方式是通過在相應的器件內部制定相應的IP 核。在物理層方面,它提供了透明的接口,將Rocket IO 硬核封裝到了協議的內部,通過Rocket 的并行綁定,從而能夠實現數據傳輸帶寬的完美升級。與此同時,Rocket IO 硬核不僅能進行上層自定義,還能被工業標準協議采用。Aurora協議運用的是有線連接的通信模式,協議中不僅僅是將物理層接口和數據格式都定義好了,還將時鐘校準、初始化等內容也進行了相應的定義。Aurora 協議傳輸方式包括流和幀兩種,能滿足不同用戶的使用。Aurora 協議傳輸結構圖如圖2 所示。

圖2 Aurora協議傳輸結構

Aurora 協議內部有多種不同的編碼方式,其中8B/10B 和64B/66B 兩種編碼方式最為常用。本文設計主要采用的是64B/66B 編碼方式。FPGA 內部自帶的Aurora IP 核模塊主要功能有:①通道的傳輸邏輯,主要是負責模塊的初始化、GTX 和GTH 收發器的驅動、錯誤檢測以及處理控制字符的編解碼;②提供用戶接收接口,將通道傳輸過來的數據送到用戶程序中,從而執行控制能力;③提供用戶發射接口,將用戶程序發送過來的數據傳輸到通道中,從而執行發送功能。

本設計Aurora 數據傳輸方式選擇的為流模式接口設計。該模式接口主要包括復位接口、接收數據信號接口、發送數據信號接口、接收數據信號使能接口、發送數據信號使能接口以及數據準備接口。

2.2 Aurora協議數據傳輸流程

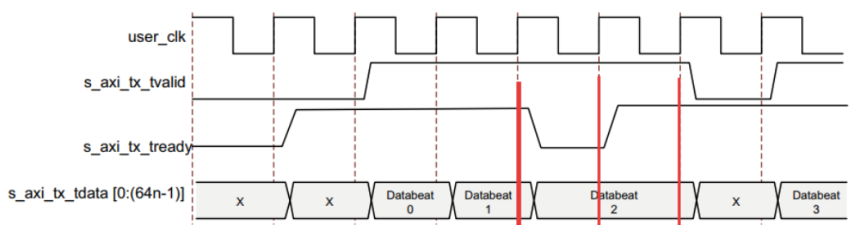

Aurora 協議數據傳輸方式選擇為Streaming 模式,在該模式中,Aurora64B/66B 通道采用流水線方式處理。此時接口的數據會傳輸到發射數據接口s_ax_tx_tdata端口,在發送數據有效位s_ax_tx_tvalid 無效時,除了數據傳輸的時鐘外,緩存的word 之間會產生間隙。當傳輸數據到達接口的接收端時,需要將數據立刻讀取,否則會造成數據丟失。

圖3 為發送數據傳輸邏輯圖,從圖中可以看出在第1 個周期時s_axi_tx_tvalid 和s_axi_tx_tready 均為0,此時表示Aurora IP 核和用戶邏輯數據傳輸均沒有準備好;等到第2 個周期時s_axi_tx_tvalid=0 和s_axi_tx_tready=1,表示Aurora IP 核已經做好了傳輸數據的準備,等待用戶邏輯傳輸數據;等到第3 個周期時s_axi_tx_tvalid=1 和s_axi_tx_tready=1,表示用戶邏輯傳輸數據,并且會將需要傳輸的數據放到了s_axi_tx_tdata總線上,此時數據會從用戶邏輯端傳輸到Aurora IP 核端;在位置1 的周期內,s_axi_tx_tready 信號被拉低,此時的數據是無效的,在位置2 的周期內s_axi_tx_tready 信號又被拉高,此時的數據是有效的;在位置1 的周期內,s_axi_tx_tready 信號被拉低,此時的數據是無效的;在位置3 的周期內s_axi_tx_tready=1 和s_axi_tx_tvalid=0,此時無數據傳輸。

圖3 Aurora協議發送數據傳輸邏輯圖

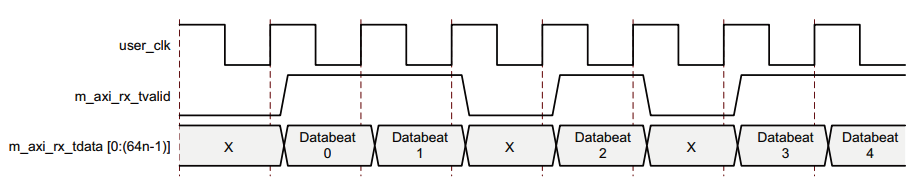

圖4 為接收數據傳輸邏輯圖,從圖中可以看出在接收數據時,只要m_axi_rx_tvalid 信號有效時,就開始接收數據,當m_axi_rx_tvalid 信號無效時,不接收信號。

圖4 Aurora協議接收數據傳輸邏輯圖

3 數據轉換設計

為了滿足5G 數據傳輸中30 kHz 和60 kHz 兩種載波間隔的基帶數據傳輸,在接收端和發射端采用了兩種采樣率即122.88 MHz 和245.76 MHz,但是AuroraIP 核使用的是245.76 MHz 固定的頻率進行數據的讀入與輸出。因此在對于122.88 MHz 采樣率的數據輸入就需要將兩個幀的數據進行緩存,然后通過一個245.76MHz 的幀時間讀出,隨之輸出一個無效的幀數據,等待下一幀數據的到來。接收端與之一樣,等到2 個122.88 MHz 的有效數據緩存之后再用245.76 MHz 的頻率輸出。

4 Aurora協議的FPGA實現及驗證

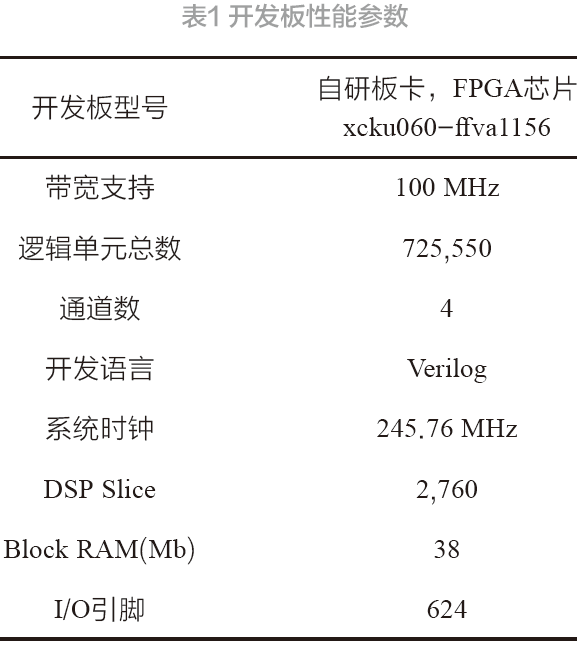

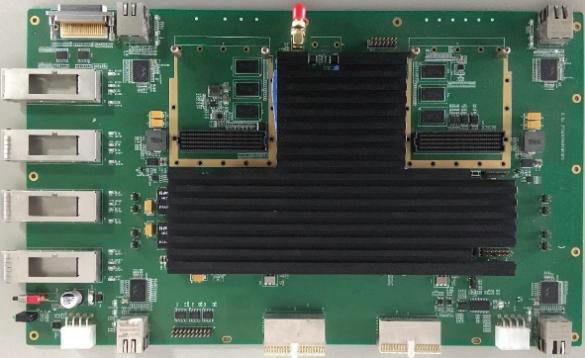

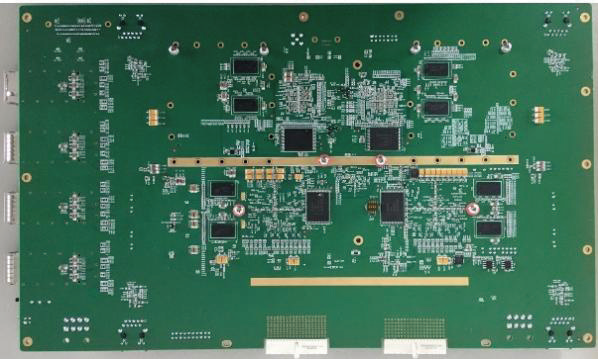

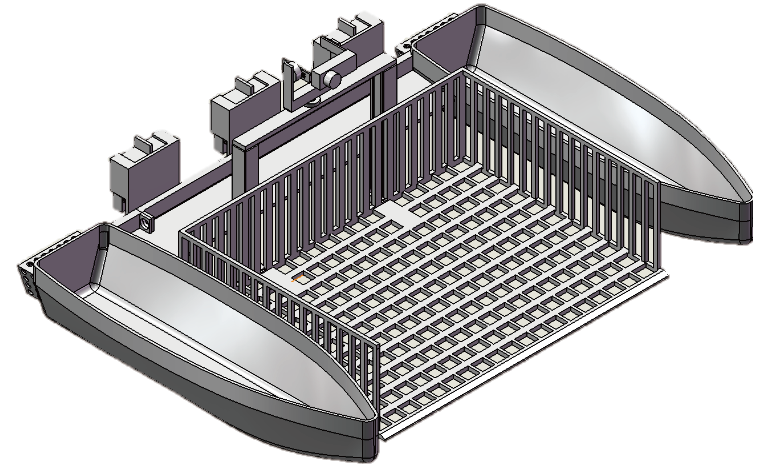

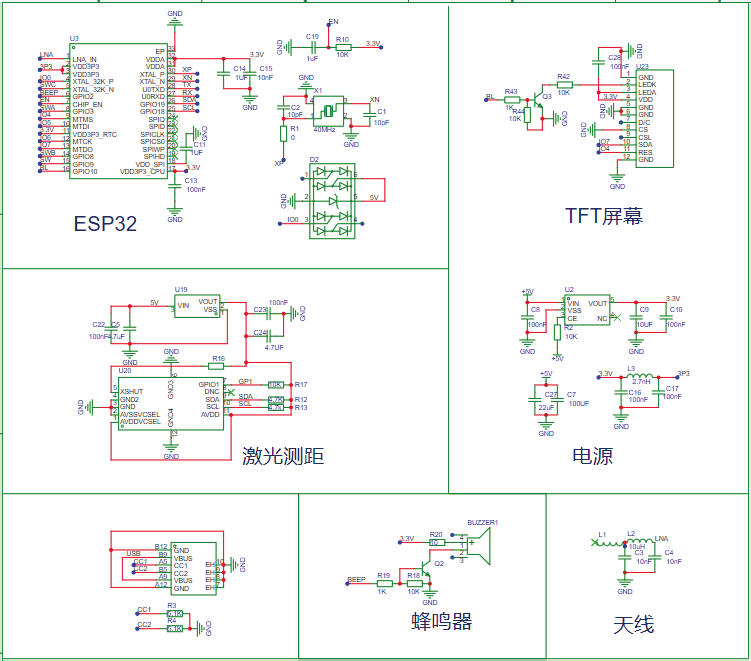

本研究將對Aurora 協議高速傳輸功能通過FPGA進行實現,并且通過硬件平臺來進行功能驗證。圖5 是FPGA 硬件開發板,首先介紹一下開發板的性能參數以及它的開發能力,開發板參數如表1 所示,開發板的硬件結構圖如圖5 所示。

圖5 FPGA開發板正反面

4.1 頂層模塊設計

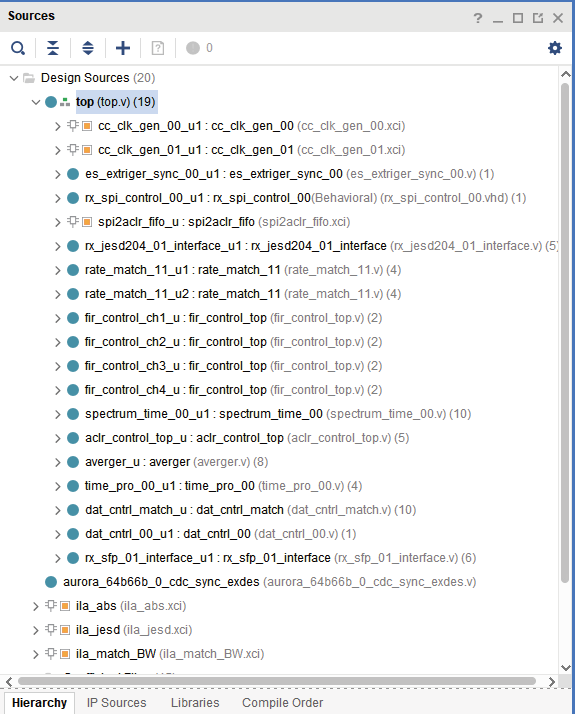

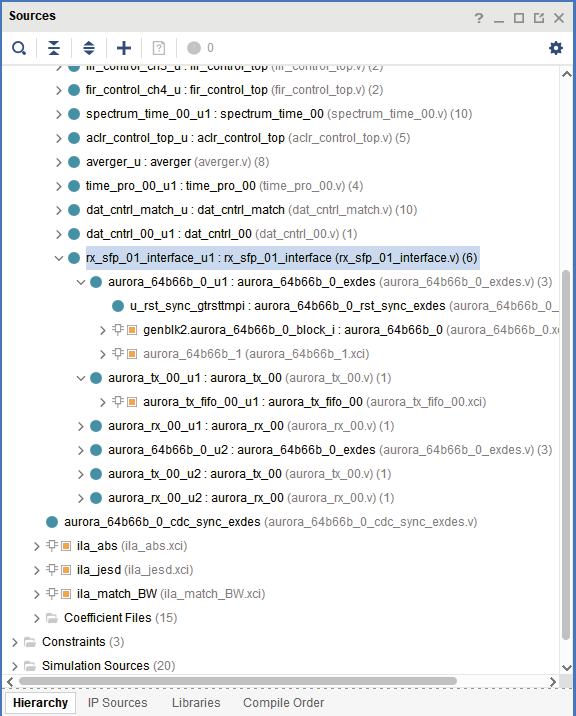

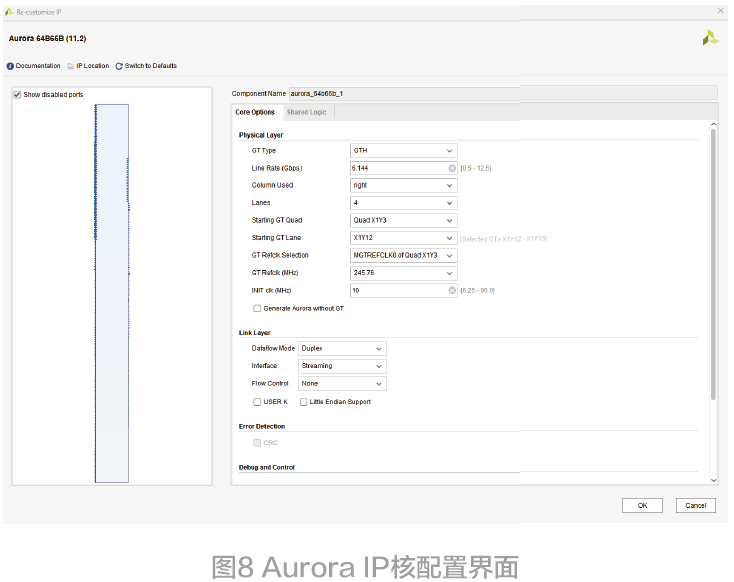

圖6和圖7給出了設計的頂層核Aurora 協議模塊的結構,Aurora IP 核設置如圖8 所示。

圖6 程序整體模塊

圖7 Aurora協議模塊

top:設計的頂層文件;

rx_jesd204_01_interface_u1:采集模塊,將采集到的射頻信號轉換成245.76 MHz 的時鐘速率;

rx_sfp_01_interface_u1:Aurora 協議實現的頂層模塊。

4.2 測試驗證

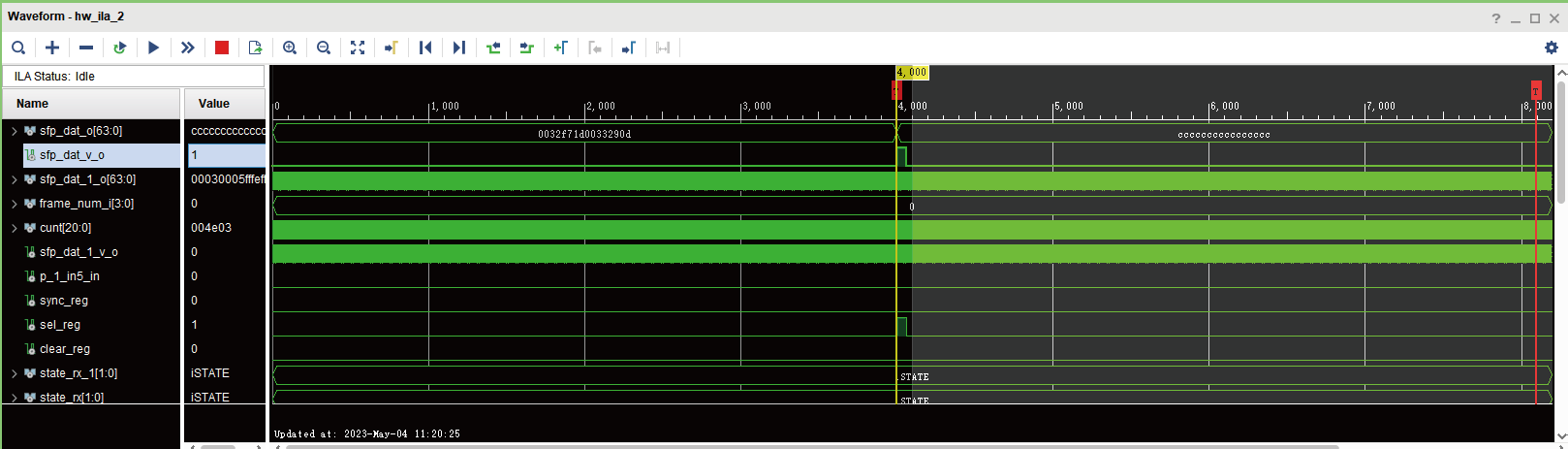

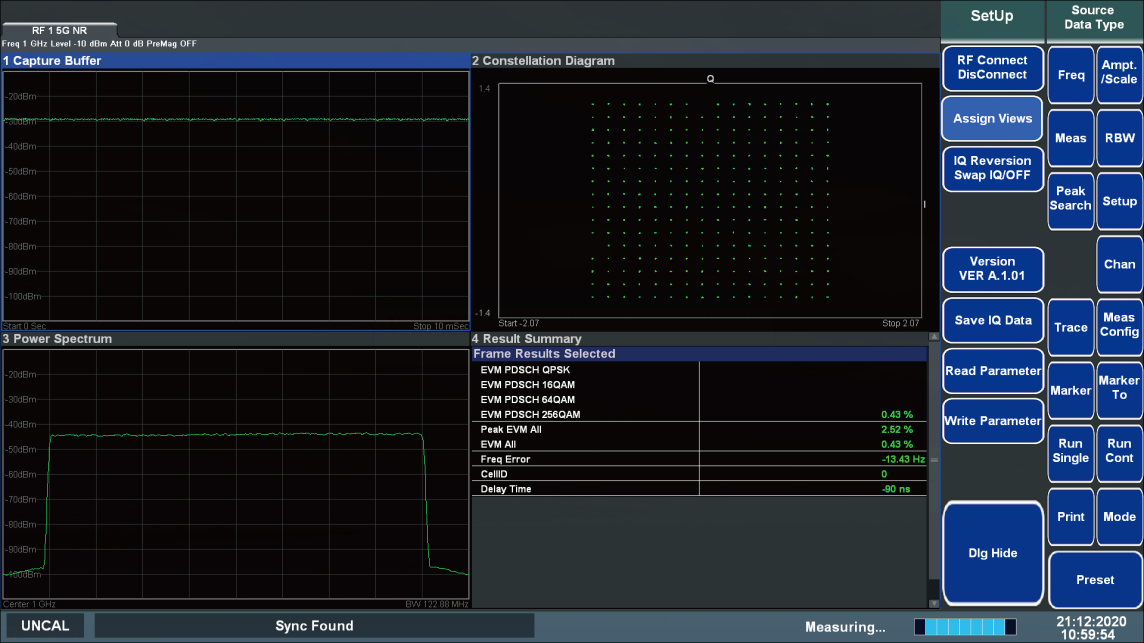

本設計采用Vivado2018.3 軟件進行代碼編寫、編譯及上板驗證,該開發軟件內部集成了大量的RAM、乘法器以及FIFO 等常用的IP 核,從而能夠大大降低了功能的開發難度。數據速率轉換模塊是將外部的異步速率的信號轉換成Aurora 核數據時鐘的信號。采用Xilinx ku060開發板進行功能仿真驗證,使用的FPGA芯片型號為xcku060-ff va1156。通過ILA 監測器來觀察Aurora協議信號傳輸功能是否正常。最后通過DSP 識別CCCC_CCCC 數據頭將IQ 數據傳輸給算法庫進行解調,軟件將解調結果顯示出來。測試結果如圖9 和圖10 所示。

圖9 FPGA捕捉到CCCC_CCCC數據頭

圖10 IQ數據解調結果

5 結束語

本研究主要完成了Aurora 協議高速傳輸系統研究和FPGA 實現驗證。為了實現射頻RF 單元和基帶BU單元之間的Aurora 協議的數據鏈路,需要將發送和接收的數據格式匹配到Aurora 協議的數據格式。數據傳輸的速率匹配難點主要在于高速處理硬件的實現。為了匹配不同采樣率的數據Aurora 傳輸,設計了數據轉換模塊。經過在Xilinx ku060 開發板測試,驗證了Aurora協議高速數據傳輸的正確性,確定了本實現方案的可行性。

參考文獻:

[1] 周代衛,王正也,周宇,等. 5G終端業務發展趨勢及技術挑戰[J].電信網技術, 2015,3:64-79.

[2] 焦志超. 一種基于Aurora協議的多通道數據傳輸系統設計[J].電子世界,2021,620(14):188-189.

[3] 袁行猛, 徐蘭天.基于FPGA的高速光纖通信基帶板的設計[J].電子產品世界,2018,25(7):8-61.

[4] 李維明, 陳建軍, 陳星锜. 基于Aurora協議的高速通信技術的研究[J].電子技術應用,2013,39(12):37-40.

[5] 祁永鑫. 基于Aurora協議的多通道高速可配置數據采集系統設計[D].荊州:長江大學,2022.

(本文來源于《電子產品世界》雜志2023年6月期)

評論