利用VectorBlox開發工具包在PolarFire FPGA實現人工智能

隨著人工智能、機器學習技術和物聯網的興起,人工智能的應用開始逐漸轉移到收集數據的邊緣裝置。為縮小體積、減少產熱、提高計算性能,這些邊緣應用需要節能型的解決方案。Microchip的智能嵌入式視覺解決方案,致力于讓軟件開發人員可以更方便地在PolarFire?現場可編程門陣列(FPGA)內執行人工智能的模型,進而滿足邊緣應用對節能型推理功能日益增長的需求。作為Microchip嵌入式解決方案組合的重要新成員,VectorBlox?加速器軟件開發工具包(SDK)可幫助軟件開發人員在不學習FPGA工具流程的前提下,利用Microchip PolarFire FPGA創建靈活的低功耗神經網絡應用。

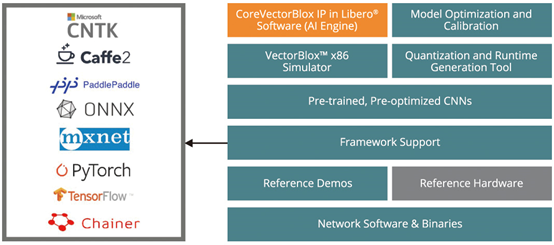

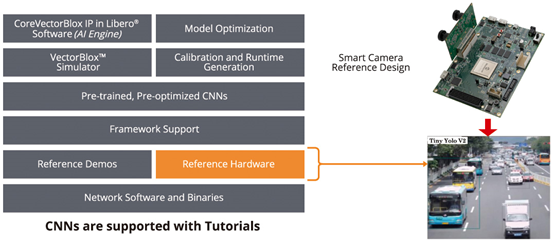

VectorBlox軟件支持以下幾個特性:

1.基于OpenVINO?工具包的前端工具;

2.支持最常見的框架,如TensorFlow、Caffe、MxNet、PyTorch和DarkNet;

3.無需預先了解FPGA即可快速評估;

4.基于軟件覆蓋的實現;更新CNN時無需重新編程FPGA。

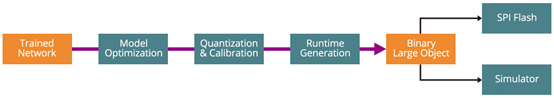

VectorBlox Accelerator SDK包含不同的工具,可將來自TensorFlow和ONNX等框架的神經網絡描述編譯成二進制大型對象(BLOB)。這些BLOB存儲在閃存中,并在執行期間加載到 DDR 內存中。

主要幾個工具如下:

1.模型優化:將經過訓練的網絡轉換為通用的中間語言(IR),并通過刪除訓練期間使用的多個層以及優化網絡以進行推理;

2.量化:將優化的網絡從 FP32 轉換為 INT8,并使網絡能夠使用更少的內存來表示,同時將精度損失降至最低;

3.校準:調整以INT8精度表示的模型的激活函數和權重;

4.運行時生成:創建寫入嵌入式非易失性存儲(例如 SPI 閃存)的BLOB。

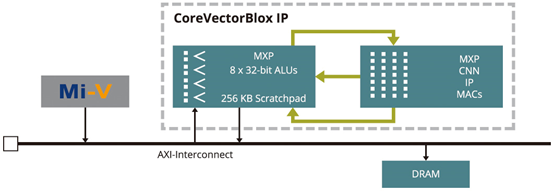

CoreVectorBlox IP是包含在SDK里面的硬件加速器,CoreVectorBlox IP由矩陣處理器(MXP)和MXP CNN IP組成。當需要共享神經網絡工作負載時,它可以實例化為單核加速器或多核加速器。MXP由八個32位算術/邏輯單元(ALU)組成,負責按元素張量運算,如加、減、異或、移位、乘法、內積等。MXP CNN IP由乘法和累加的二維數組組成,IP使用FPGA內部的數學塊來實現功能。顧名思義,MXP CNN IP負責執行CNN的卷積層。多個網絡可以在運行時迭加并動態切換。

開發設計流程可以簡單的分成三個步驟:

步驟1:準備訓練好的模型

使用SDK中提供的Python腳本將經過訓練的模型轉換為優化的INT8表示形式,稱為BLOB。通過VectorBlox Accelerator Simulator運行BLOB,以驗證網絡的準確性并確保網絡的成功轉換。

步驟2:準備硬件

PolarFire FPGA視頻套件配置為作為支持AI的智能相機運行。SDK包括一個預編譯的套件刻錄檔。使用套件中包含的FlashPro編程器將刻錄檔寫入PolarFire FPGA并將第1步生成的BLOB寫入套件的SPI閃存。

步驟3:編寫您的嵌入式代碼

在基于C/C++的SoftConsole IDE中使用提供的嵌入式代碼并生成和編程hex文件。將視頻套件連接到HDMI顯示器并將其打開。修改嵌入式代碼以加載和運行多個CNN BLOB、實時動態切換CNN或按順序加載CNN以進行同時推理。

部署選項:

PolarFire FPGA視頻套件(MPF300-VIDEO-KIT-NS)支持VectorBlox SDK。

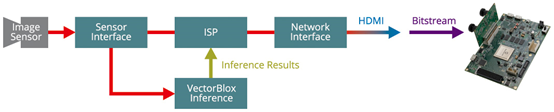

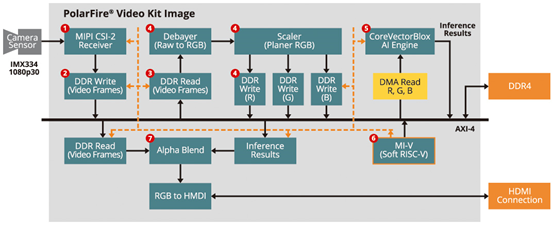

VectorBlox智能相機參考設計流程:

1.通過MIPI CSI-2接收影像;

2.影像存儲在DDR4內存中;

3.推理之前,影像從DDR4讀回;

4.影像從RAW轉換為RGB并寫回DDR4;

5.CoreVectorBlox引擎對R、G、B數組運行推理并將結果寫回內存;

6.Mi-V(軟RISC-V?)生態系統對概率進行排序并創建帶有邊界框的覆蓋框架,并將結果放入 DDR4;

7.讀取原始影像并與迭加幀進行 alpha 混合,然后發送到 HDMI 顯示器。

本文作者為:Microchip高級應用工程師 張長軒

評論