555定時器數字秒表電路

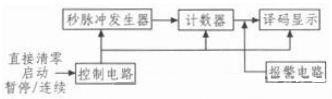

本文介紹了一個數字秒表電路的原理、設計和操作。數字秒表可以是一個顯示以分、時、秒為單位的實際時間的電路,也可以是一個顯示時鐘脈沖數的電路。這里我們設計的是第二種類型,其中電路顯示從0到59的計數,代表60秒的時間間隔。換句話說,這里的電路只顯示秒數的時間。這是一個簡單的電路,包括一個555定時器來產生時鐘脈沖和兩個計數器IC來進行計數操作。

本文引用地址:http://www.j9360.com/article/202305/446450.htm數字秒表電路原理:

這個電路是基于同步級聯的2級計數器工作原理。其想法是顯示時鐘脈沖從0到59的計數,代表60秒的時間間隔。這是通過使用一個以星形模式連接的555定時器IC來產生每個間隔為1秒的時鐘脈沖來實現的。當第一個計數器從0到9計數時,第二個計數器在第一個計數器的計數值達到9時開始計數操作。計數器IC以級聯的形式連接,每個計數器的輸出連接到BCD-7段解碼器,用于驅動7段顯示器。

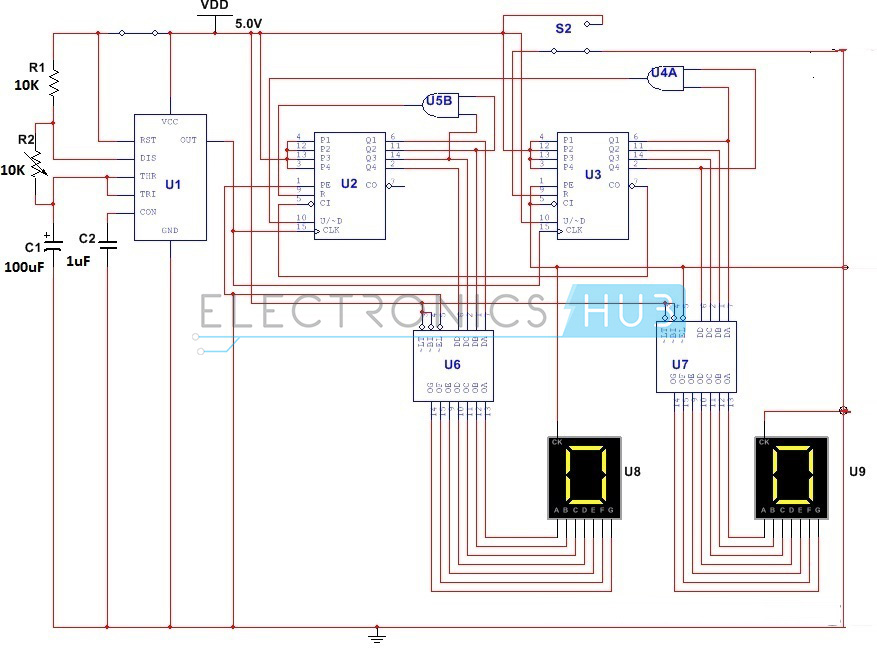

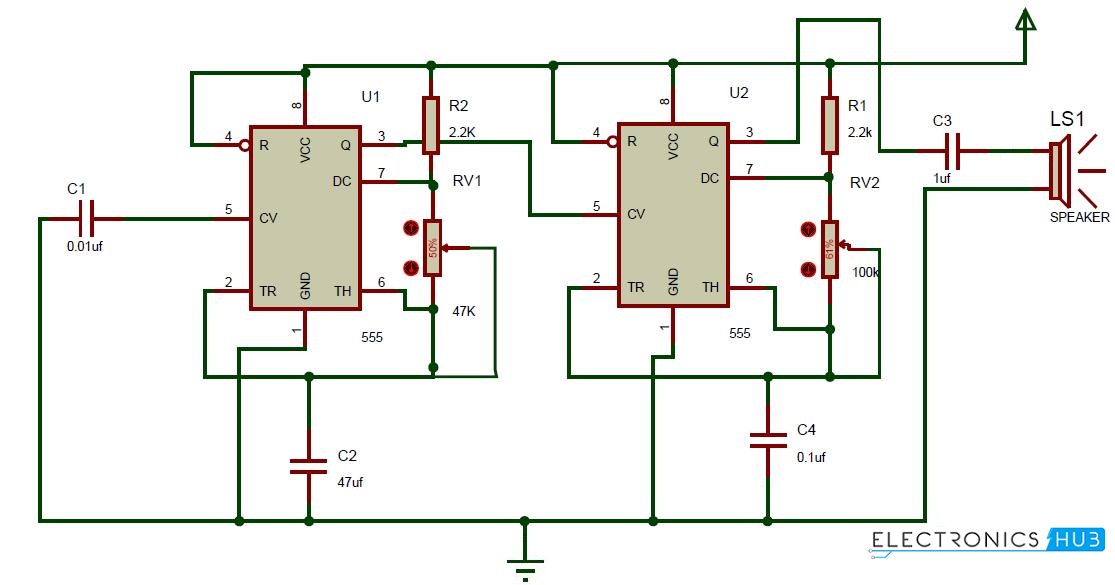

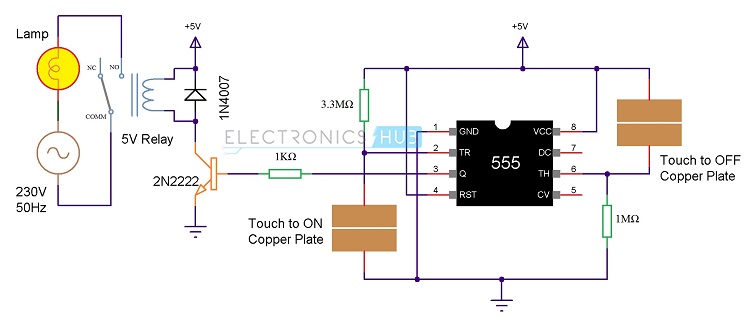

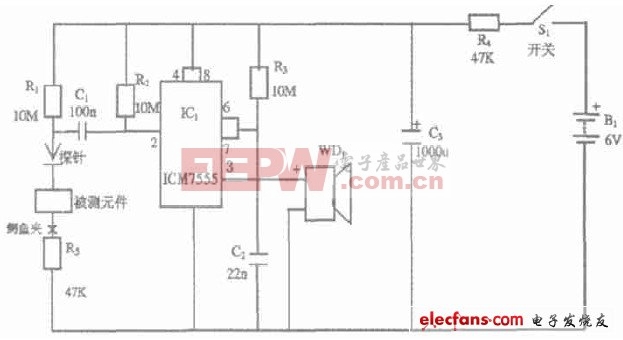

數字秒表電路圖:

數字停表的電路圖

數字秒表電路設計:

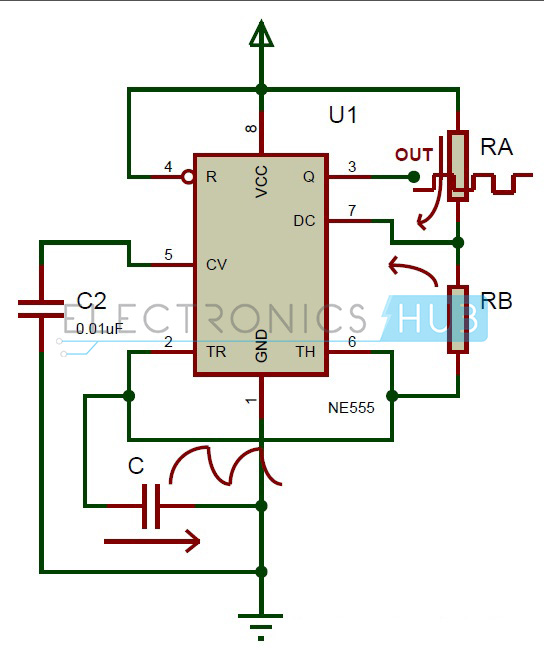

設計的第一部分涉及到設計555定時器的星形多諧振蕩器安排。這里需要的時間周期是1秒。輸出信號的頻率由f = 1.44/ (Ra+Rb) C給出,我們可以計算出C的值,假設Ra和Rb的值約為10K。這里我們得到一個100uF的電解質電容。

設計的第二部分涉及到將兩個計數器IC-4510以同步級聯的方式連接起來。這是通過將計數器IC的時鐘引腳連接到555定時器的輸出來實現的,從而形成平行的時鐘輸入信號。其中一個IC的輸出引腳被連接到另一個IC的輸入引腳。

由于我們關心的是,一旦第一個計數器達到9的計數值,就啟動第二個計數器,我們通過設計一個簡單的組合邏輯電路來實現。回顧一下計數器的真值表,對于一個9的時鐘脈沖計數,相應的二進制計數或計數器輸出信號的狀態是1001。換句話說,當計數為9時,Q1和Q4處于高邏輯信號。在這里我們使用一個AND門IC 7408,它的輸入連接到第一個計數器的Q1和Q4引腳,輸出連接到第二個計數器的U/D引腳。

在這里,我們的要求是顯示時鐘脈沖,直到數到60。這可以通過確保第二個計數器在計數達到5的時候復位來實現。我們通過設計一個簡單的邏輯電路來實現,該電路由另一個AND門IC組成,其輸入端連接到第二個計數器的Q3和Q2引腳。

第三部分是設計顯示電路。這是通過將每個計數器IC的輸出連接到BCD到7段解碼器的輸入來完成的。每個解碼器ICs 4511的輸出被連接到7段顯示器。

數字秒表電路的工作:

一旦常開開關轉到關閉位置,電路就開始工作。定時器555以頻繁的間隔產生高低信號,從而產生振蕩信號,其頻率是基于兩個電阻和充電電容的值。換句話說,定時器555集成電路產生所需時間周期的時鐘脈沖。這個時鐘信號被送入兩級排列的BCD計數器CD4510。CD4510由四個同步時鐘的D-觸發器組成,它們被連接在一起以實現計數操作。時鐘脈沖由兩級同步級聯排列的兩個CD4510計數器進行計數。當集成電路U3收到時鐘脈沖時,它開始從0到9計數。一旦計數達到9,AND門IC U4A產生一個高邏輯輸出,該輸出被送入IC U2的U/D引腳。IC U2開始進行計數操作。IC U2繼續其計數操作,每當U3達到其結束計數時,IC U3也繼續計數。然而,一旦IC U2的計數達到6,復位引腳被AND門U5B設置為高電平。該計數顯示在由BCD到7段解碼器CD4511驅動的7段顯示器上。因此,該電路顯示從0到60的時鐘脈沖。

數字秒表的應用:

這個電路可以作為問答比賽的指示器使用。

數字秒表的局限性:

該電路不顯示實際時間,而是顯示時鐘脈沖的計數。

由于傳播延遲,使用數字計數器IC在整個操作過程中會產生一個時間延遲。

這是一個理論上的電路,可能需要修改。

評論