ESD簡介(簡單明了!)

記得小學時候的自然課上老師用冬天脫毛衣時的火花向年少的我們描述靜電的情形,那時候不禁對大自然肅然起敬。沒想到很多年之后學習集成電路課程,又一次跟靜電有了接觸,只是這一次沒有年少時的輕松與愉悅。

本文引用地址:http://www.j9360.com/article/202210/438849.htm靜電放電(Electrostatic Discharge, ESD)很容易造成電子元件或電子系統遭受過度電應力而被永久破壞。靜電放電破壞的產生,大多數是由于人為因素造成的,但又很難避免。

在芯片制造、生產、測試、搬運等過程中,靜電會積累在人體、儀器、設備之中,甚至芯片本身也會積累靜電,這些靜電一旦在某些情況下形放電通路,那么芯片便有可能遭受高壓、大電流的靜電放電損害。

摩擦帶來的靜電

上下、左右滑動可以查看更多內容哦!

如何才能避免靜電放電的危害?一方面需要加強工作場所對靜電積累的控制,另一方面必須加強集成電路本身對靜電放電的耐受能力,于是ESD保護設計成為所有芯片設計時必須考慮的一部分。

ESD保護的基本認識

當兩個帶有相反電荷的物體相接觸時就會發生放電的現象,而且這種現象在芯片使用和生產中隨處可見。

比如摩擦、離子注入等過程中很容易造成芯片中的靜電積累,當積累有電荷的芯片與人體、機械導體、其它芯片接觸時,就有可能發生靜電放。

這個過程可能持續幾納秒到幾百納秒,放電電壓可能高達幾百伏甚至上千伏,放電電流可能高達數安培甚至數十安培,芯片內的器件在這樣高壓、大電流的作用下會發生不可逆的破壞,這是需要設計ESD保護電路的根本原因。

在目前CMOS集成電路設計中,工藝節點普遍進入到亞微米階段,器件特征尺寸不斷縮小、柵氧厚度不斷減小、電路速度要求越來越高,為了滿足電路性能要求以及克服一些由于特征尺寸減小帶來的消極問題,工藝也不斷地得到改進。

LDD(Lightly Doped Drain,LDD)工藝:為了克服熱載子(Hot-Carrier)注入效應發展出了LDD工藝與結構。

Silicide工藝:為了降低CMOS器件漏極(drain)與源極(source)的寄生電阻(sheet resistance)Rs與Rd, 發展出了Silicide工藝。

Polycide工藝:為了降低CMOS器件柵級的寄生電阻Rg,發展出了Polycide工藝。

Salicide工藝:在更先進的工藝中把Silicide與Polycide一起制造,發展出了所謂的Salicide工藝。

在先進工藝中更薄的柵氧厚度、更淺的結深以及小的柵、源、漏電阻,使得器件更容易被ESD損壞。

ESD失效至少由以下三個原因之一導致:器件局部過熱、高電流密度、高電場強度。而且三者之間有一定聯系,電流密度過大很容易導致器件結溫升高,進而導致器件損壞。

ESD對器件的損壞程度也有一些區別,有可能導致器件直接失效,芯片功能喪失,也有可能導致器件基本功能保留但是漏電增加的情況,不論哪一種情況都是ESD失效的表現。

ESD保護能力是一個"短板"問題,芯片的ESD耐受能力是由所有ESD保護電路中表現最差的來決定,所以ESD保護電路設計中一定要考慮提高所有保護電路的抗ESD能力,而不是單單提高某些引腳的抗ESD能力。

ESD保護電路是集成電路中專門用來抗ESD的電路,可以為ESD電流提供放電通路,以免發生ESD時靜電電流進入IC內部而造成器件損傷。

ESD的模型分類

目前根據ESD 產生的原因及其對集成電路放電的方式不同,常見的ESD 被分類為下列三類(還有一些模式并不常用),分別是:人體放電模式(HBM, Human Body Model), 機器放電模式(MM, Machine Model)以及元件充電模式(CDM, Charge Device Model).

在業界2000V的人體放電模式、200V的機器放電模式以及500V的原件充電模式是芯片ESD耐壓的標準之一,當然不排除一些特殊用途的場合會有更高的ESD耐壓要求。

人體放電模式(HBM, Human Body Model):是指因人體通過磨擦或其他因素積累了靜電,此時當人去碰觸IC時,人體上的靜電便會經由IC的PIN腳進入IC內,再經由IC放電到地。

有關于HBM的ESD已有工業測試的標準,用來判斷IC的ESD可靠程度。上圖中顯示的是HBM的等效電路圖,其中人體的等效電容定為100pF, 人體的等效電阻定為1.5kΩ, 對人體放電模式的更多測試規范可以參考工業標準。

HBM的電流波形如上圖中所示,對于2kV的 HBM ESD電壓,通常電流峰值在1.2A-1.48A左右,電流上升時間在數ns,電流持續時間在130ns-170ns之間,這些又會受到環境濕度、溫度、不同人群等因素的影響。

機器放電模式(MM, Machine Model):是指機器(例如機械手臂)本身積累了靜電,當此機器碰觸IC時,該靜電便經由IC的PIN腳放電。此放電的過程時間更短,電流更大。

因為大多數機器都是用金屬制造的,所以機器放電模式中的等效電阻為0Ω,等效電容定為200pF,并且相比于HBM, 等效電路中多出了一個電感。

由于機器放電模式的等效電阻為0,故其放電的過程更短,在幾ns到幾十ns的時間內會有數安培的放電電流產生。

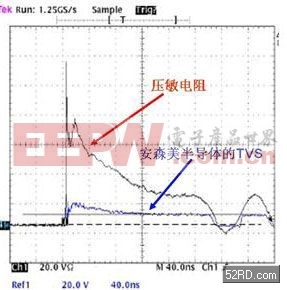

上圖中展示的是有關2kV HBM 與 200V MM的放電電流比較,可以看到雖然HBM的電壓比MM的電壓高很多,但是MM的放電電流卻比HBM的放電電流大很多,因此MM ESD放電對IC的破壞力更大。圖中放電電流波形振動的情形,是因為測試機臺導線的雜散電感與電容引起的。

元件充電模式(CDM, Charge Device Model):是指IC先因磨擦或其他因素而在IC內部積累了靜電,但在靜電積累的過程中IC并未受到損傷。這種帶有靜電的IC在處理過程中,當其PIN腳碰觸到接地面時,IC內部的靜電便會經由PIN腳自IC內部形成放電,此種模式的放電時間可能只在幾ns內。

因為IC內部積累的靜電會隨著IC本身對地的等效電容而變,而且IC擺放的角度與位置以及IC所用的包裝型式等都會造成不同的等效電容,多種因素難以確定,因此,有關CDM放電的現象更難被真實地模擬。

CDM ESD放電時間更短、電流峰值更高,導致器件承受的ESD應力更大,相比于前兩種模式,CDM更容易導致IC損壞。

ESD的測試

靜電的積累可能是正的或負的電荷,因此靜電放電測試對同一PIN腳而言是具有正、負兩種極性。

對于每一個I/O PIN而言,進行ESD測試時,有下列四種組合:

PS mode:VSS引腳接地,正的ESD電壓出現在I/O PIN并對VSS腳放電,此時VDD與其它PIN腳浮空。

NS mode:VSS引腳接地,負的ESD電壓出現在I/O PIN并對VSS腳放電,此時VDD與其它PIN腳浮空。

PD mode:VDD引腳接地,正的ESD電壓出現在I/O PIN并對VDD腳放電,此時VSS與其它PIN腳浮空。

ND mode:VDD引腳接地,負的ESD電壓出現在I/O PIN并對VDD腳放電,此時VSS與其它PIN腳浮空。

上面是針對I/O PIN與電源和地之間發生ESD的情形,等效原理圖如下所示。

ESD也可能發生在任意的I/O引腳之間,若兩只PIN腳之間無直接的相關電路,靜電放電電流會先經由某部分的電路到VDD或VSS電源線上,再由VDD或 VSS電源線到另一引腳流出IC。

上述的情況在實際測試中會很復雜,導致測試工作量的增大,下圖中給出了改進的Pin-to-Pin測試方法,情形與上述基本類似,只是正、負ESD電壓放電發生在一個I/O引腳與其他I/O引腳之間,測試這種情況時電源和地浮空。

ESD也可能發生在電源和地的引腳上,這種情況測試時也分正、負兩種情況,測試時只在電源和地之間加測試信號,其余引腳浮空。

以上是ESD測試時常用的測試電路等效電路圖,對于有些模擬信號引腳的測試也參考上面的方法分別進行。

ESD失效判斷:IC進行ESD測試之后,要判斷其是否已被ESD破壞,以便決定是否進一步測試,但是如何判定該IC已被ESD損壞了呢?常用的有下述三種方法:

絕對漏電流:當IC進行ESD測試后,在其 I/O PIN上加一定電壓,漏電電流超過規定值,即可認為ESD失效。

相對I-V漂移:當IC進行ESD測試后,其 I/O PIN的I-V曲線漂移超過規定值,即可認為ESD失效。

功能判斷:當IC進行ESD測試后,其 I/O PIN的功能已經不滿足性能規格,即可認為ESD失效。

需要注意的是:即使是對同一IC而言,不同的ESD失效判斷標準,可能會得到差距較大的ESD失效電壓,因此ESD失效電壓要在一定的故障判定準則下才有意義。

關于ESD測試的內容做以上簡單介紹,更具體的ESD測試操作方法有興趣的同學可以查閱ESD設計相關文獻。

ESD保護電路中器件的使用

在集成電路設計中加入ESD保護電路,當ESD來的時候,ESD保護電路發揮保護效果,避免集成電路內的元件被ESD損傷。

當ESD電壓出現在芯片PIN腳上時,位于該PIN腳附近的ESD保護電路必須及早地導通來泄放ESD電流。因此,ESD保護電路所使用的元件必須要具有較低的擊穿電壓或較快的導通速度,同時也需要注意在芯片正常工作時ESD保護電路不能影響芯片功能。

在CMOS集成電路中,可用來做ESD保護的元件如下列所示:

電阻(Diffusion or poly resistor)

二極管(P-N junction)

金屬-氧化物-半導體晶體管(NMOS or PMOS)

厚氧化層元件(Field-oxide device)

寄生的雙極型晶體管(BJT)

寄生的可控硅元件(SCR device)

以上器件或單一使用實現ESD保護功能,或與其他器件組合使用實現ESD保護功能,在設計電路時可以根據代工廠給出的ESD設計指導手冊進行ESD保護電路設計或者根據經驗選擇合適的ESD器件。

全芯片的ESD保護電路

以上已經了解到ESD會發生在I/O PIN與電源和地之間,也會發生在不同的I/O PIN之間,也可能出現在電源和地之間,因此對于ESD保護電路的設計需要考慮所有可能發生ESD的情形。

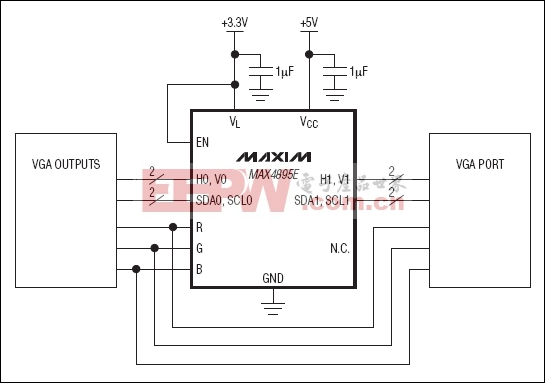

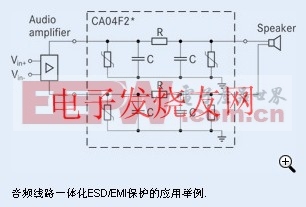

全方面的ESD保護電路設計必須考慮所有可能發生ESD的情況,上圖中給出了芯片中一個全面的ESD保護設計的內容,對于電源分布更復雜的混合信號芯片來說,ESD保護電路設計還需要考慮不同電源域之間的ESD情形,電路設計和電源布局會更復雜。

上圖中包含I/O PIN的ESD保護電路以及電源和地之間的ESD Clamp電路,具體的電路原理和電路結構在下一次的內容中與PAD一起講,ESD保護電路的設計是一個包含器件、電路、系統的全方面考慮,不僅需要扎實的理論基礎,也需要大量的經驗積累。本次小目主要向大家做一次簡單的ESD內容科普,配合完成模擬集成電路設計中的全部流程。

評論