IBIS建模--第3部分:如何通過基準測量實現質量等級為3級的IBIS模型

輸入/輸出緩沖器信息規范(IBIS)是一種行為模型,作為生成器件模型的標準格式而在全球受到歡迎。器件模型的精度取決于行業提供的IBIS模型的質量。因此,為信號完整性仿真提供高質量、可靠的IBIS模型是對客戶的堅定承諾。

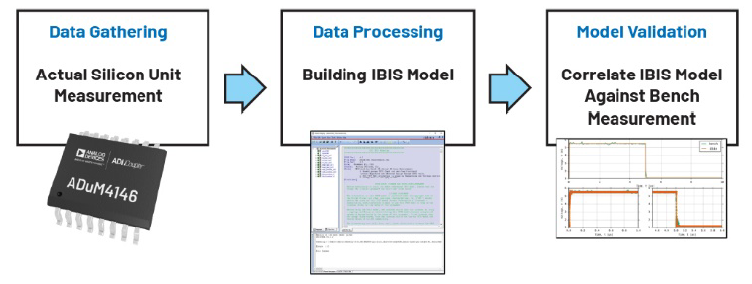

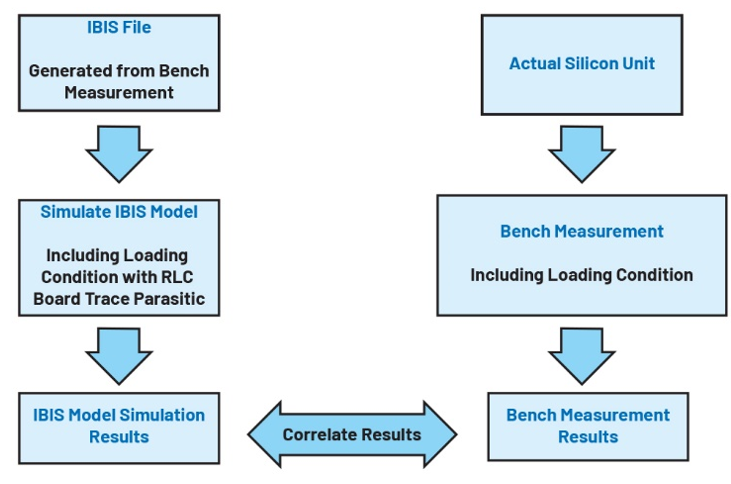

生成IBIS模型的一種方法是通過仿真,但在某些情況下,設計文件不可用,因而無法從仿真結果生成IBIS模型。在這種情況下,通過基準測量生成IBIS模型是解決這一問題的方法,它能提供高質量和更真實的器件行為模型。圖1顯示了通過基準測量生成IBIS模型的完整過程。使用實際芯片,提取器件的接收器和驅動器緩沖器行為以表示電流與電壓(I-V)數據和電壓與時間(V-t)數據。

然后使用實際試驗臺設置在完整負載條件下驗證模型。此程序提供質量等級2b的IBIS模型。為了實現更高質量等級(3級)的模型,生成的IBIS模型還將針對器件的晶體管級設計進行驗證,同樣采用推薦的負載條件。

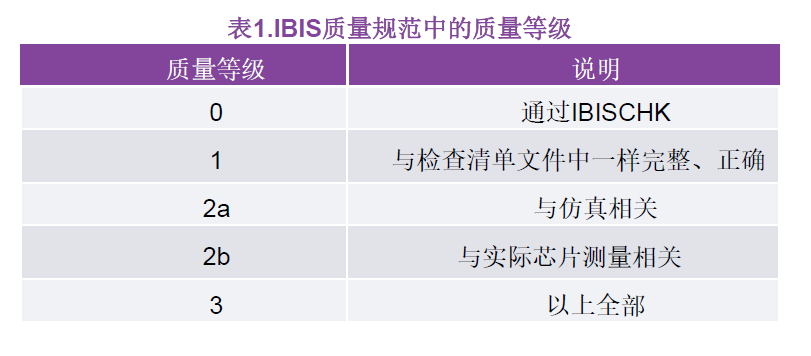

為了表征質量,IBIS質量任務組制定了一種包含五個QC(質量控制)階段的質量控制流程。表1為定義不同質量等級的清單。

表1中列出的質量等級提供了IBIS模型質量標準,該標準因供應商而異。制定IBIS模型精度標準將能確保客戶獲得準確可靠的模型。模型的質量等級越高,其數據就越準確,因為更高的質量等級需要更多的驗證。

根據《半導體建模:用于信號、電源和電磁完整性仿真》一書(Roy Leventhal和Lynne Green撰寫),IBIS正確性檢查清單有5個公認的質量等級。

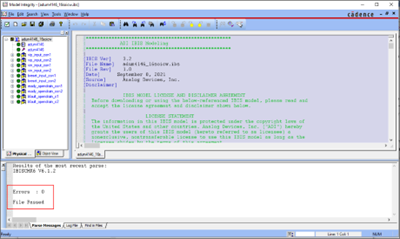

質量等級0—通過IBISCHK

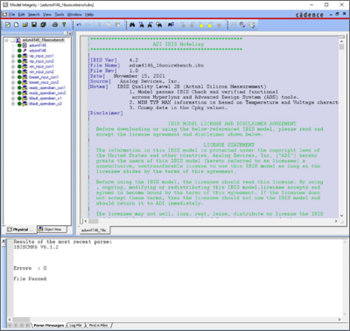

質量等級0要求至少應通過IBIS解析器檢查。IBISCHK必須產生零錯誤;如果無法消除所有警告,則必須對其進行解釋。理想情況下,不應有任何警告,但人們認識到,有些警告是無法消除的。解析器檢查產生的“錯誤”、“警告”和“注意”消息可作為IBIS模型制作商識別錯誤并輕松糾正錯誤的指南。IBIS模型解析器檢查參見圖2。

圖2.IBIS模型通過IBISCHK

質量等級1—達到檢查清單文件中規定的完整性和正確性

質量等級1的IBIS模型不僅要通過質量等級0檢查,還要通過基本仿真測試的正確性和完整性檢查。封裝寄生參數、引腳配置和負載參數應正確定義。斜坡速率和典型值/最小值/最大值必須符合器件規格。另外,可以參考這里列出的質量等級1下的詳細要求。

質量等級2a—與仿真相關

質量等級2a將IBIS模型的性能與器件的晶體管級設計進行比較。連接到負載時的IBIS模型性能與相同負載下器件的晶體管級設計進行相關處理。然后比較兩個仿真設置的結果,并檢查模型是否達到了質量等級2a。細節將在“驗證和結果”部分討論。

質量等級2b—與實際芯片測量相關

質量等級2b將IBIS模型的性能與器件的實際單元進行比較。與質量等級2a一樣,在相關期間必須將相同的負載連接到兩個設置。根據相關結果判斷模型是否達到質量等級2b。細節將在“驗證和結果”部分討論。

質量等級3—晶體管級仿真與IBIS基準測量的相關

質量等級3要求根據晶體管級設計和實際單元驗證IBIS模型。要使模型達到質量等級3,它必須通過質量等級2a和2b的相關性檢查。此外,模型必須通過IBIS解析器測試(質量等級0),并通過IBIS質量檢查清單的檢查(質量等級1)。細節將在“驗證和結果”部分討論。

應用案例

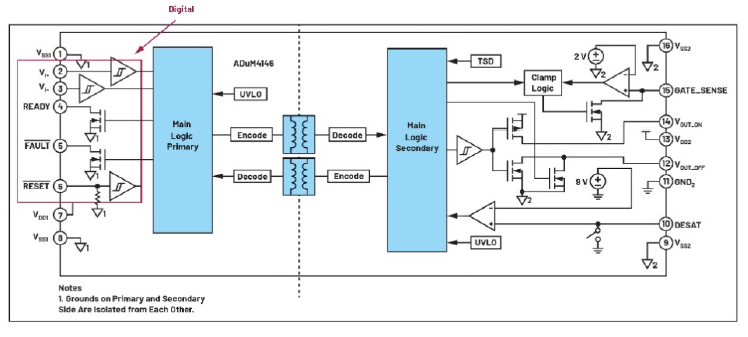

本文研究的案例是ADuM4146,它是一款專門為驅動碳化硅(SiC) MOSFET而優化的隔離式柵極驅動器。ADuM4146有三個輸入引腳(VIP、VIN和RESET)和兩個開漏引腳(READY和FAULT),但本文針對每種緩沖器類型僅討論一個引腳。這是因為,對于緩沖器類型相似的引腳,構建和驗證IBIS模型的過程是相同的。VIP引腳將作為輸入緩沖器的用例,FAULT將作為開漏緩沖器的用例。

需要注意的是,盡管相似的緩沖器類型具有相同的IBIS建模和驗證過程,但這并不一定意味著它們具有相同的IBIS數據。本文對每種緩沖器類型僅討論一個引腳,以簡化對IBIS模型構建和驗證過程的解釋。

ADuM4146采用標準小型寬體封裝(SOIC_W),封裝在驗證過程中以寄生電阻、電感和電容(RLC)的形式表示。封裝工程師通過仿真提取封裝RLC值。專用印刷電路板(PCB)與封裝寄生的情況類似,也是由寄生RLC表示,其值由PCB工程師提取。

圖3.ADuM4146功能框圖

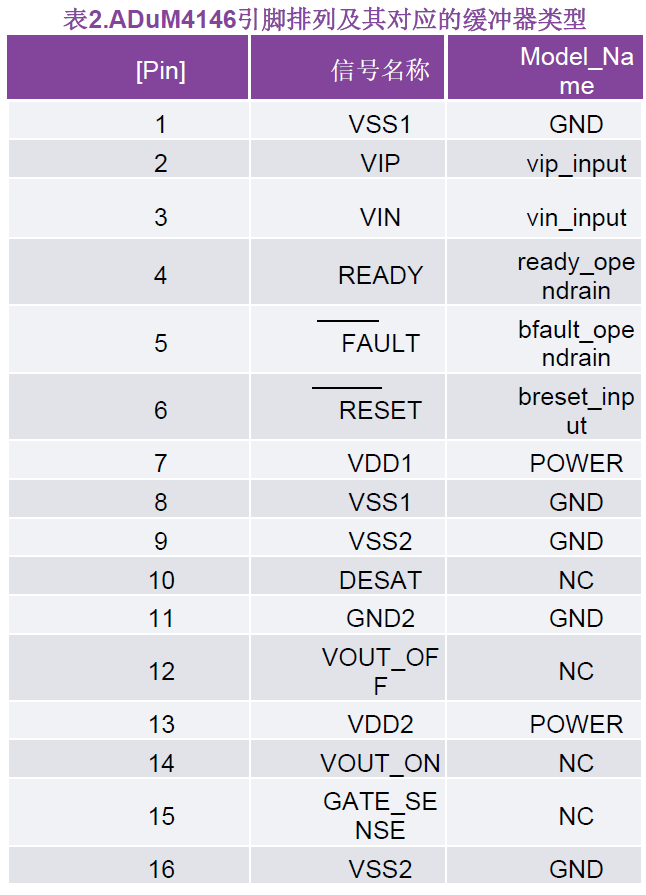

表2顯示了ADuM4146引腳配置和每個引腳對應的緩沖器類型。此信息將用于IBIS模型的[Pin]關鍵字。

IBIS基準測量步驟

通過基準測量收集數據可能會受到不同外部因素的影響。應補償這些因素以滿足相關并提供高質量模型。

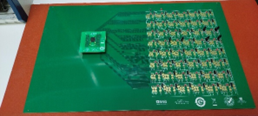

為了最大限度地減少外部因素的影響,待測器件(DUT)放置在專用夾具上,以減小可能導致被測器件行為不準確的干擾電容,如圖4所示。寄生電容是實際硅片測量中的一個重要問題,并且常常是限制器件模型工作頻率和帶寬的因素。

圖4.IBIS基準測量專用夾具

通過基準測量生成IBIS模型的步驟:

準備設置

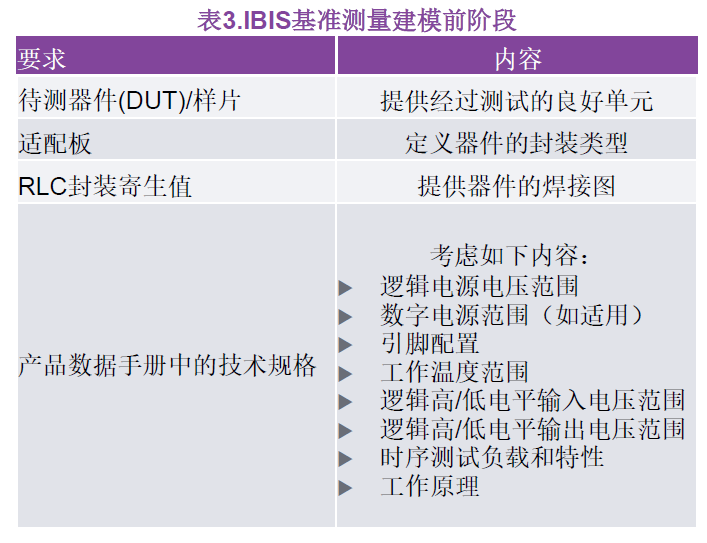

表3顯示了基準測量的IBIS預建模階段要求,表4顯示了定義緩沖器行為的不同模型類型和模型組成。模型類型在文章“IBIS建模—— 第1部分: 為何IBIS建模對設計成功至關重要”和“IBIS 建模——第2部分: 為何以及如何創建您自己的IBIS模型”中有詳細討論。您也可以參考IBIS建模手冊。

試驗臺設置

了解器件的運行方式對于IBIS模型的數據收集至關重要。如圖1所示,這是第一階段,通過提取I-V數據和V-t數據來完成。兩者都以表格形式表示。

I-V數據包括ESD箝位行為和驅動器強度,而V-t數據表示從低/高電平狀態到高/低電平狀態的轉換。切換行為是通過將負載連接到輸出引腳來測量,這個負載與輸出緩沖器將要驅動的值相等。然而,通常的負載值為50Ω,代表典型的傳輸線阻抗。

對于I-V測量,使用能夠吸收和提供電流的可編程電源和曲線跟蹤器來掃描電壓并收集緩沖器的電流行為。建議在–VDD至2×VDD的電壓范圍內以及典型值、最小值和最大值拐角處獲取數據。V-t測量需要使用具有適當帶寬和低電容探頭的示波器。

DUT安裝在專用工具上,使用溫度強制系統在不同溫度條件下進行測試,以獲取最小、典型和最大性能。在這種情況下,最小(最弱驅動強度、最慢邊沿)數據是在125°C下獲取,最大(最強驅動強度、最快邊沿)數據是在–40°C下獲取。

基準數據提取

一旦驗證試驗臺設置已準備就緒,就可以開始收集所需I-V和V-t數據的過程。輸出和I/O緩沖器需要I-V表和上升/下降數據,而輸入緩沖器只需要I-V表。

u I-V(電流與電壓)數據測量

I-V曲線測量涵蓋四個IBIS關鍵字——[Pullup]表示驅動高電平時上拉元件的I-V行為,[Pulldown]表示驅動低電平時下拉元件的I-V行為,而[Power Clamp]和[GND Clamp]表示高阻抗狀態下ESD保護二極管的I-V行為。

要測量I-V特性,請將器件安裝在專用板上,并將電源和接地引腳連接到電源。準備溫度強制系統,調整到所需溫度,等待其穩定。在推薦范圍內掃描電壓,然后使用曲線跟蹤器測量所需緩沖器的電流。

用于上拉和電源箝位數據的掃描設備的正節點應連接到電源電壓,負節點應連接到引腳,而用于下拉和接地箝位數據的掃描設備以地為參考。當曲線跟蹤器無法掃描整個范圍時,可能需要外推。

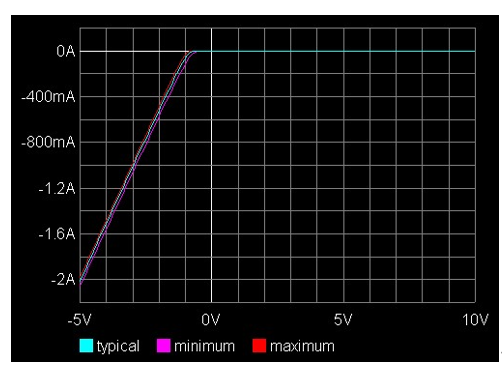

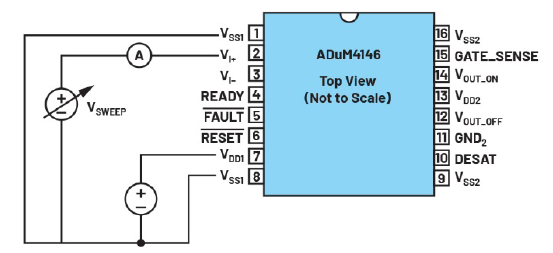

圖5顯示了輸入緩沖器(VI+) I-V接地箝位測量的試驗臺設置,而圖6顯示了其測量行為。當輸入降低到地以下導致負電流時,接地箝位電路被觸發,使電流接近并穩定為零。輸入引腳(VIP)沒有電源箝位元件,因此其模型不會有電源箝位數據。

圖5.用于I-V箝位測量的ADuM4146試驗臺設置

圖6.ADuM4146輸入緩沖器試驗臺測量的接地箝位

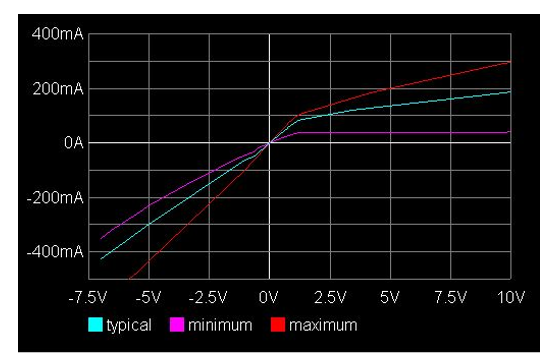

對輸出緩沖器的ESD箝位、上拉和下拉數據實施相同的方法。但在這種情況下,ADuM4146 READY和FAULT引腳為開漏緩沖器。因此,它們沒有上拉元件,只需要下拉數據。

圖7.ADuM4146開漏緩沖器下拉結果

圖7顯示了ADuM4146開漏緩沖器的下拉數據結果。下拉曲線從負電流開始,然后穿過零到達正象限,也在–VDD至2×VDD的范圍內。

u 緩沖電容(C_comp)提取

根據IBIS建模手冊(IBIS 4.0版),“每個焊盤的總裸片電容或C_comp參數是從焊盤向緩沖器看到的電容,用于完全布局布線的緩沖器設計,不包括封裝效應”。獲得C_comp值的一種方法是使用以下公式。

![]()

其中:

CIN = 器件輸入電容

Cpkg = 器件封裝電容

u V-t(輸出電壓與時間)數據測量

V-t曲線測量也涵蓋了四個IBIS關鍵字——[Rising Vddref]和[Falling Vddref]與以電源為參考的負載的從低到高和從高到低的轉換有關,而[Rising Gndref]和[Falling Gndref]與以地為參考的負載的從低到高和從高到低的轉換有關。與這些相關的是關鍵字[Ramp],它定義了從一種狀態變為另一種狀態時的轉換速率,取波形的20%到80%。

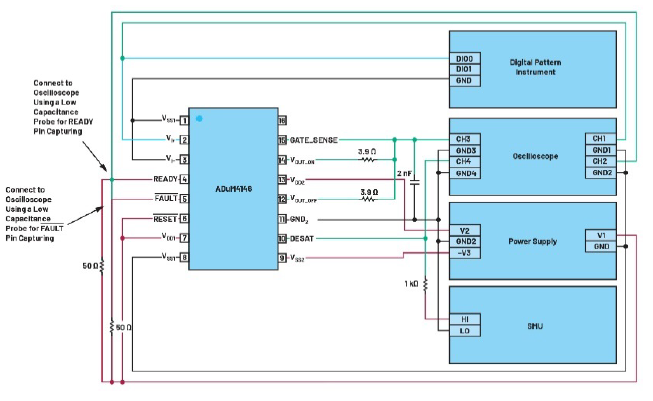

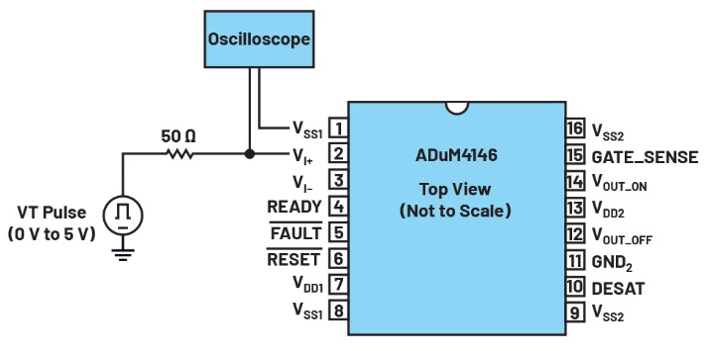

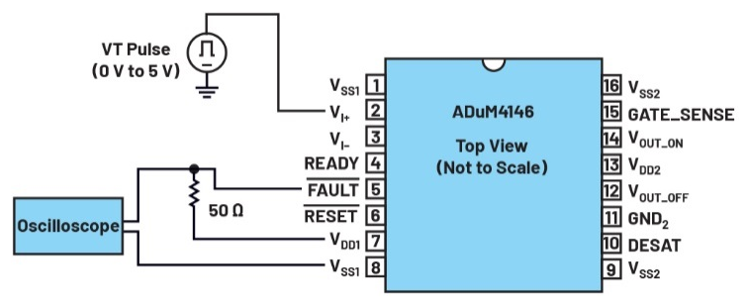

測量上升和下降時間數據需要在驅動所需負載的緩沖器上使用示波器。在這種情況下,使用一個50Ω電阻來表示傳輸線阻抗。對于開漏型,將負載連接到緩沖器和電源電壓以測量切換行為(以VDD1為基準)。務必使用溫度強制系統以根據需要穩定溫度,從而捕獲最小、典型和最大范圍。圖8顯示了ADuM4146 READY和FAULT引腳切換行為的實際試驗臺設置。ADuM4146數字輸出引腳為開漏型,因此只需要以電源電壓為基準的上升和下降行為。

圖8.ADuM4146 READY/FAULT切換行為的試驗臺設置

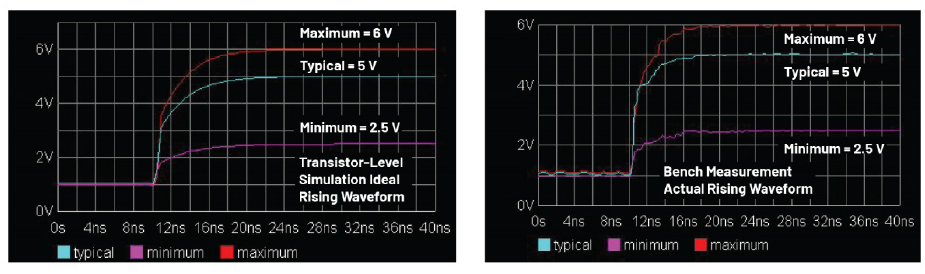

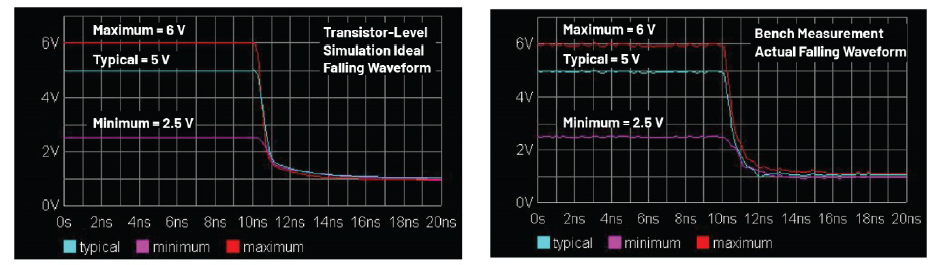

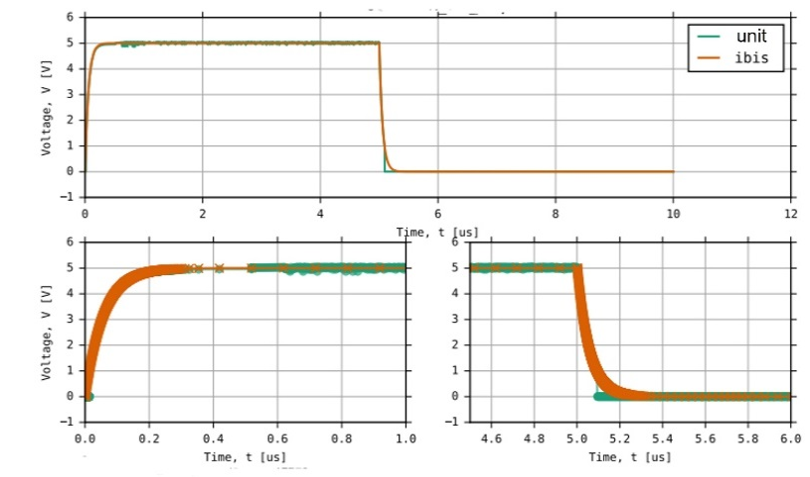

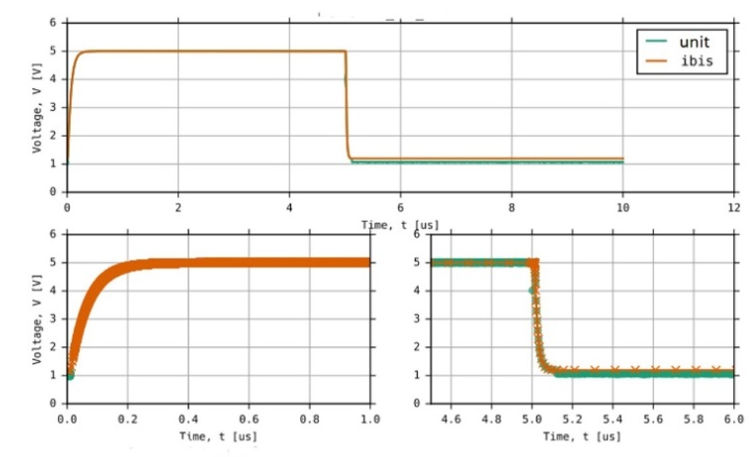

圖9和圖10顯示了在晶體管級仿真和實際芯片測量中捕獲的FAULT引腳上升和下降波形。兩種設置使用相同的負載條件,即50Ω連接到VDD1,跨越典型值、最小值和最大值拐角。

圖9.ADuM4146 FAULT引腳上升波形(以VDD1為基準)

圖10.ADuM4146 FAULT引腳下降波形(以VDD1為基準)

構建IBIS模型

創建IBIS模型的下一階段是處理收集的數據并構建模型本身。在此階段,在必要的關鍵字之后以IBIS文本格式插入原始數據表,包括器件參數。詳細過程參見文章“IBIS建模—— 第1部分: 為何IBIS建模對設計成功至關重要”。

圖11.從基準測量生成的ADuM4146 IBIS模型

圖11顯示了從基準測量生成的ADuM4146 IBIS模型。該模型應通過IBIS解析器檢查,包括基本檢查,例如I-V和V-t表之間的匹配以及檢查表格數據的單調性。在繼續驗證過程之前,應完全解決所有錯誤、警告和注意事項。此外,模型應通過IBIS質量檢查清單的檢查。

驗證和結果

本文的驗證過程將遵循本系列的第二篇文章“IBIS建模——第2部分:為何以及如何創建您自己的 IBIS模型”中說明的步驟,其中討論了有關IBIS模型驗證過程的更多詳情。

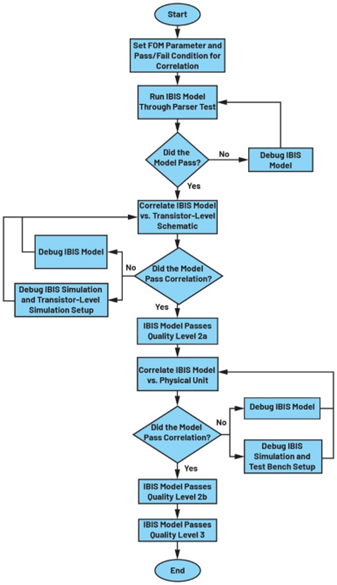

圖12.IBIS模型質量等級3驗證過程流程圖

模型首先必須通過解析器測試,這可以使用集成了IBISCHK的軟件來進行檢查,或使用來自ibis.org的開源可執行代碼進行檢查。通過解析器測試后,模型必須與其晶體管級原理圖或實際芯片單元相關聯。本文旨在實現質量等級為3級的模型,因此ADuM4146的IBIS模型將與其晶體管級原理圖和實際單元相關聯。設置品質因數(FOM)值以確定IBIS模型是否會通過這兩種相關性檢查。在這種情況下,兩種相關性的FOM值必須大于或等于95%才能通過質量等級3 IBIS模型驗證。圖12顯示了IBIS模型達到質量等級3所必須通過的驗證過程的流程圖。

曲線度量下方的面積將用于計算兩種相關性的FOM值。須將相同的負載條件放置在這兩組相關性上。在驗證過程中,建議按照數據手冊中指示的負載條件來測試設備的正常運行。

為了根據參考正確驗證IBIS模型(例如,IBIS與基準測量的相關性),必須把信號在基準測量設置中經過的PCB走線添加到IBIS仿真設置中。

以下是實現質量等級為3級的IBIS模型的兩個條件。

IBIS質量等級2a驗證

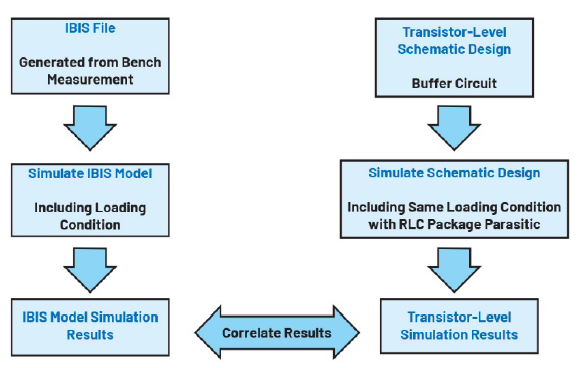

圖13.IBIS模型質量等級2a驗證過程

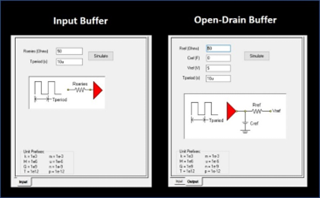

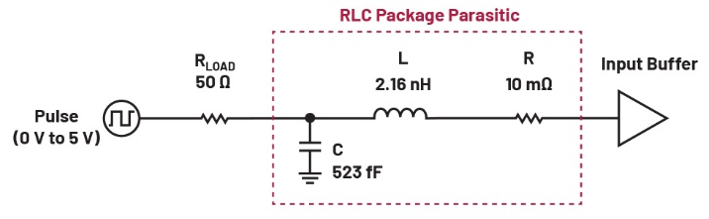

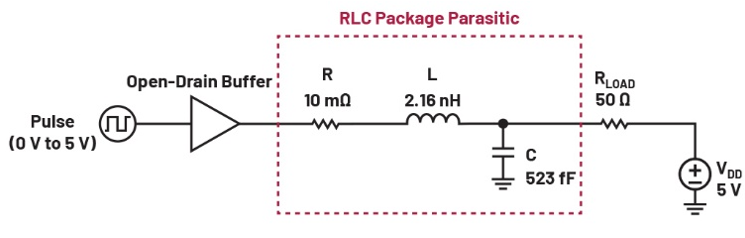

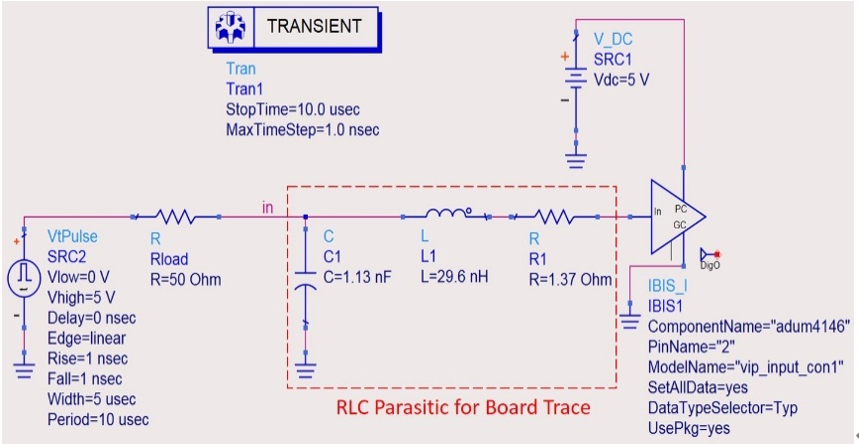

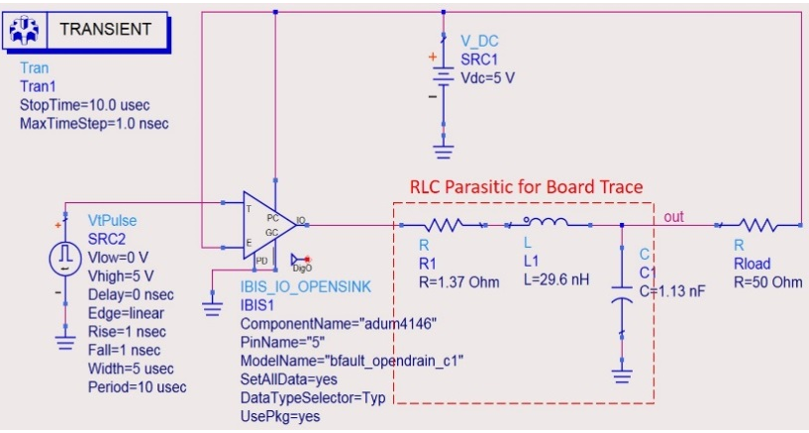

圖13顯示了IBIS模型質量等級2a驗證過程。該相關處理旨在評估IBIS模型數據將在何種程度上產生與晶體管級仿真結果相匹配的仿真。圖14顯示了ADuM4146的輸入和開漏緩沖器的IBIS模型仿真設置以及負載條件。

圖14.ADuM4146輸入和開漏緩沖器仿真設置

圖15.ADuM4146晶體管級設計仿真設置和負載條件(輸入緩沖器)

圖16.ADuM4146晶體管級設計仿真設置和負載條件(開漏緩沖器)

圖15和16分別顯示了輸入和開漏緩沖器的晶體管級設計仿真設置以及負載條件。器件的封裝RLC值添加在緩沖器和負載之間,以再現IBIS設置中的封裝寄生效應。

圖17.晶體管級設計與IBIS模型驗證結果的關系(輸入緩沖器)

圖18.晶體管級設計與IBIS模型驗證結果的關系(開漏緩沖器)

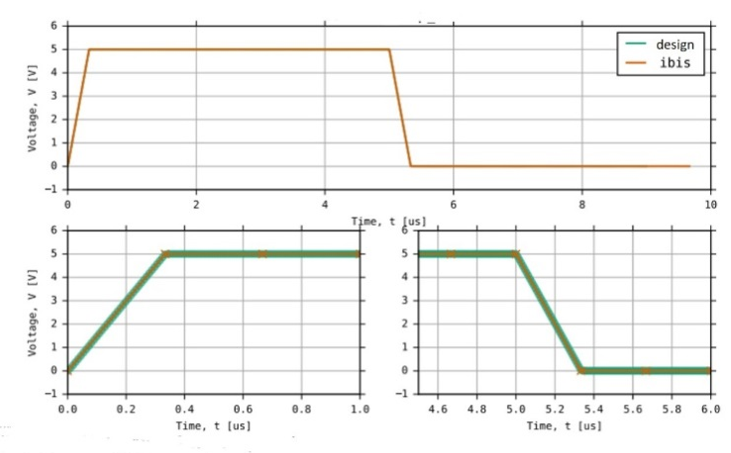

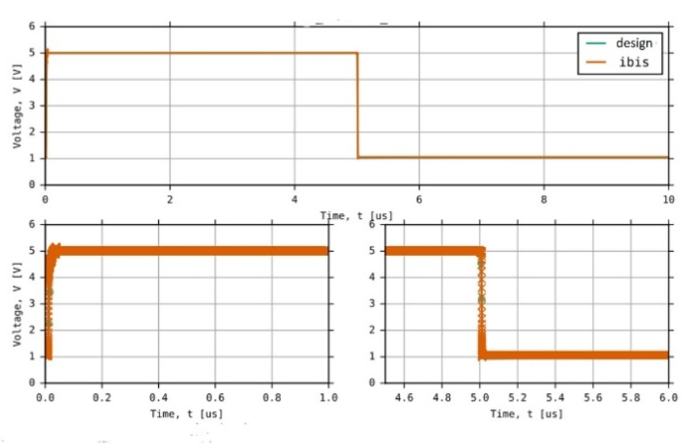

圖17和圖18分別顯示了IBIS模型在標準負載下運行并將結果與使用相同負載下的晶體管級參考仿真進行比較時,輸入和開漏緩沖器的相關結果。一個50Ω電阻用作開漏緩沖器的IBIS與晶體管級相關性設置的負載。使用10μs脈沖輸入對兩種設置進行瞬態分析。

表5顯示了兩個緩沖器模型在與晶體管級原理圖相關時計算出的FOM值。兩個緩沖器模型的FOM值均大于95%,因此IBIS模型達到了質量等級2a。

IBIS質量等級2b驗證

IBIS質量等級2b要求模型與基準測量相關,因此需要考慮可能影響基準測量性能的因素。執行基準測量的主要挑戰是信號衰減,大部分是由走線寄生效應引起的。利用實際單元測量數據時,最好使用帶有低電容探頭的專用板,以盡可能減少走線寄生效應的影響。在這種情況下,IBIS試驗臺專用板是信號完整性問題的解決方案,可減少混入目標信號的干擾信號所引起的衰減。圖19顯示了IBIS質量等級2b的驗證過程。

圖19.IBIS模型質量等級2b驗證過程

IBIS模型相關性的主要目標是獲得盡可能接近參考的結果。在示波器中捕捉上升/下降時間數據時,最好使用負載極低的探頭,以減少信號衰減。探頭和儀器組合引入的誤差會對目標信號產生重大影響。根據Tektronix,“使用特殊濾波技術和正確選擇工具以去除測量系統對信號的影響、顯示邊沿時間以及其他信號特性,是測量實際芯片性能時要考慮的關鍵因素”。

圖20和圖21分別顯示了使用輸入和開漏緩沖器并考慮負載條件的IBIS模型的仿真設置。串聯到緩沖器的RLC值是來自電路板走線的寄生值。添加負載以復制實驗室設置時,重要的是要考慮其對模型性能的影響。

圖20.實際IBIS仿真設置和負載條件(輸入緩沖器)

圖21.實際IBIS仿真設置和負載條件(開漏緩沖器)

圖22.試驗臺設置和負載條件(輸入緩沖器)

圖23.試驗臺設置和負載條件(開漏緩沖器)

圖22和23分別顯示了負載條件下輸入和開漏緩沖器的試驗臺設置的示意圖。5V脈沖信號用于驅動連接到50Ω負載的開漏緩沖器。圖24和圖25分別顯示了輸入和開漏緩沖器的IBIS仿真與基準測量的相關結果。

圖24.實際芯片單元與IBIS模型驗證結果的關系(輸入緩沖器)

圖25.實際芯片單元與IBIS模型驗證結果的關系(開漏緩沖器)

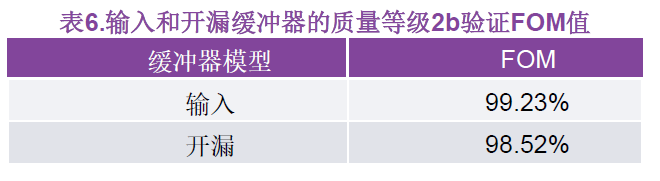

表6顯示了輸入和開漏緩沖器的FOM值與實際芯片基準測量的相關性。FOM值大于95%,這意味著兩個緩沖器的IBIS模型達到了質量等級2b。由于該模型通過了質量等級2a和質量等級2b檢查,因此現在可以將其視為質量等級3 IBIS模型。

結論和要點

通過基準測量構建高質量IBIS模型時,提取硬件與模型相關所需的數據是最具挑戰性的步驟之一。通過仔細關注細節并了解I/O電路的行為,可以實現實驗室測量與IBIS仿真結果的密切相關。在相關處理中,盡可能多地消除衰減是獲得高FOM值的關鍵。考慮到這一點,建議使用專用測試平臺以及匹配良好的設備和配件,以確保信號的完整性。

同時須記住,在相關處理中,IBIS模型和試驗臺設置在信號經過的走線方面必須完全相同。這將能減少相關性引起的誤差,從而提高FOM值。

擁有質量等級為3級的IBIS模型對半導體供應商和客戶來說都是一個優勢,有助于確保模型從硅前驗證到實際芯片測量時獲得更高的精度水平。

致謝

感謝ADI設計工程師、ADGT測試開發工程師和ISO團隊全力支持完成本項目。此外,感謝ADGT系統集成經理對項目贊助的支持。

###

關于ADI公司

ADI是全球領先的高性能模擬技術公司,致力于解決最艱巨的工程設計挑戰。憑借杰出的檢測、測量、電源、連接和解譯技術,搭建連接現實世界和數字世界的智能化橋梁,從而幫助客戶重新認識周圍的世界。

關于作者

Christine C. Bernal于2007年6月加入ADI,擔任產品工程師。2016年,她在新技術集成團隊為各種ADI產品開發IBIS模型。Christine于2015年畢業于馬尼拉馬普阿大學,主修微電子,獲電子與通信工程碩士學位。

Janchris Espinoza是ADI公司新技術集成團隊的產品應用工程師。主要負責對ADI產品進行IBIS建模和仿真。他于2019年在ADI的Analog Garage團隊實習,并于2020年9月正式加入ADI。他于2020年2月畢業于德拉薩大學,獲電子工程學士學位。

Aprille Arjhilynne Hernandez-Loyola于2015年8月加入ADI。她是新技術集成團隊的產品應用工程師。她主要從事建模和電路仿真工作,尤其是ADI產品的LTspice?和IBIS。她畢業于德拉薩大學(達斯馬里尼亞斯分校),獲電子與通信工程學士學位。

評論