Teledyne e2v:通過雜散抑制IP,立即將寬帶ADC的動態性能提高約10 dBFS

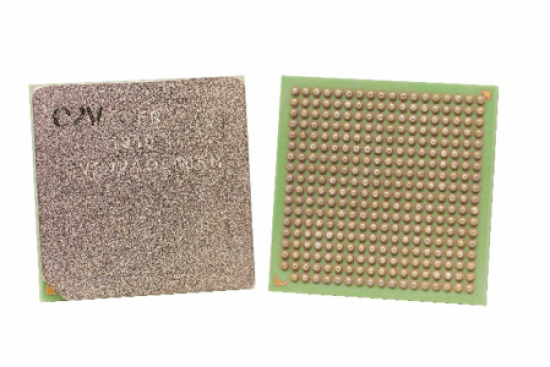

新的EV12AQ600/605-ADX4器件選項具有集成的ADX4許可證密鑰,可提高高達6.4 GS/s(單通道模式)的峰值運行時的動態性能。

本文引用地址:http://www.j9360.com/article/202206/435277.htmADX4 - 與Xilinx Kintex? Ultrascale? FPGA兼容的后處理算法可在寬帶應用中提供高達10 dBFS的SFDR動態雜散抑制和接近1個有效位的額外分辨率。

時間交錯雖然提供了概念上易于理解的采樣率提升,但在擴展分辨率和寬帶寬下很難實現。

為EV12AQ600/5提供即時、無需設計的動態性能增強

Teledyne e2v今天宣布即將推出具有集成的許可證密鑰的EV12AQ600/5選項,可直接使用Teledyne集團公司旗下SP Devices開發的新型ADX4后處理算法。ADX4雜散抑制IP可動態抑制由四個ADC內核之間的增益、偏移和相位不匹配導致的雜散頻率分量。時間交錯是提高ADC采樣率的可靠的架構方法。然而,在10位分辨率以上和寬帶應用中,通過校準避免產生頻譜失真非常具有挑戰性。

|

對于EV12AQ600/5,四個核心的時間交錯將采樣率從1.6提高到6.4 GS/s。ADC核心之間的不匹配誤差降低了無雜散性能。ADX4可提供高達10 dB的無雜散動態范圍(SFDR)提升。這種提升在寬帶應用中尤其明顯,因為它不需要硬件設計的更改。用戶可方便地將ADX4代碼模塊燒寫進后處理FPGA中,甚至可以在工作現場進行。

關于ADC時間交錯

高分辨率數據轉換器正在快速發展,以獲取更寬的瞬時帶寬。實現更高采樣率的一種理論上簡單的方法是對現有內核應用時間交錯。多個ADC核心在公共采樣時鐘的不同相位上進行時鐘控制,從而允許獲取更高密度的信號采樣。這種增加的采樣密度提供了一種有用的性能擴展,并且可以很好地使用高達8位的分辨率。通過標準的混合信號校準和電路布局方案,跨內核匹配相對更容易管理。

對于10位及以上的分辨率,尤其是在千兆赫茲范圍內工作,則越來越難以確保匹配。因此,會出現采樣偽影,導致失真并限制測量的動態性能。這些高頻不匹配誤差在模擬設計領域很難緩解。因此,對于6.4 GS/s時間交錯ADC,要在3 GHz輸入信號下實現72 dB SNR(理論最大12位),需要優于12 fs的跨核相位匹配。

值得慶幸的是,在過去的二十年里,DSP資源的成本已經顯著下降,如今采用算法方法來減少雜散在經濟上是可行的。Teledyne SP Devices專門設計和制造高分辨率超高速數字化儀,幾十年來積累了有關先進分立轉換器的豐富經驗,并精通這方面的相關技術。

與單點或多點校準不同,ADX4數字誤差校正可以在誤差隨頻率變化時提供雜散抑制,使得不需要的混疊雜散被抑制到噪聲本底中。

實現ADX4

獲得ADX4動態增強非常容易。通過所需的供應鏈,客戶只需將訂單轉移到EV12AQ600/5器件的-ADX4選項。此外,他們需要將ADX4模塊添加到Xilinx FPGA代碼負載中。這樣就大功告成了。

ADX4供應

以下組件列表顯示了當前隨ADX4許可證密鑰提供的EV12AQ600/5選項。考慮雙通道模式工作的客戶可直接聯系Teledyne e2v,咨詢ADX2許可證密鑰選項的未來供應情況。

評論