大容量電池充放電管理模塊MOSFET選型及應用

作者簡介:劉松,男,武漢人,碩士,現任職于萬國半導體元件有限公司應用中心總監,主要從事開關電源系統、電力電子系統和模擬電路的應用研究和開發工作。獲廣東省科技進步二等獎1項,發表技術論文60多篇。E-mail: songliu@aosmd.com。

本文引用地址:http://www.j9360.com/article/202112/430649.htm0 引言

鋰離子電池包內部的電芯和輸出負載之間要串聯功率MOSFET,使用專用的IC 控制MOSFET 的開關,從而對電芯的充、放電進行管理。在消費電子系統中,如手機電池包、筆記本電腦電池包等,帶有控制IC、功率MOSFET 管以及其他電子元件的電路系統稱為電池充放電保護板(protection circuit module,PCM)。離子電池的容量從早期的600 mA·h, 到現在高達10 000 mA·h,為了實現更快的充電速度,降低充電時間,通常采用提高電流、使用大電流充電的快充技術,另外,大容量鋰離子電池在生產線和使用過程中,還有一些特定的技術要求,所有這些因素都對大容量鋰離子電池包充、放電管理的功率MOSFET 提出了嚴格的技術設計挑戰。[1-2]

1 功率MOSFET的配置方式

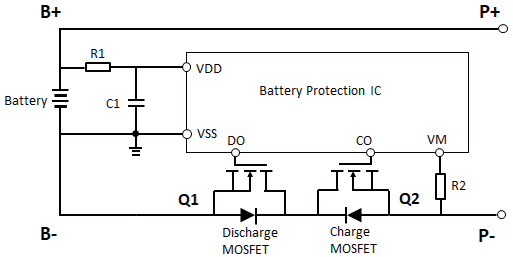

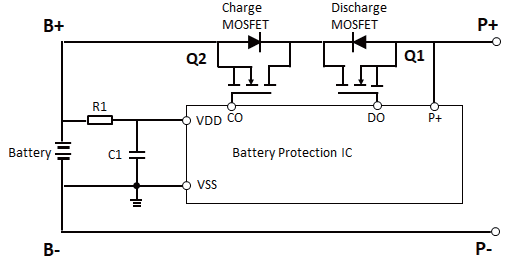

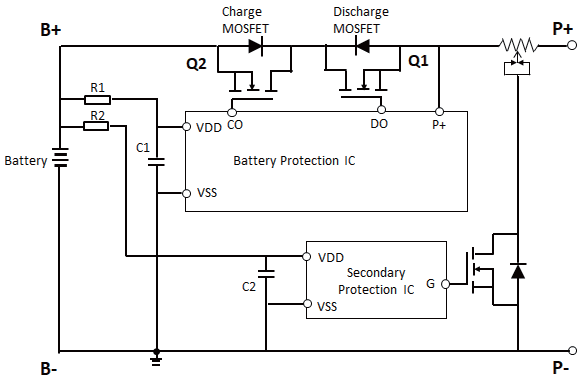

在電池充放電保護板PCM 中,充、放電分別使用1 顆功率MOSFET,背靠背串聯起來。MOSFET 背靠背串聯的方式有2 種:1 種是2 顆漏極連接在一起;另1 種是2 顆源極連接在一起。MOSFET 放置的位置也有2 種方式:①放在電池的負端,也就是所謂的“地端”、低端(low side);②放在電池的正端,高端(high side)。MOSFET 連接的不同方式以及放在不同位置各有優缺點,對應系統的不同要求。

PCM 需要低的導通電阻,同時要控制成本,通常采用N 溝道MOSFET。P 溝道率MOSFET 放在高端驅動簡單靈活,少量的應用也會采用。但是,其導通電阻很難做低,成本高,選擇和供應廠家也受限,因此,N溝道MOSFET 依然是主流的方案。如果MOSFET 有非常嚴格的體積和尺寸要求,需要將2 個MOSFET 集成到1 個芯片上,通用功率MOSFET 是垂直結構,襯底是漏極D,因此,使用漏極的背靠背結構就可以采用這樣的工藝。

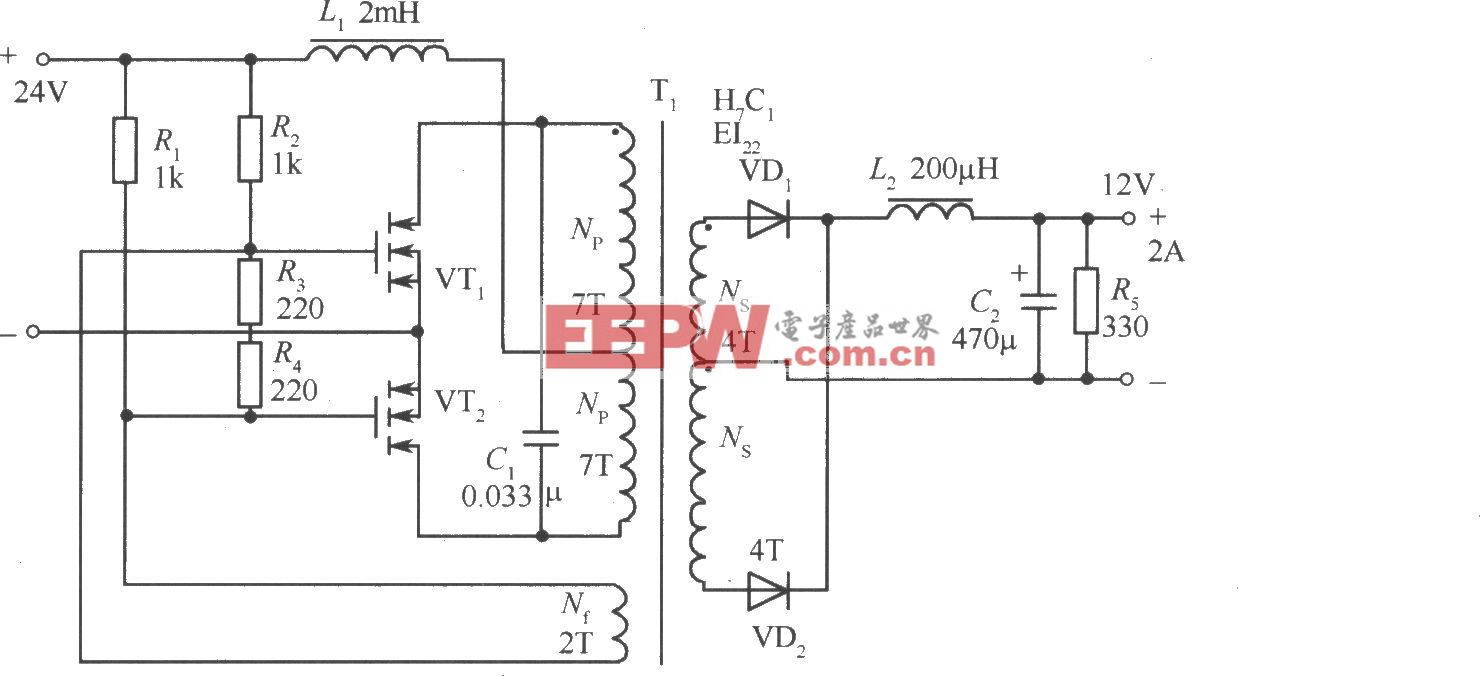

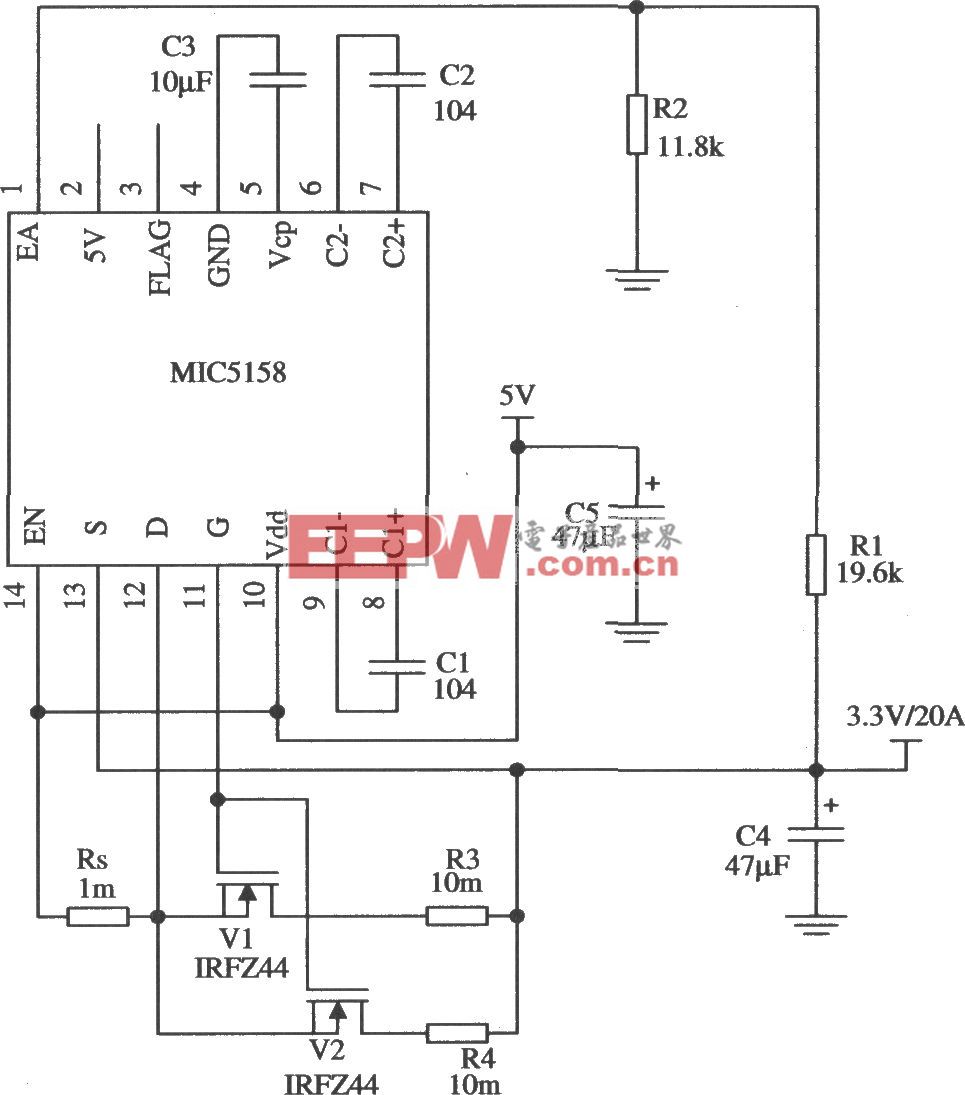

2 顆N 溝道功率MOSFET 放在地端,或電源端(高端),漏極背靠背連接在一起,是PCM 常用的2 種方案,如圖1 所示。前者驅動簡單,后者因為MOSFET 的源極電壓浮動變化,需要2 個充電泵進行浮驅。

(a)功率MOSFET放在高端,漏極背靠背

(b)功率MOSFET放地端、漏極背靠背

圖1 PCM的功率MOSFET配置方式

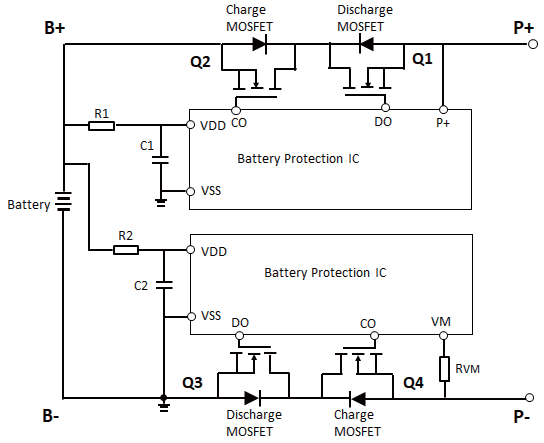

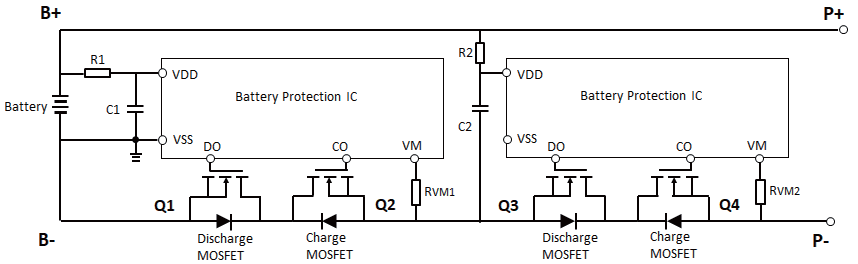

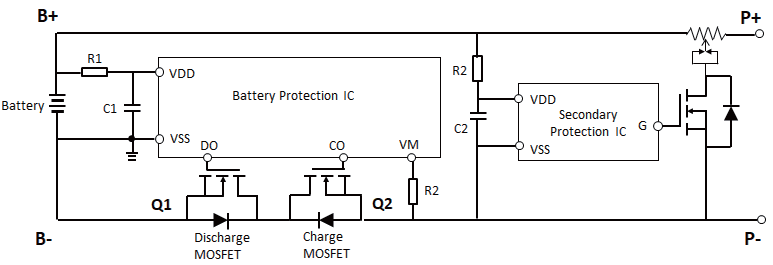

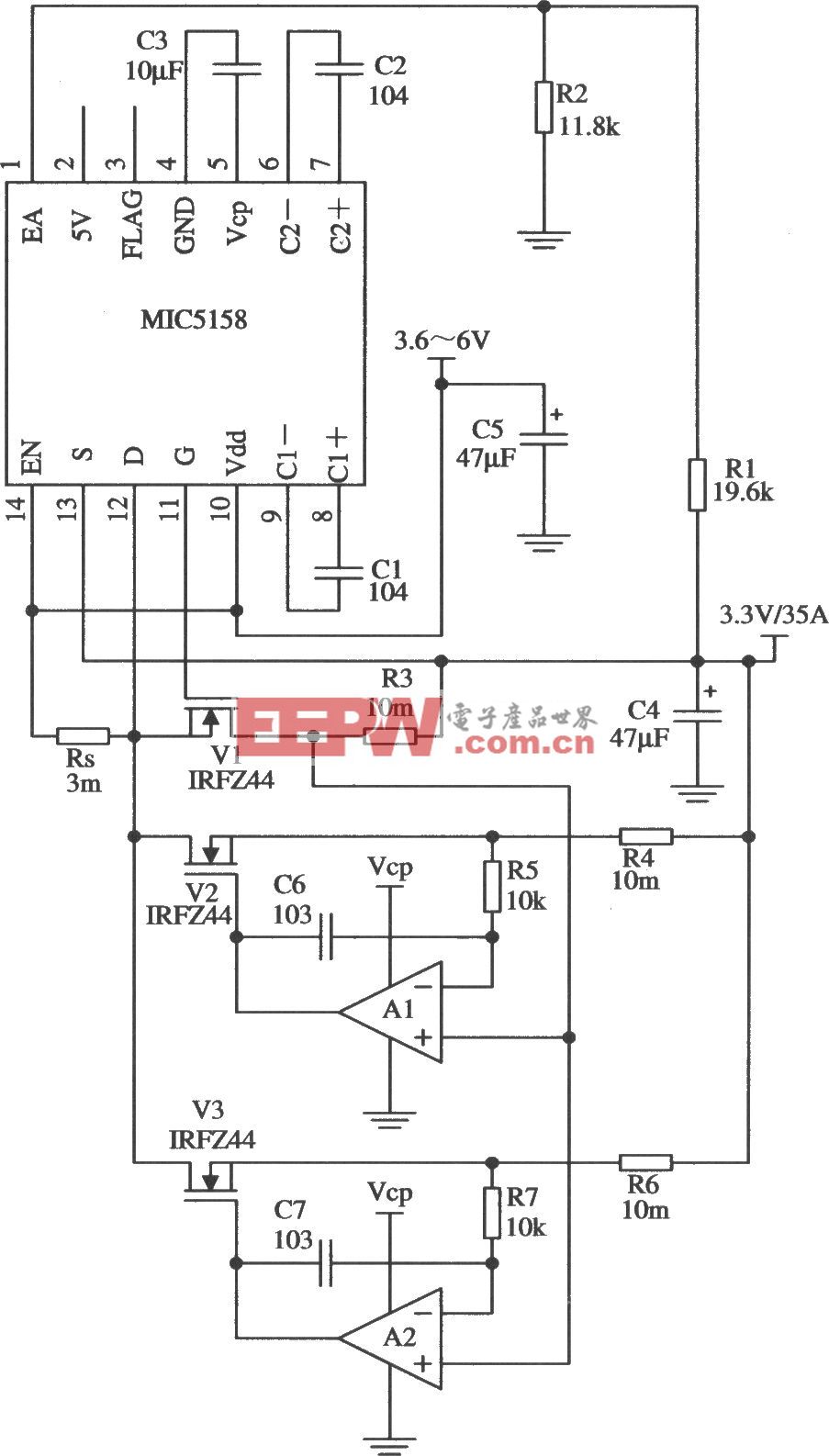

大容量電池充電電流更大,如4 A、5 A、甚至高到8 A,PCM 內部MOSFET 的功耗非常大,溫度非常高。為了降低MOSFET 的溫升,滿足熱設計的要求,就會使用2 個或多個功率MOSFET 并聯工作。根據安規LPS 要求,如果PCM 內部MOSFET 發生損壞而短路,充電器輸入電壓直接加在電池上可能發生危險。為了提高系統的安全,可以再串聯1 組背靠背MOSFET,或使用其他方案,形成冗余設計,二級保護,如圖2 所示。

(a)2組功率MOSFET,1組放在高端,1組放在低端

(b)2組功率MOSFET放在低端

(c)功率MOSFET放在高端,電子保險絲

(d)功率MOSFET放在低端,電子保險絲

圖2 PCM的功率MOSFET配置方式

2 PCM中功率MOSFET的性能要求

2.1 高功率密度、低功耗、散熱好

大容量鋰離子電池包設計的基本要求是在一定體積和重量條件下盡可能提高電池的容量,從而提高功率密度。由于其空間非常有限,因此要求PCM 上面的MOSFET 具有更小的體積和尺寸;同時,由于快充電流大,MOSFET 在一定尺寸限制下,如1.2 mm×1.2 mm,具有最小的導通電阻(RDS(ON))。理論上,更小的RDS(ON)要求更大的芯片尺寸。為了在同樣的芯片尺寸實現更低的RDS(ON),從設計上主要從2 個方面進行優化。

1)晶圓技術

為了使MOSFET 實現更低的RDS(ON), 必須對MOSFET 內部結構重新設計,使用各種最新技術降低內部單元結構的晶胞尺寸,提高晶胞單元密度;同時,改變內部電場分布,在保證同樣耐壓的前提下,盡可能降低芯片厚度,這樣,MOSFET就可以實現超低的FOM值,獲得更低的RDS(ON)。

2)封裝技術

為了進一步降低導通電阻,在PCM 中使用芯片級CSP 封裝技術,完全去除封裝連線電阻,CSP 芯片熱阻更低,降低功率MOSFET 的溫度。

由于CSP 封裝的MOSFET 沒有外部塑料殼等材料的保護,在生產加工過程中,如PCB 板焊接,會受到各種熱應力、機械應力的作用產生開裂的風險,因此,要采用各種技術,如在MOSFET 芯片的表面涂敷新材料,以保證其抗機械應力和熱應力的能力,提高可靠性。

2.2 抗短路的能力

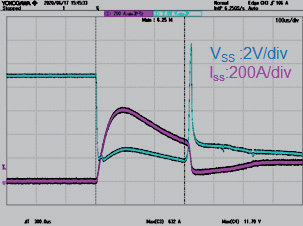

在極端條件下應用,如電池包的輸出負載短路,電池會流過非常大的電流,IC 過流保護也有延遲,要求MOSFET 具有承受大電流沖擊的能力。因此,現在安規要求電池包都要做短路測試,以免電池發生爆炸。

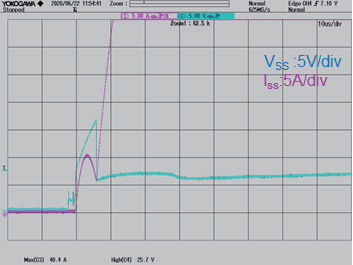

圖3 短路測試失效波形

理論上,芯片尺寸越大,抗短路沖擊的能力越強。在非常小的芯片尺寸限制條件下,需要對MOSFET 內部結構做特定的設計,以保證其具有足夠的抗短路大電流沖擊的能力。

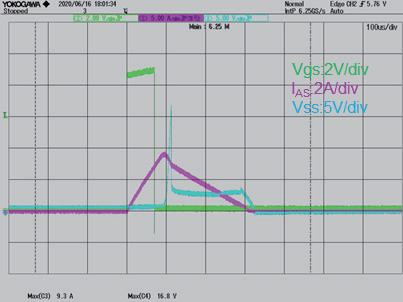

2.3 抗雪崩能力

MOSFET 的雪崩能力表明器件的強壯程度和可靠的工作能力,特別是電池包的輸出端短路關斷后,非常容易發生雪崩,需要對MOSFET 的結構做優化,以保證其具有足夠的雪崩能力。[3-6]

圖4 雪崩測試失效波形

2.4 高抗dV/dt能力

在生產過程中,外部的測試直流電源會直接碰觸電池包的2 個輸出端,電路不發生損壞的碰觸電壓越高,能力越強,這個測試實際測量的是MOSFET 對dV/dt 的耐受能力,過大dV/dt 會引起MOSFET 動態雪崩損壞。因此,需要對MOSFET 的結構做優化,以保證其具有高直接碰觸電壓和抗dV/dt 的能力。

圖5 直接碰觸電壓測試,14 V測試失敗

3 PCM的PCB及熱設計要點

PCM 控制板和電池組裝在一起,要求PCB 尺寸比較小,發熱量不能過高,手機應用要求MOSFET 在常溫環境滿載條件下表面溫度不超過65 ℃。如47 W 手機快充,充電電壓為5 V,最大充電電流為9.4 A,需要并聯2 顆AOCR38232(0.8 mΩ),電流路徑采用上下對稱,以保持電流均衡。2 顆MOS 之間間隔3 cm,避免相互加熱。盡可能增加功率路徑鋪銅面積,且在靠近MOSFET 的銅皮上增加散熱孔增加散熱,減小MOSFET 溫升。

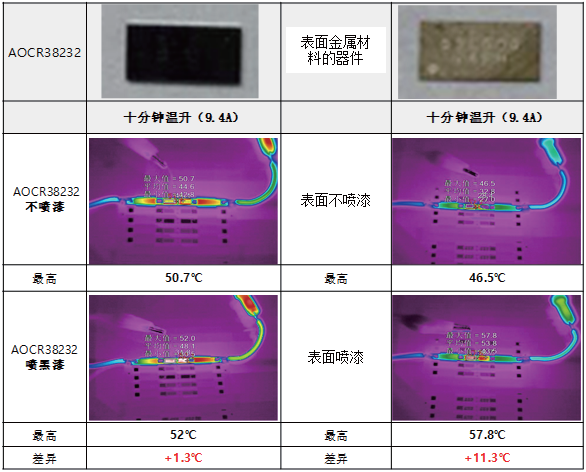

用紅外測溫儀測量MOSFET 表面溫升,由于不同器件的表面材質不同,產生的光學折射率也不同。金屬表面溫升需要先用光學折射率為100% 的黑色油漆噴涂器件表面,然后再進行測試,才能得到準確的溫升數據,如圖6 所示。

圖6 PCM板的MOSFET溫度測量

4 輸出漏電流產生原因及解決方法

4.1 輸出漏電流產生的原因

電池端B+、B- 有電壓時,充電管和放電管都處于關閉狀態。此時,如果有微小的漏電流,如100 nA,由于輸出端并沒有負載,輸出端呈現高阻抗狀態,如10 MΩ,此時控制芯片會檢測到輸出端有1 V 電壓。以BQ20Z45 為例,當輸出P+、P- 之間電壓高于0.8 V 時,控制芯片會誤判輸出有充電電壓,啟動預充電功能,開啟充放電管,嘗試給電池充電,增加電池的靜態損耗,嚴重時會導致電池電量耗盡。

30 V 功率MOSFET 通常數據表會列出30 V 的IDSS小于1 μA,實際筆記本電腦電池應用中電池電壓通常在9~13.2 V 之間,IC 很難判斷在13.2 V 電池電壓下放電管DS 漏電流是不是大于100 nA,從而出現應用的問題。

在出廠測試IDSS 時,器件廠家使用300 μs 的脈沖電壓進行短時間的漏電流測試。在實際應用中,功率管長時間承受偏壓,載流子會注入到柵極,雖然外部GS 電壓為0 V,內部局部單元柵極仍有殘余電荷,抬高局部柵極電壓,從而導致DS 漏電流增大;同時,工廠短時間脈沖測試無法保證長時間偏壓情況下的漏電流,從而也會導致極少量MOSFET 在使用后IDSS 超出1 μA,使器件漏電流過大。

4.2 輸出漏電流的解決辦法

在實際系統中,主板電池輸入接口的阻抗普遍低于1 MΩ,上述漏電流異常,在系統上并不會產生問題,只是在電池包廠家庫存期間,可能發生電池電量異常下降的問題。

為了解決這個問題,可以采用以下方案。

方案1:電池包輸出端P+、P- 并聯1 MΩ 電阻,避免因漏電流產生的輸出電壓導致芯片誤檢測而出現問題。

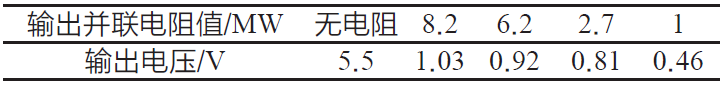

增加1 MΩ 電阻后,P+ 端的漏電流產生的漏電壓下降到0.46 V,如表1 所示,內部MOSFET 不會開通,系統正常。

表1 增加外部電阻后的輸出電壓

增加電阻的不利之處是會導致電池弱放電,但是,其消耗的電量非常小,可以忽略。

方案2:芯片調整輸出檢測電壓,單節電池建議從0.8 V 提高到2.3 V,3 節串聯電池建議提高到6 V,這樣可以容忍更高的放電管漏電流,系統也不會開通內部MOSFET。

5 結論

1)采用先進的晶圓技術及CSP 封裝技術,可以為高容量鋰離子電池包提供小體積、高功率密度的設計,同時滿足熱設計和各種應力的設計要求。

2)功率MOSFET 的高抗雪崩能力、抗短路能力和抗dV/dt 能力才能保證電池包安全可靠的工作。

3)MOSFET 器件表面為金屬材質,用紅外測試儀測量其溫度時必須將其表面涂黑,才能得到正確的測量結果。

4)電池包輸出端并聯電阻或提高控制芯片輸出檢測電壓,可以有效避免漏電流導致電池包不正常工作的問題。

參考文獻:

[1] 李全,劉松,張龍.無人機電池管理充放電MOSFET的選擇[J].電子產品世界,2019(5):69-71.

[2] 劉松,孫國營.快充次級同步整流MOSFET對EMI輻射干擾的影響[J].今日電子,2017(8):32-33.

[3] 劉松.理解功率MOSFET的Rds(on)溫度系數特性[J].今日電子,2009(11):25-26.

[4] 劉松,陳均,林濤.功率MOS管Rds(on)負溫度系數對負載開關設計影響[J].電子技術應用,2010,12(36): 72-74.

[5] 劉松,葛小榮.理解功率MOSFET的UIS及雪崩能量[J].今日電子,2010(4):52-54.

[6] 劉松,張龍,王飛,等.開關電源中功率MOSFET管損壞模式及分析[J].電子技術應用,2013(3): 64-66.

(本文來源于《電子產品世界》雜志2021年12月期)

評論