當人工智能遇到EDA,Cadence Cerebrus以機器學習提升EDA設計效能

隨著算力的不斷提升,人工智能的應用逐漸滲透到各個行業。作為人工智能芯片最關鍵的開發工具EDA,是否也會得到人工智能應用的助力從而更好地提升服務效率呢?答案自然是肯定的。隨著半導體芯片設計的復雜度不斷提升,以及芯片包含功能的日漸廣泛,EDA的設計過程越來越需要借助人工智能來盡可能避免一些常見的設計誤區,并借助大數據的優勢來實現局部電路設計的最優化。在可以預見的未來,隨著人工智能技術的不斷引入,借助大數據和機器學習的優勢,EDA軟件將可以提供更高效更強大的設計輔助功能。

本文引用地址:http://www.j9360.com/article/202110/428670.htm

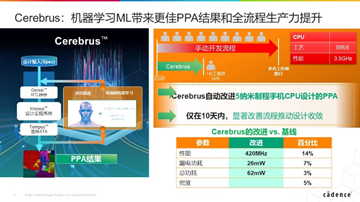

近日,楷登電子(Cadence)宣布推出 Cadence Cerebrus Intelligent Chip Explorer——首款創新的基于機器學習 (ML)的設計工具,可以擴展數字芯片設計流程并使之自動化,讓客戶能夠高效達成要求嚴苛的芯片設計目標。Cerebrus 和 Cadence RTL-to-signoff 流程強強聯合,為高階工藝芯片設計師、CAD 團隊和 IP 開發者提供支持,與人工方法相比,將工程生產力提高多達 10 倍,同時最多可將功耗、性能和面積 (PPA) 結果改善 20%。

如何界定Cerebrus與其他EDA工具的區別,Cadence公司數字與簽核事業部產品工程資深群總監劉淼這樣評價,Cerebrus已經超出了普通的EDA工具,它是凌駕于其他EDA工具之上的,它會用一種全新的全自動學習的工具凌駕于其他EDA工具之上,然后推出來更好結果的技能,這就是Cerebrus想要做的。

Cerebrus 采用可重復使用、可移植的增強學習模型,每次使用均可提高效率;與傳統的人工設計過程相比,可實現更高效的本地和云計算資源管理,特別的,在多個工藝節點和多個終端應用中均可顯著提高 PPA 和生產力,包括消費電子、超大規模計算、5G 通信、汽車電子和移動設備等。基于這些優勢,Cerebrus 可以幫助使用者快速找到工程師可能不會嘗試或探索的流程解決方案,提高 PPA 和生產力;同時允許將設計學習經驗自動應用于未來的設計,縮短獲得更好結果的時間;特別的,Cerebrus提供易于使用的界面和強大的用戶管理工具,支持交互式結果分析和運行管理,以獲得對設計指標的深入了解。此外,Cerebrus還可以讓一位工程師同時為多個區塊自動優化完整的 RTL-to-GDS 流程,提高整個設計團隊的工作效率;另外,提供可擴展的本地或基于云的設計探索,實現更快的流程優化。針對可擴展性,劉淼指出,Cerebrus是基于可分布的、可擴展的計算解決方案,所以它可以用很多計算資源,無論是公有云或者企業的私有云都可以利用起來,利用可利用云的資源完成他的計算。

如果要以通俗點的話來描述Cerebrus,那就是結合Cadence服務過的各個客戶的設計開發經驗作為大數據,匯總反饋到Cadence這邊通過機器學習,可以找到各個細節設計的最優解,然后再反饋并優化新的EDA工具中,最終幫助客戶實現高效的芯片設計。而對Cerebrus的適用范圍,劉淼則指出,無論是身處尚在溫飽階段掙扎的初級設計者,還是對接近小康的資深設計師,亦或是要考慮整個系統級芯片架構的大企業重點項目,都可以從Cerebrus中得到有益的幫助,并且可以大幅縮減從初級設計到資深設計所需要的時間和精力,并能有效提升大規模系統級芯片的設計效率。

隨著 Cerebrus 加入到Cadence廣泛的數字產品系列中,Cadence現在可以提供業界最先進的基于機器學習的數字全流程,從綜合到實現和簽核。這款新工具與多個領先云服務商合作啟用了云計算服務,可利用高度可擴展的計算資源,快速滿足包括消費電子、超大規模計算、5G 通信、汽車和移動等廣泛市場的設計要求。

評論