新型抗總劑量輻照高壓LDMOS結構

馮垚榮(電子科技大學,四川 成都 610054)

本文引用地址:http://www.j9360.com/article/201910/406443.htm摘?要:通過分析低壓MOS中存在的漏電路徑,針對高壓LDMOS面積大,最小寬長比有限制的特點,提出了一種更加適用于高壓LDMOS的新型抗總劑量輻照結構。器件仿真結果顯示,新結構在實現500 krad(Si)的抗輻照能力,并且新結構不會增加面積消耗,與現有工藝完全兼容。

關鍵詞:總劑量效應;高壓LDMOS;抗輻照加固;輻射致漏電路徑

0 引言

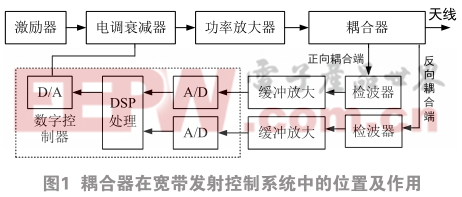

LDMOS(橫向擴散金屬氧化物半導體)相比普通的MOSFET具有高耐壓、高增益等優點,被廣泛應用于各種電源管理電路中。高壓LDMOS在芯片中要占到1/3更多的面積,所以說LDMOS的性能好壞對于電源管理電路至關重要。在太空等特種應用環境中,高能粒子長期作用于MOSFET會使其電特性發生改變,具體表現為閾值電壓漂移,關態漏電流增大,遷移率下降等性能退化。這些改變將顯著影響電子設備的壽命,導致其功耗增大,甚至功能失效,這就是總劑量效應。由于電源電路功能的特殊性,無法像數字電路那樣,采用冗余設計的方法實現抗輻照功能,這就要求電路本身,尤其是LDMOS必須具備抗輻照的功能 [1] 。目前國內外對于LDMOS抗輻照設計的研究,特別是600 V以上的高壓LDMOS的研究還比較少,大多還停留在沿用低壓MOS抗輻照設計方案的階段 [2-3] 。

1 總劑量效應機理及輻照導致的寄生漏電路徑

1.1 總劑量效應的機理簡介

總劑量效應是輻照致電路失效的一種長期機制,它主要作用于MOSFET中的氧化物部分。其機理可以簡述為:高能粒子的轟擊使MOSFET氧化層中產生電子-空穴對,由于電子與空穴遷移率的差異,在偏壓的作用下,電子很快就被掃出氧化層;而空穴則被緩慢的輸運到氧化物/體硅界面,輸運過程中空穴若被氧化物中的空穴陷阱俘獲就會形成氧化層陷阱電荷,隨著輻照總劑量的增加,這些陷阱電荷的數量也越來越多,其最終的結果就是在氧化層內部以及氧化物/體硅界面產生凈的正電荷,導致MOSFET的閾值電壓漂移和關態漏電流增大 [4] 。總劑量效應在MOSFET氧化層的體內和氧化物/體硅界面產生凈的正電荷,因此N型MOSFET對總劑量效應更為敏感,接下來都只討論NMOS中的總劑量效應。

1.2 普通低壓NMOS中的寄生漏電路徑與抗總劑量輻照設計

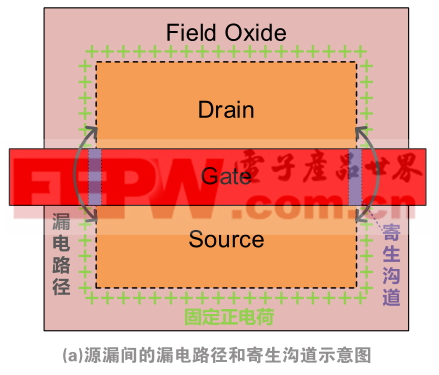

總劑量效應導致MOSFET閾值電壓漂移和關態漏電流增大,其本質是氧化層固定正電荷積累到一定程度,使下方的p型層發生了反型,形成了無法關斷的寄生漏電通路,對于普通低壓NMOS,存在如圖1所示的兩種可能存在的漏電路徑。第一種源漏間的漏電路徑如圖1(a)的箭頭所示,它產生在MOSFET的有源區與場區交界的溝道處,固定電荷導致交界處的溝道反型,形成寄生溝道,當NMOS源漏有偏壓存在時,即使柵壓低于閾值電壓也會有電流產生;第二種晶體管間的漏電路徑如圖1(b)的箭頭所示,它產生在兩個晶體管之間,輻照使場氧失去了隔離作用,在NMOS的源/漏與PMOS的N阱之間形成了寄生導電路徑,PMOS的N阱一般固定接較高的電位,會使漏電一直存在 [4] 。

普通NMOS的抗總劑量設計普遍采用環柵版圖結構,環柵結構將導電溝道與場氧區完全分開,因此完全避免了源漏間漏電通路的產生。環柵結構被證明有著良好的抗總劑量效果 [5-7] ,但是環柵版圖設計也存在著諸如器件面積大,寬長比無法自由選取等缺點。

1.3 高壓LDMOS中的寄生漏電路徑

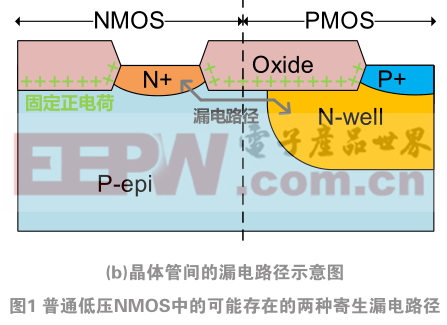

如圖2所示的是一種典型的高壓NLDMOS的剖面圖,比較圖1可以直觀地看出高壓LDMOS與傳統MOS的最大不同在于多出了一個漂移區的結構,這個結構主要起到提升器件耐壓的作用,而就是這個差異給高壓LDMOS的抗總劑量設計帶來了很大不同。高壓LDMOS在電路中要承受600 V甚至更高的電壓,所以漂移區面積必須做得很大,進而導致高壓LDMOS的面積占到這個芯片面積的1/3以上。本身面積巨大,再改為環柵設計,所帶來的成本提升可能無法接受,我們將在后文中分析這個面積提升究竟有多大。

相比低壓MOS,高壓LDMOS還有兩點不同之處:一是LDMOS的柵氧要比低壓MOS厚,因此LDMOS的柵氧對總劑量效應更加敏感,但同時LDMOS的閾值也較低壓MOS高,因此可接受的閾值漂移的量也更大。對于要求較高的設計我們可以采用在柵氧生長時摻氟等工藝來提升柵氧的抗總劑量能力 [8] 。二是高壓LDMOS并不存在上文所述的第二種漏電路徑,為了防止施加在LDMOS上的高壓對相鄰器件造成串擾,會在LDMOS的四周加上一圈P+隔離環,這個隔離環恰好也能起到杜絕管間漏電路徑產生的作用。通過以上的分析我們可知,高壓LDMOS本身的面積已經很大,因此不適合采用傳統的環柵結構實現抗輻照功能,也不存在第二種漏電路徑,所以我們在設計使用與高壓LDMOS的抗輻照結構時,應該著眼于消除源漏間的漏電通路。

1.4 新型抗總劑量輻照高壓LDMOS結構

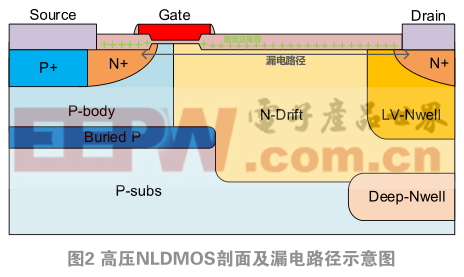

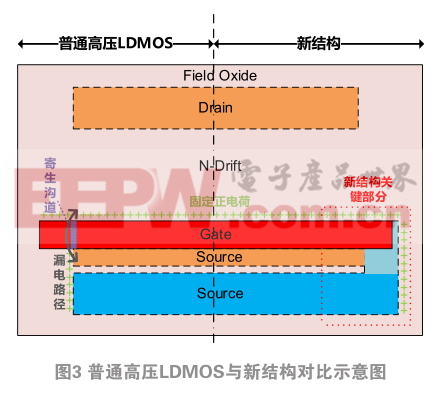

根據前面所做的對比和分析,本文提出了一種新型抗總劑量輻照高壓LDMOS結構,在消除源漏間漏電通路的同時,相比原LDMOS結構面積沒有任何增加。圖3是新型抗總劑量輻照高壓LDMOS結構(以下簡稱新結構)與普通高壓LDMOS結構的對比圖,從圖中可以看到,新結構將傳統LDMOS的有源區和P-body的P+接觸向外延長。向外延長的有源區使得場氧遠離LDMOS的溝道區,多出的P+摻雜區域向外橫向擴散,使得同等輻照劑量下場氧下的襯底不發生反型,從而避免了源漏間漏電通路的產生。

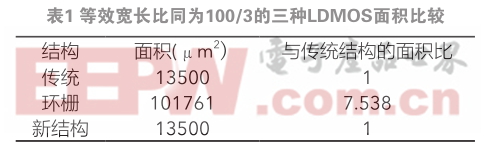

表1列出了相同等效寬長比條件下,傳統、環柵結構和新型結構高壓LDMOS的面積比較。三種結構的面積均是參考國內某高壓BCD工藝平臺的設計規則給出,其中環柵等效寬長比計算用的是(W 1 +W 2 )/2的公式 [9] ,從表中可以看出環柵結構的面積是其他兩種結構面積的7.5倍多,前面提到高壓LDMOS在芯片中占到芯片總面積的1/3以上,照這個比例估算,如果采用環柵結構,芯片面積會在傳統設計的基礎上增加218%,這會大大增加電路的成本,甚至可能導致芯片無法采用原本的封裝方案。反觀新結構就完全不存在這方面的問題,新結構相比傳統LDMOS結構,面積完全沒有增加,而且不增加新的掩膜版,可以與現有的工藝完全兼容,不改變原有器件的耐壓結構,不會造成生產成本的增加。

2 新結構抗輻照能力仿真驗證

2.1 仿真策略

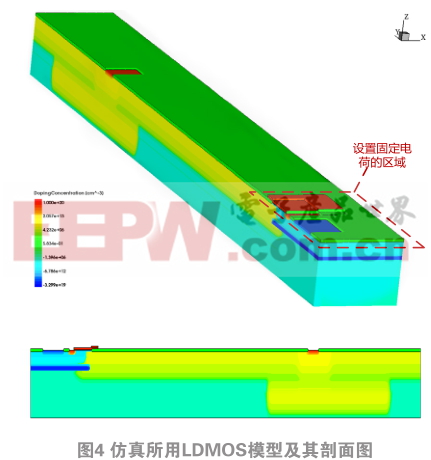

本文通過Synopsys公司的Sentaurus TCAD軟件對新結構的抗輻照功能進行仿真驗證,使用軟件自帶的Insulator Fixed Charge模型,在材料交界面設置固定正電荷來模擬總劑量效應對MOSFET的作用,該仿真方法已經被很多報道采用并驗證過其可行性 [10-11] 。要驗證新結構是否確實能夠消除源漏間漏電路徑,必須進行3D仿真,3D仿真本身計算量很大,加之LDMOS相比普通MOS尺寸巨大,經過多次嘗試發現無法同時對整個LDMOS總劑量仿真。最終只選取LDMOS中受輻照影響會產生漏電通路的關鍵部分來進行仿真,如圖4所示的就是本文最終建立的LDMOS仿真模型,從剖面圖可以看到其仍然包含LDMOS的所有關鍵結構,因此不影響仿真結果的可信度。同樣出于減小計算量的考慮,我們只在圖4虛線框所示區域的Oxide/Si界面中加入固定電荷。固定電荷的密度參考文獻 [12] ,其通過將仿真結果與實驗對比得知,2.93×1012/cm 2 的固定正電荷密度相當于劑量為300 krad(Si)的γ射線輻照;3.26×1012/cm 2的固定正電荷密度相當于劑量500 krad(Si)的γ射線輻照。本文仿真時共設置了8個不同固定電荷面密度,其中3.5×10 10 /cm 2 的密度用以表征器件出廠自帶的正電荷,即未受輻照的情況,然后從0.5×10 12 /cm 2 開始,每隔0.5×10 12 /cm 2 的步長進行一次仿真,一直仿真到3.5×10 12 /cm 2 的面密度,確保仿真所施加的最大劑量高于500 krad(Si),而且可以觀察隨著劑量的增加,器件的性能是如何變化的。

2.2 仿真結果及分析

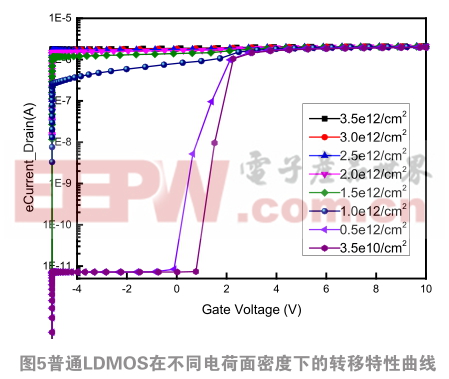

如圖5所示的是普通高壓LDMOS在不同電荷面密度下的轉移特性曲線的仿真結果,仿真施加的偏置條件為,Vds=0.1 V,Vb=Vs=0 V,Vg從-4 V掃描到10 V。從仿真結果我們可以看到隨著電荷密度的增加,LDMOS的關態漏電流也隨之增加,而且閾值電壓也隨之發生負向漂移,這與我們之前提到的源漏間漏電通路會同時造成關態漏電流增加和閾值電壓漂移的推論一致。未經輻照加固設計的高壓LDMOS對總劑量效應相當敏感,僅在1.0×10 12 /cm 2 的電荷密度就表現出了明顯的漏電流增加,可見未加固的LDMOS其抗輻照能力遠低于50 krad(Si)。而固定電荷密度增加到2.0×10 12 /cm 2以上時,關態漏電流幾乎已經與開態電流相當,此時器件已經無法關閉完全失去功能。

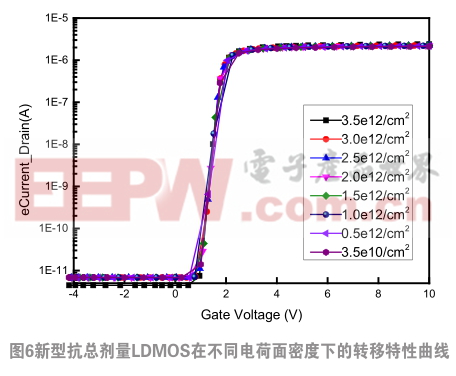

如圖6所示的是本文提出的新型抗總劑量LDMOS在不同電荷面密度下的轉移特性曲線的仿真結果,仿真施加的偏置條件與普通LDMOS相同。從仿真結果我們可以看到,隨著電荷密度的增加,LDMOS的關態漏電流沒有明顯變化,閾值電壓也沒有發生漂移,8條轉移特性曲線幾乎重合到了一起。說明本文提出的新結構很好地消除了源漏間的漏電路徑,加入抗輻照設計之后,LDMOS的抗輻照能力達到了500 krad(Si)以上。

3 結論

本文結合對普通MOS總劑量效應的研究,分析了高壓LDMOS與普通MOS在抗輻照設計方面的差異,提出了一種更加適用于高壓LDMOS新型抗總劑量結構,相比環柵結構,其不增加器件版圖面積,不改變器件耐壓,寬長比可以按照普通LDMOS的規則選取,而且與現有的工藝完全兼容。通過仿真驗證,新結構確實可以有效地消除LDMOS中的漏電路徑,實現 500 krad(Si)

以上的抗輻照能力。

參考文獻

[1]NAGORNOV A, TIMOSHENKOV V. Dependence of HVMOS transistor I-V characteristics from total ionizing doseeffects. 2018 IEEE Conference of Russian Young Researchers inElectrical and Electronic Engineering (EIConRus), 2018, 1996-1999.

[2]王丹輝,趙元富,岳素格,等.高壓LDMOS總劑量輻射效應研究[J].微電子學與計算機,2015,32(10):82-86.

[3]DODD P E, SHANEYFELT M R, DRAPER B L, et al.Developmentof a Radiation-Hardened Lateral Power MOSFET for POLApplications. IEEE Trans. Nucl. Sci., 2009,56:3456-3462.

[4]SCHWANK J R, SHANEYFELT M R, FLEETWOOD D M, et al.Radiation Effects in MOS Oxides. IEEE Transactions on NuclearScience,2008,55(4).

[5]范雪,李威,李平,等.基于環形柵和半環形柵N溝道金屬氧化物半導體晶體管的總劑量輻射效應研究[J].物理學報,2012,61(01):318-323.

[6]FACCIO F, CERVELLI G. Radiation-induced edge effectsin deepsubmicron CMOS transistors. IEEE Trans. Nucl. Sci.,2005,52(6): 2413 –2420.

[7]FACCIO F. “Design hardening methodologies for ASICs”in Radiation Effects on Embedded Systems. New York:Springer-Verlag,2007: 143-160,.

[8]譚開洲. MOS器件總劑量輻射加固技術研究[D].成都:電子科技大學, 2001.

[9]楊變霞. 封閉形柵NMOS晶體管的設計與器件特性研究[D].成都:電子科技大學, 2015.

[10]李念龍,于奇,王凱,等. MOS結構γ總劑量效應仿真模型研究[J].微電子學,2013,43(03):445-448.

[11]Roh Y T, Lee H C. TID and SEE hardened n-MOSFET layouton a bulk silicon substrate which combines a DGA n-MOSFETand a guard drain. 2015 IEEE Nuclear Science Symposium andMedical Imaging Conference,1-4.2015.

[12]Lee M S, Lee H C.cDummy Gate-Assisted n-MOSFET Layoutfor a Radiation-Tolerant Integrated Circuit. IEEE Trans. Nucl. Sci.,2013,60(4):3084-3091.

本文來源于科技期刊《電子產品世界》2019年第11期第58頁,歡迎您寫論文時引用,并注明出處。

評論