臺積電:3nm工藝進展順利 已有客戶參與

如今在半導體工藝上,臺積電一直十分激進,7nm EUV工藝已經量產,5nm馬上就來,3nm也不遠了。

本文引用地址:http://www.j9360.com/article/201907/403055.htm臺積電CEO兼聯席主席蔡力行(C.C. Wei)在投資者與分析師會議上透露,臺積電的N3 3nm工藝技術研發非常順利,已經有早期客戶參與進來,與臺積電一起進行技術定義,3nm將在未來進一步深化臺積電的領導地位。

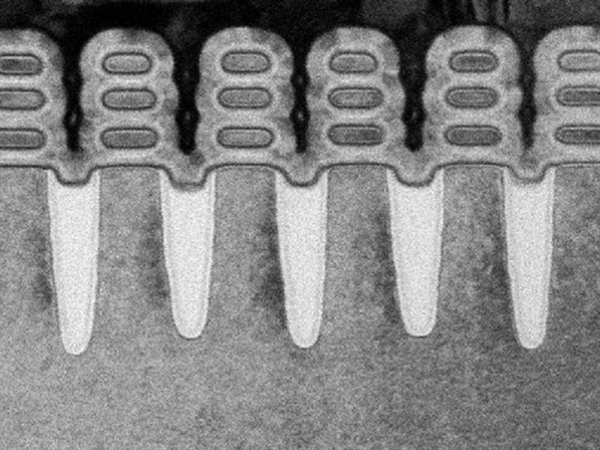

目前,3nm工藝仍在早期研發階段,臺積電也沒有給出任何技術細節,以及性能、功耗指標,比如相比5nm工藝能提升多少,只是說3nm將是一個全新的工藝節點,而不是5nm的改進版。

臺積電只是說,已經評估了3nm工藝所有可能的晶體管結構設計,并與客戶一起得到了非常好的解決方案,具體規范正在進一步開發中,公司有信心滿足大客戶們的所有要求。

三星此前曾披露,將在3nm工藝上采用基于納米片(nano-sheet)的環繞式柵極(Gate-All-Around) MBCFET晶體管結構,工藝節點簡稱3GAAE。

考慮到臺積電必須在新工藝上保持足夠的競爭力,而且強調過3nm是全新的,所以必然也會有新的架構、技術、材料等。

另外,臺積電5nm工藝使用了14個EUV極紫外光刻層,3nm上應該會使用更多,但仍可能繼續保留DUV深紫外光刻技術,混合使用。

臺積電此前曾披露,計劃在2022年就量產3nm工藝。

評論