LDO設計中的盲區:負載調整率

傳統的DC-DC一般要求輸入輸出的壓差在2~3V以上,隨著時代的發展,這樣的條件已經不能滿足實際應用的需要。例如在無線通信領域,GPRS模塊常用到的電壓是4V,經常是通過5V轉換而來,輸入輸出的壓差需低至1V。針對這樣的情況,于是LDO(Low dropout regulator)應運而生。

本文引用地址:http://www.j9360.com/article/201812/396199.htm相對DC-DC而言,LDO的優點是噪音低,靜態電流小。很多DC-DC在外圍電路里還需要有電感和續流二極管,而LDO的典型電路非常簡單,很多LDO只需在輸入端及輸出端各接一顆旁路電容就能夠穩定工作,對于節省PCB的布局空間也很有優勢。Ricoh推出的很多LDO,還具有如負載短路保護、過壓關斷、過熱關斷、反接保護等其它的功能。

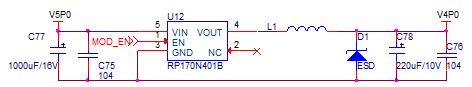

很多硬件工程師在LDO的應用中主要考慮輸入電壓范圍,輸出電壓和電流、壓差、紋波、功耗、靜態電流等,然而往往會忽略一個很重要的參數:負載調整率。本文就筆者在應用Ricoh的RP170N401B時由于忽視了負載調整率而來帶的問題,并最終通過改進設計得到解決的過程,分享自己的一些經驗。

問題描述

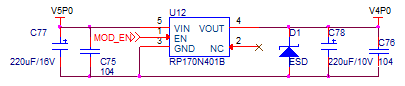

筆者的電路如圖1所示,系統12V轉為5V,5V轉換成3.3V和4V分別供MCU和通信模塊。由于通信模塊是定時打開和關閉的,使用中發現只要U12(RP170N401B)的使能腳為低電平,系統就能正常工作,在MOD_EN拉高時,整個系統則被復位。

圖1:筆者設計的最初版原理圖

問題分析

筆者最初是懷疑4V后端的電路短路,導致5V電源被拉底,但由于6臺樣機均會發生這個問題,4V短路的可能性被排除。實際上在電路中還有看門狗兼電源監控的設計,如圖2所示,問題就發生在這里,其中的PW_EN腳直接控制5V轉3.3V的LDO芯片。

圖2:看門狗電路

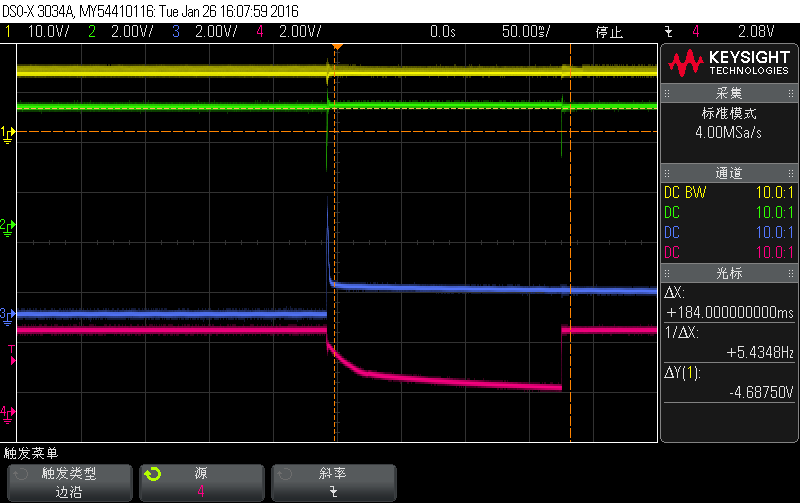

筆者首先測量了系統各個電源在MOD_EN被拉高時的波形,得到波形如圖3所示。

圖3:系統各電源波形

波形分析:圖中從上至下依次為12V、5V、4V、3.3V波形,圖中3.3V被拉低了184ms,需要進一步看一下5V和4V電源線上的尖峰細節。將以上波形進行放大后,得到如圖4所示波形圖。

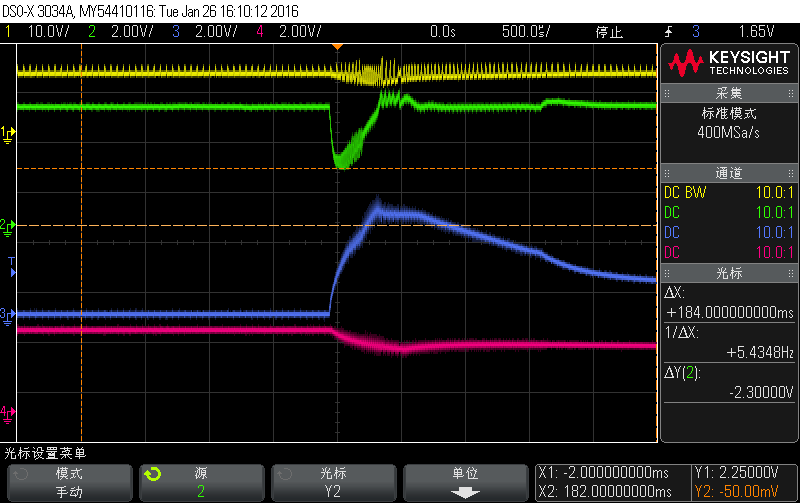

圖4:系統各電源波形放大

波形分析:圖中從上至下依次為12V、5V、4V、3.3V波形細節。圖中5V電壓被拉至2.3V,此電壓低于2.63V時706會輸出200mS復位信號。實測時間184mS,在測量的誤差范圍內,與706的電源監控復位時間相近,可繼續監測706的復位信號,得到如圖5、6所示波形。

圖5:看門狗706的復位信號

波形分析:圖中從上至下依次為12V、5V、4V、PW_EN波形細節。4V跳變的瞬間,RST輸出了低電平復位信號,將5V轉3.3V的LDO使能腳拉底。

圖6:復位波形細節

波形分析:在5V跌落后回升至3V前,看門狗706即輸出了低電平復位信號,且復位信號分兩段,在電源電壓2.65V前后出現拐點,拐點前的跌落波形是隨5V電源電壓同步跌落;而拐點后的下降波形是看門狗芯片706監測到電源電壓低于2.63V輸出的復位信號。

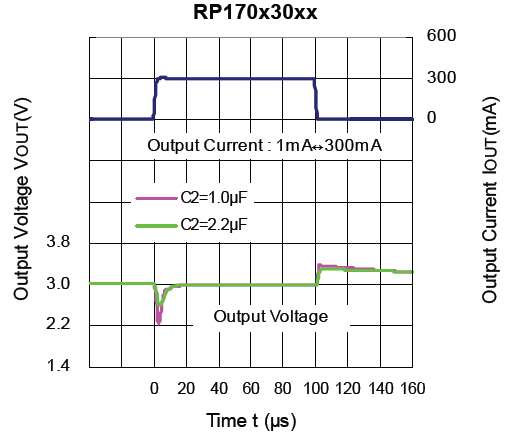

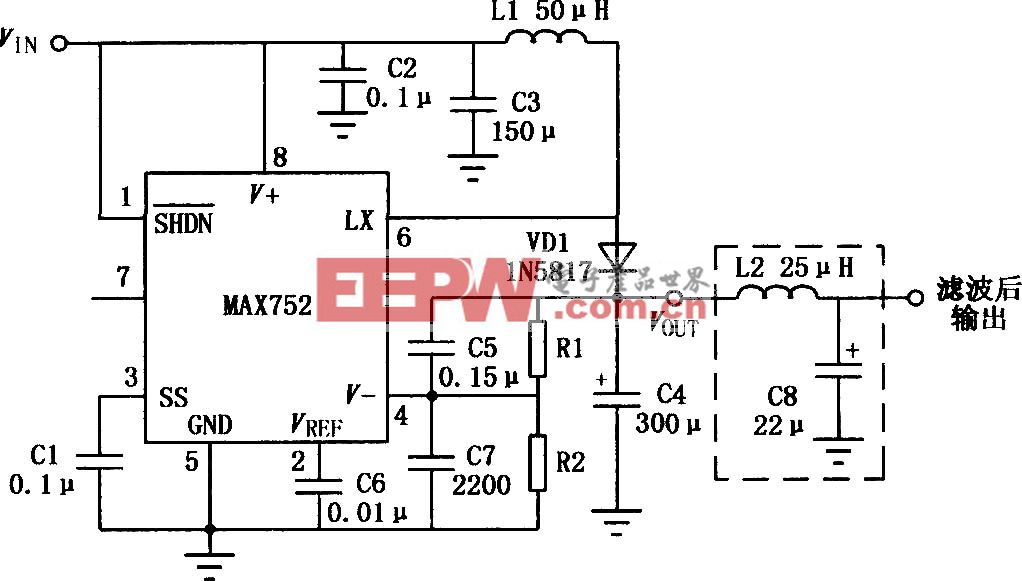

圖7:RP170N401B手冊上的負載調整率

通過查看RP170N401B的器件手冊,發現其在負載突然變大時,輸出電壓由于不能及時調整而有瞬間的跌落。對應到系統中,在使能4V電源LDO使能端的瞬間,因LDO后端有負載,瞬間電流的沖擊,使得LDO輸入和輸出均有一定瞬間壓降,系統把12V拉低至9.6V,更嚴重的是在50us內把5V電平拉低至2.6V以下,4.7V拉低到2.6V以下,引起電源監控芯片706輸出復位信號,從而導致文頭所述系統重啟現象。

改進方案

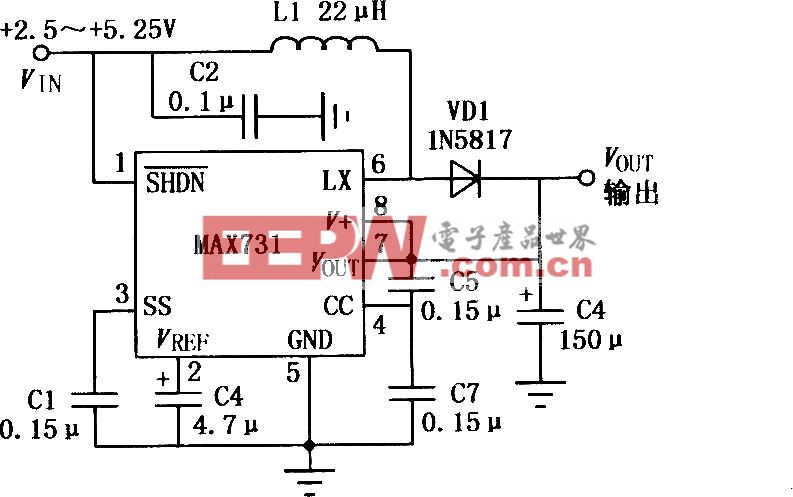

從圖7可見,當調整LDO輸出的電容值時,其電壓跌落也會變得平緩,同時采取了以下兩個辦法:

1)LDO輸出串聯電感,通過電感的飽和電流來抑制芯片啟動時的瞬態大電流。

2)調整LDO輸入輸出兩端的電容的拓撲結構,通過電容儲能來消除跌落。

圖8:改進后的電路

LDO的負載變化率也是十分重要的參數,這往往也是設計中的一個盲區。最終筆者的電路如圖8所示,增加了電感L1,C77調整到1000uF,重啟的現象也成功解決。

經驗總結

在LDO芯片的應用中,負載調整率也是一個很重要的參數,在新產品設計的選型之初就應當重視這個參數。對老產品已經使用的芯片,當其負載調整率不能滿足實際使用的要求時,通過控制后端負載電路的瞬間功率、調整LDO級聯的拓撲結構等方法,可以使得電源設計滿足系統要求,從而使產品穩定可靠地運行。

評論