組合邏輯電路原理概述及作用分析

組合邏輯電路概述:

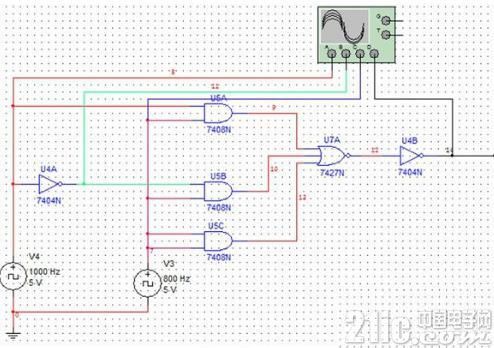

本文引用地址:http://www.j9360.com/article/201809/389121.htm數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。而時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當時的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

1.半加器與全加器

①半加器

兩個數A、B相加,只求本位之和,暫不管低位送來的進位數,稱之為“半加”。

完成半加功能的邏輯電路叫半加器。實際作二進制加法時,兩個加數一般都不會是一位,因而不考慮低位進位的半加器是不能解決問題的 。

②全加器

兩數相加,不僅考慮本位之和,而且也考慮低位來的進位數,稱為“全加”。實現這一功能的邏輯電路叫全加器 。

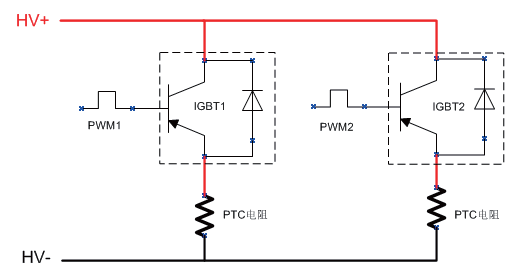

2.加法器

實現多位二進制數相加的電路稱為加法器。根據進位方式不同,有串行進位加法器和超前進位加法器兩種 。

①四位串行加法器:如T692。優點:電路簡單、連接方便。缺點:運算速度不高。最高位的計算,必須等到所有低位依此運算結束,送來進位信號之后才能進行。為了提高運算速度,可以采用超前進位方式 。

②超前進位加法器:所謂超前進位,就是在作加法運算時,各位數的進位信號由輸入的二進制數直接產生 。

1.基本概念

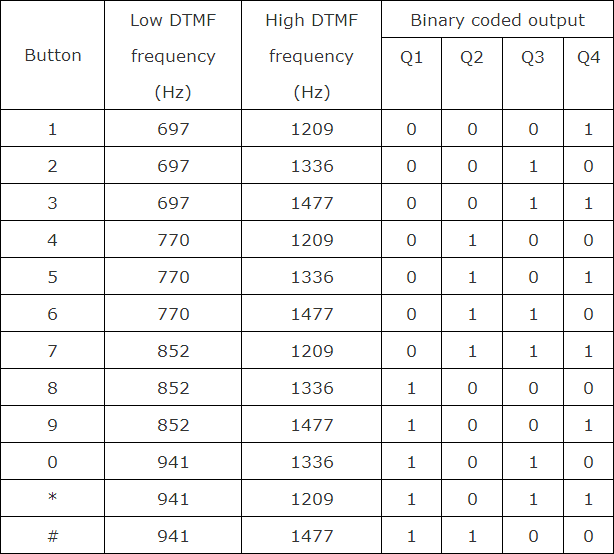

用代碼表示特定信號的過程叫編碼;實現編碼功能的邏輯電路叫編碼器。編碼器的輸入是被編碼的信號,輸出是與輸入信號對應的一組二進制代碼 。

2.普通編碼器

①三位二進制編碼器:二進制編碼器:用n位二進制代碼時,對m=2n個一般信號進行編碼的電路 。

②二M十進制編碼器:把0~9十個十進制數字編成二進制代碼的電路。n位二進制代碼共有2n種,可以對m≤2n個信號進行編碼。因二M十進制編碼器的輸入是十個十進制數,故應使用四位二進制代碼表示制。從2n=16種二進制代碼中取十種來代表0~9這是個十進制數碼,方案很多,最常用的是8421BCD碼。在二M十進制編碼器中,代表0~9的輸入信號也是互相排斥的,其工作原理及設計過程與三位二進制編碼器完全相同,不再重復 。

3.優先編碼器

定義:允許若干信號同時輸入,但只對其中優先級別最高的信號進行編碼,而不理睬級別低的信號,這樣的電路叫優先編碼器 。

1)基本概念

定義:把二進制代碼按照愿意轉換相應輸出信號的過程叫譯碼。完成譯碼功能的邏輯電路叫譯碼器。譯碼器的n個輸入,m個輸出應滿足2n≥m。譯碼器有二進制譯碼器、二—十進制譯碼器、數字顯示譯碼器等類型 。

2)二進制譯碼器

把二進制代碼的各種狀態,按照其原意轉換成對應的信號的輸出。這種電路叫二進制譯碼器。在二進制譯碼器中,若輸入代碼有n位,則輸出信號就是2n個。因此它可以譯出輸入變量的全部狀態。(有時又稱為變量譯碼器,或最小項產生器 。

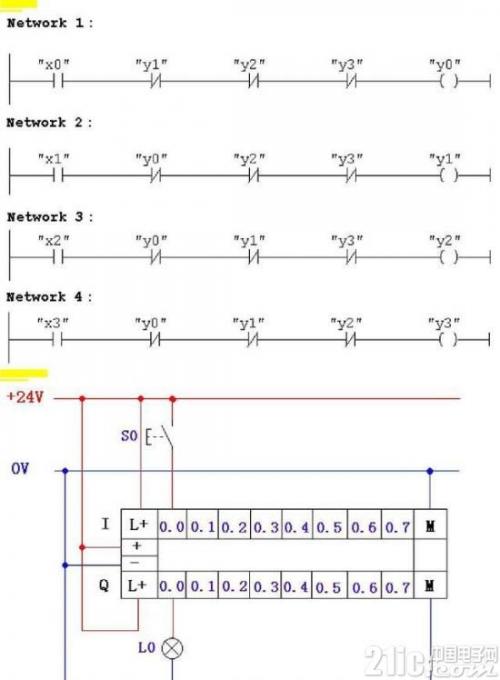

1.數據分配器的邏輯功能

數據分配器(Demulplexer)又稱為多路分配器,它只有一個數據輸入端,但有2n個數據輸出端。根據n個選擇輸入的不同組合,把數據送到2n個數據輸出端中的某一個。從其作用看,與多位開關很相似,從邏輯功能看,與數據選擇器恰好相反 。

2.用譯碼器作數據分配器

凡是帶使能控制端的譯碼器都能作數據分配器使用 。

3.多路信號分時傳送

數據選擇器和數據分配器結合,可以實現多路信號的分時傳送。原理:選擇輸入C2C1C0=001時,數據選擇器是把XIN1的狀態送到輸出端。對數據分配器而言,則是把送來的XIN1分配到XOUT1端。各路信號不是同時傳送,但傳輸線減少了 。

1.1位數值比較器

兩個1位二進制數比較時,有4種可能,3種結果

2.多位數值比較器

設:A=A3A2A1A0,B=B3B2B1B0

用li =1,表示Ai>Bi;

mi =1,表示Ai

gi =1,表示Ai=Bi。

比較時,應從高開始,若高位比出結果,則低位不用再比。當高位相等時,再去比較低位 。

評論