積分梳狀濾波器的FPGA實現

1 CIC濾波器結構分析

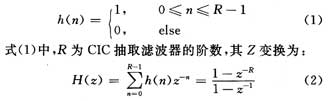

本文引用地址:http://www.j9360.com/article/201809/389015.htmCIC濾波器最早是由Hogenauer提出的,后來出現了不少改進的結構形式。最基本的CIC抽取濾波器是指該濾波器的沖激響應具有如下形式:

|

|

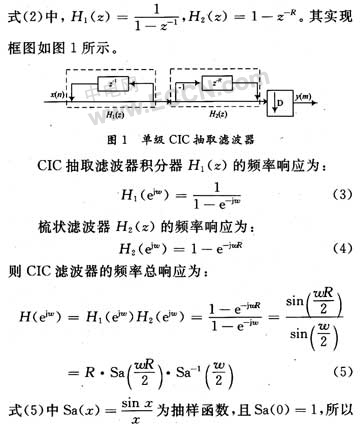

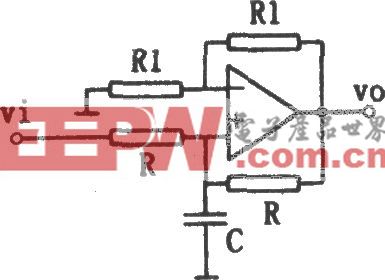

CIC抽取濾波器在w=0處的幅度值為R,其幅頻特性如圖2所示。稱頻率區間0~2π/R為CIC濾波器的主瓣,而其他區間為旁瓣。由圖2可以看見隨著頻率的增大,旁瓣電平不斷減小,其中第一旁瓣電平為:

|

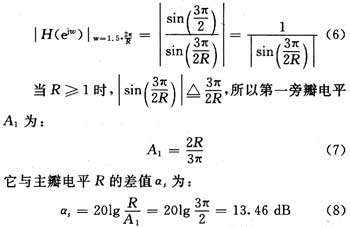

可見單級CIC濾波器的旁瓣電平比較大,只比主瓣低13.46 dB,說明阻帶衰減很差,一般很難滿足實用要求。為了降低旁瓣電平,可以采用多級CIC濾波器級聯的辦法來解決。

|

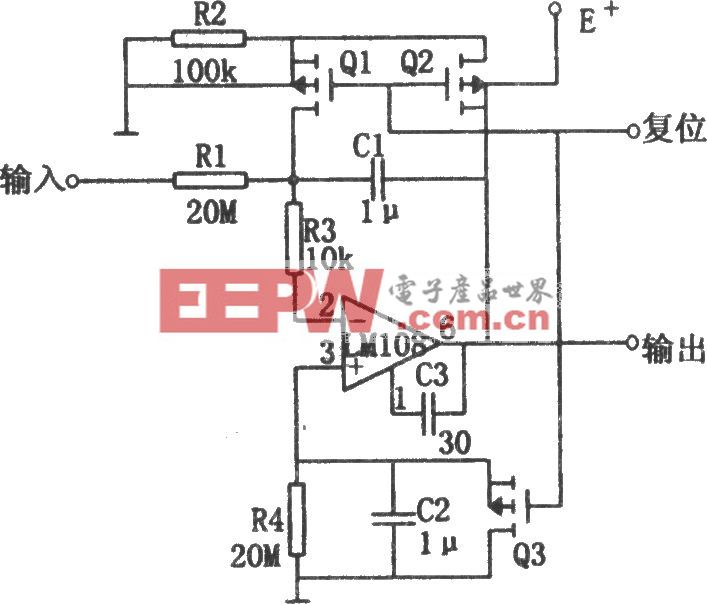

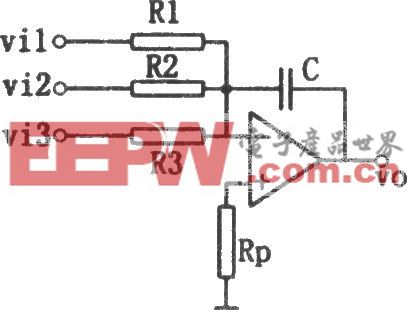

當Q=5時,QQS=67.3 dB,由此可見5級級聯的CIC濾波器具有67 dB左右的阻帶衰減,基本能滿足實際要求。實際應用的CIC抽取濾波器常采用多級結構來實現。由此可見實際應用中采用多級CIC抽取濾波器能適用更寬的有用輸入信號。適用于軟件無線電系統中的CIC抽取/內插濾波器如圖3所示,通常R的取值為1或2。

2 五級CIC濾波器的FPGA實現

在此設計的CIC抽取濾波器的參數為:抽取因子D=25,帶寬比例因子b=1/8,R=1的5級CIC濾波器。設輸入數據位寬為8 b,輸出數據位寬為10 b。

|

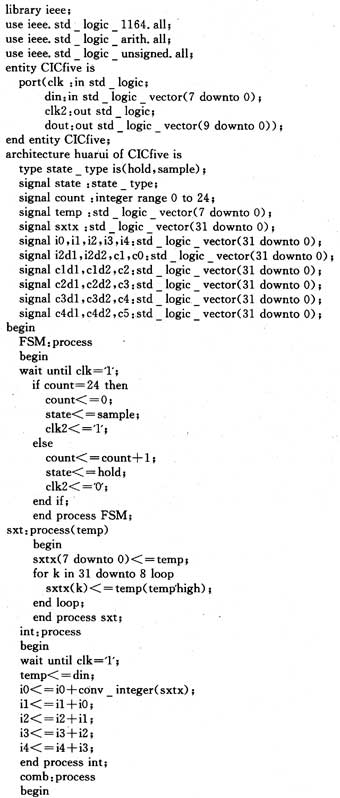

實現的VHDL代碼如下所示:

|

|

3 仿真分析

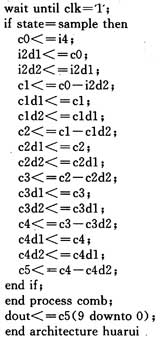

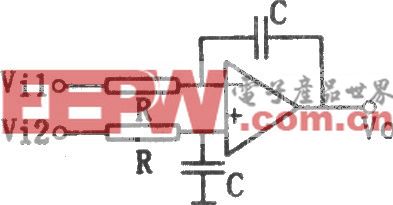

利用Altera公司的Quartus Ⅱ軟件,針對Cyclone系列的EP1C12Q24017,對CIC濾波器的實現方法進行仿真分析,所得時序圖如圖4所示。仿真結果表明5級CIC濾波器的實現方法正確。

|

4 結論

本文給出了適用于軟件無線電采樣率變換系統中CIC濾波器的結構,完成了5級CIC濾波器的具體設計,時序仿真分析證明了該濾波器的正確性和可行性。該多級CIC濾波器的FPGA實現方法可在其他多速率處理系統中推廣應用。

評論