一種信道化測頻接收機的工程實現

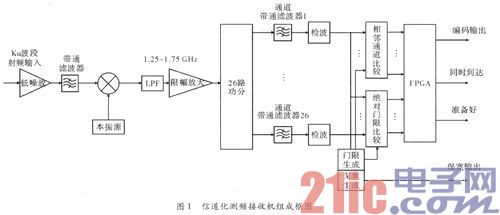

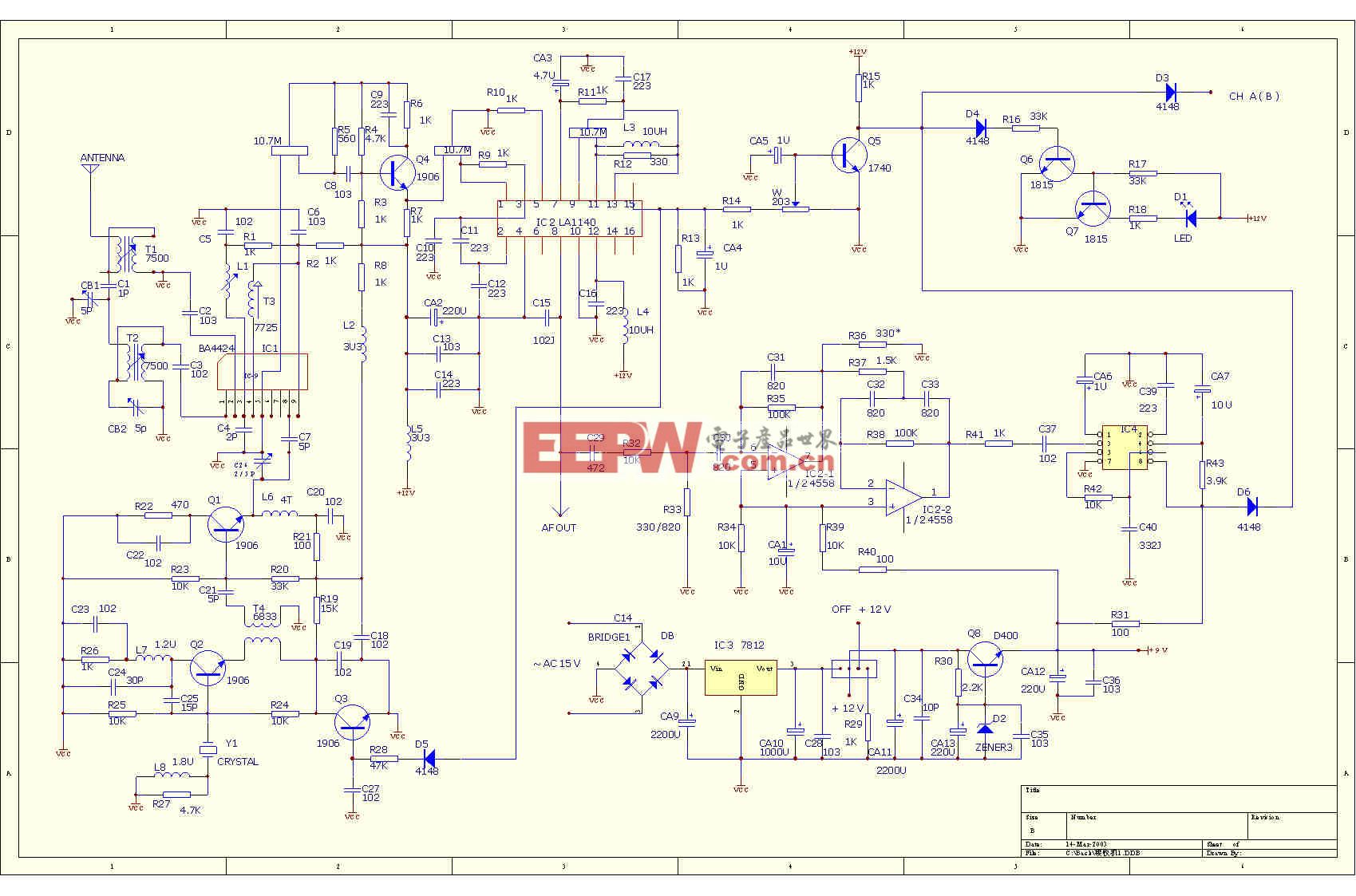

摘要 將Ku波段射頻信號下變頻為1.25~1.75 GHz的中頻信號,經26路功分器功分為26路信號,每路經過相互交疊的帶通濾波器和檢波器,當頻率位于某個通道的濾波器內時,該通道檢波器輸出對應檢波電壓,將該檢波電壓與相鄰通道檢波電壓和絕對電平進行比較,并將比較結果送入FPGA,由FPGA進行判斷、編碼,輸出對應的頻率編碼、同時到達信號,準備好指示等。

本文引用地址:http://www.j9360.com/article/201809/388282.htm測頻接收機在武器裝備中得到廣泛應用,根據測頻的體制不同,分為信道化測頻、鑒頻法瞬時測頻、比相法瞬時測頻和計數法測頻等多種形式。其中,信道化測頻接收機動態范圍寬、測頻速度快、可處理同時到達信號等優點,故得到了廣泛應用。本文以一個實用化的工程產品為例,介紹信道化接收機的功能原理、組成及實現,最后給出了達到的技術指標及不足。

1 功能原理及組成

信道化測頻機的基本原理是利用多路功分器進行功分,輸出多路信號,每路信號經窄帶濾波器進行濾波,若信號落在該濾波器帶內,則該通道輸出功率較大,若信號未落在該通道內,則該通道無輸出信號或信號較小,然后由FPGA對各通道的功率狀態進行判斷,從而實現對輸入頻率的識別和編碼輸出。

本文介紹的信道化接收機完成對Ku波段射頻信號的頻率測量,給出了測頻碼、同時到達脈沖、準備好信號、保寬脈沖等,如圖1所示。

需測頻的Ku波段射頻信號首先經低噪聲放大器放大、帶通濾波器濾波,之后進入混頻器混頻輸出1.25~1.75 GHz的中頻信號。對該中頻信號進行限幅、放大后經26路功分器進行功分,并輸出26路中頻信號。每路中頻信號經30 MHz的帶通濾波器濾波后進行功率檢波,檢波輸出送往:(1)相鄰通道比較,實現與該通道的前一通道和后一通道的相對比較;(2)絕對門限比較,該通道檢波輸出與絕對門限進行比較,若大于門限電平輸出高電平,否則輸出低電平;(3)門限生成和保寬生成電路,實現比較門限的生成和保寬脈沖的生成。

為提高測頻精度,采用濾波器帶寬30 MHz,相鄰濾波器交疊10 MHz,最終可實現10 MHz的測頻精度。中頻頻率采用1.25~1.75 GHz,原因是由于該頻段可采用介質濾波器實現,其指標好、體積較小。

2 功能實現

2.1 編碼的設計

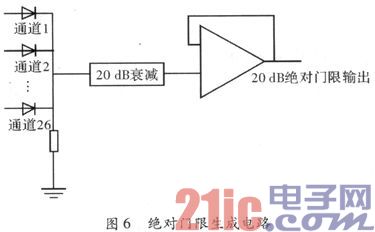

編碼分為相鄰通道比較輸出和絕對門限比較輸出兩部分。相鄰通道比較輸出是將每一通道與該通道的上一個和下一個通道分別進行比較輸出;絕對門限比較輸出是將每一個通道與最大電平經20 dB衰減后形成的門限進行比較,用于濾除小于門限的功率。每個通道經比較后的3個輸出均送給FPGA,并由FPGA進行邏輯判斷,同時進行編碼輸出。

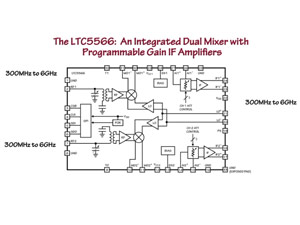

2.2 檢波的實現

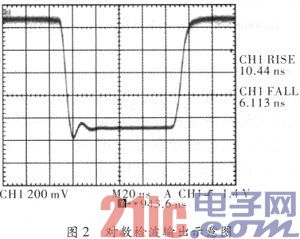

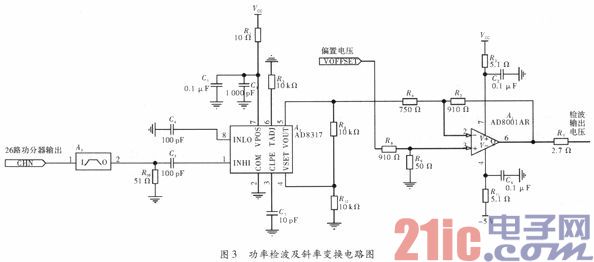

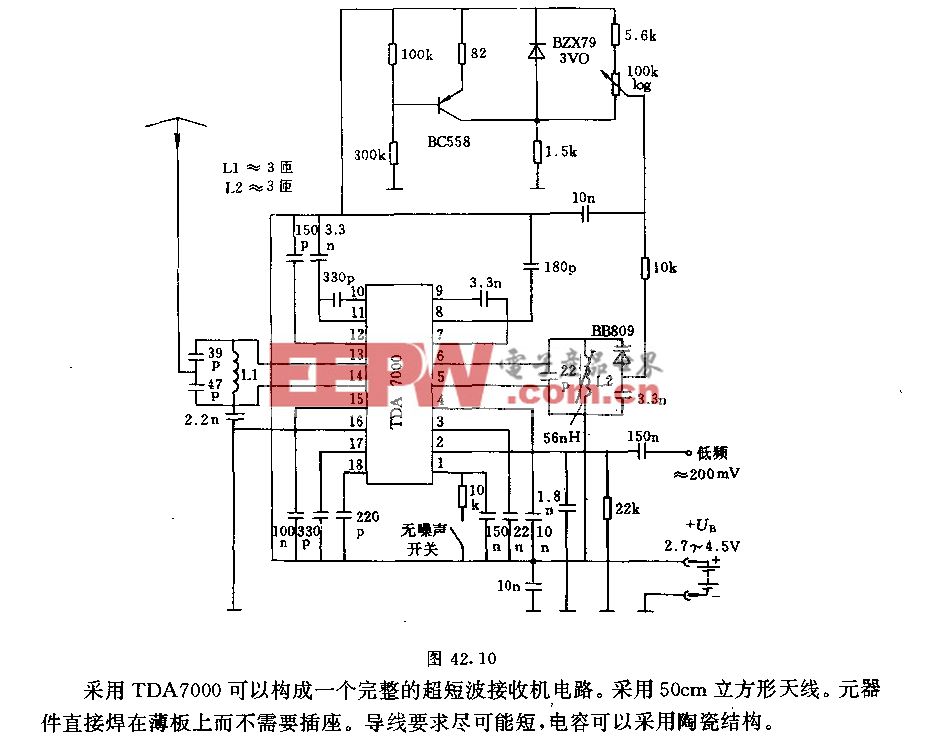

檢波采用AD公司的AD8317ACPZ對數檢波器實現。該檢波器使用頻率為10 MHz~10 CHz,3 dB動態范圍55 dB,脈沖上升/下降時間為6 ns/10 ns,電源電流22 mA,檢波視頻帶寬50 MHz,其典型檢波曲線如圖2所示。該檢波器相應速度快、動態范圍寬、功耗低,適用于測頻接收機中用作功率檢波。該檢波器為負斜率輸出,需采用外部運放將負斜率變換為正斜率輸出。圖3為檢波及斜率變換電路圖,功分后的射頻信號經A3帶通介質濾波器后進入A2檢波器進行檢波,檢波后的信號通過運放A1將負斜率轉換為正斜率信號,隨后送到比較器進行相鄰通道比較和絕對電平比較。

2.3 相鄰通道比較及絕對門限比較實現

如圖4所示。第N通道的檢波電壓送到兩個比較器的輸入端,與N-1通道和N+1通道的檢波電壓進行比較,輸出的兩個比較電平送到FPGA,輸出高電平表示N通道功率比相鄰通道的功率高。為保證相鄰通道比較的唯一性,N通道與相鄰通道比較時,會增加一個小的電壓△V,確保唯一性。

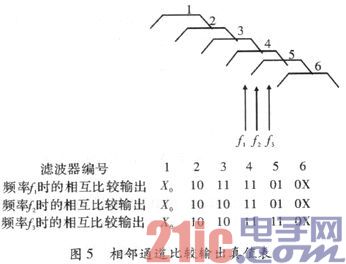

圖5為相鄰通道比較輸出真值表示意圖,圖中濾波器1~6帶寬30 MHz、相互交疊10 MHz,當頻率為f1、f2、f3分別位于濾波器4通帶內左側、中心、右側時,給出了濾波器相鄰通道比較輸出的真值表。

該檢波電壓同時與絕對門限電平比較,若大于絕對門限,則輸出高電平,否則輸出低電平。

2.4 門限電平的實現

門限電平用于絕對比較,該電平是將26個通道檢波進行“或”操作,找到最大的檢波電壓,然后將該電壓進行20 dB衰減,并送至絕對比較電路用作絕對比較電平,如圖6所示。

2.5 保寬脈沖的實現

實際應用中,信號功率較大時,經后續濾波器濾波,檢波器輸出的視頻信號存在較嚴重的“兔耳效應”和拖尾現象,此時保寬脈沖失真較為嚴重。為得到滿足指標的保寬脈沖,根據信號的大小采用不同位置、不同比較電平進行視頻電平的比較,從而較好地滿足了該指標的要求。

在26路功分器前設置一個功率檢波器,判斷大小信號并輸出大信號時的整形輸出。26路功分器后設置比較器對各檢波器“或”信號進行比較,輸出小信號時的整形輸出。

大小信號標志、大信號保寬脈沖、小信號保寬脈沖均送到FPGA,由FPGA進行判斷,輸出合適的保寬脈沖。如圖7所示。

2.6 FPGA的實現

FPGA采用Xilinx公司的XC3S200-4PQ208I,該FPGA規模為200百萬門,內部有4 320個等效邏輯單元,480個CLB,141個用戶IO口。采用ISE操作環境,用VHDL語言進行程序編寫。FPGA主要完成對26個通道的相互比較電平和絕對比較電平的采集,同時對這些電平進行分析與判斷并生成對應的頻率編碼;對是否存在同時到達信號進行判斷并給出指示。對信號大小進行判斷,并進行保寬脈沖的選擇輸出。

3 達到的技術指標

圖8為信道化測頻接收機編碼一側布局及外形。達到的主要技術指標為:測頻頻率為Ku波段;測頻帶寬為500MHz;測頻誤差為10MHz;測頻時間為150 ns;動態范圍為>65 dB。具有同時到達、頻率準備好、保寬脈沖輸出等功能。重量為1.6kg。

4 結束語

產品經高低溫試驗及隨機振動試驗,達到了預期的設計指標。該類型信道化測頻機主要優點是:測頻速度快、動態范圍寬,具有同時到達的識別功能等。但也存在不足,例如:體積及重量較大;存在著“兔耳效應”,使得同時到達信號的功率差不能過大等。

評論