基于FPGA的等效時間采樣原理的實現

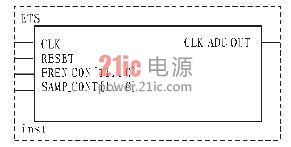

圖3等效時間采樣模塊圖

以下是實現等效時間采樣所需時鐘的代碼:

SIGNAL SAMP_CONTS:STD_LOGIC_VECTOR(11

DOWNTO 0):=(OTHERS=>'0');

SIGNAL ADC_CLK_BANK:STD_LOGIC_VECTOR(11

DOWNTO 0):=(OTHERS=>'0');

SIGNAL CLK_CNT :INTEGER RANGE 0 TO 5000:=0;

SIGNAL CLK_TANK:STD_LOGIC:='0';

SIGNAL EN :STD_LOGIC:='1';

BEGIN

PROCESS(CLK,RESET)

BEGIN

IF RESET='1' THEN EN'0');

SAMP_CONTS'0');

EN

3波形仿真

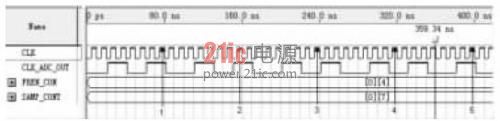

圖4中的波形仿真是以模擬信號的一周期等于8個CLK時鐘周期,CLK_ADC_OUT是對CLK進行4分頻且分頻后的時鐘占空比為50%為假設的。1號箭頭指向的時鐘上升沿標志著第一周期結束,上升沿之后進入第二周期。同理,2號箭頭所指時鐘的上升沿標志著第二周期的結束,上升沿之后標志著進入第三周期。

圖4波形仿真

在第一個周期中從CLK的第一個上升沿開始計時同時對CLK進行分頻可以得到CLK_ADC_OUT時鐘信號,在第一周期中在CLK的第二個上升沿CLK_ADC_OUT電平翻轉(存在延時),在第二周期中在第三個上升沿CLK_ADC_OUT電平翻轉,在第三個周期中在CLK的第四個上升沿CLK_ADC_OUT電平翻轉。可以看出波形仿真圖是對圖1(a)、(b)兩圖表達時鐘的實現。在這里應該注意到,在第一周期中雖然也有8個CLK的上升沿,但是并沒有表示出如1號箭頭所指CLK時鐘上升沿之后與第二周期第一個CLK時鐘上升沿之間的波形。

4結論

本文介紹了等效時間采樣的基本原理、系統實現的具體方案。等效時間采樣技術實現了利用低速的ADC器件對寬帶模擬信號的采集,降低了系統對ADC器件的要求以及系統實現的復雜度。本文介紹的等效時間采樣技術由于使用了FPGA采樣技術,使得在被采樣信號的一個周期中相較于一個周期僅能采集一個點的順序等效時間采樣有很大的提高,并且可以控制被采集信號一個周期中的采集點數從而可以根據后續器件處理速度實現變頻控制采樣。通過FPGA實現等效采樣時間,降低了系統實現的復雜度,同時可以十分方便的對代碼進行修改使系統的調試更加簡便。

評論