了解如何在MCU的內部總線結構驅動器應用效率

微控制器現在有一個驚人的數字,可以同時使用來卸載低級別的功能從CPU片上外設。這可以大大提高加工效率,降低功耗,并簡化設計。你可能會在一個不幸的意外,不過,如果你的外設功能壓倒內部總線接口和數據傳輸緩慢的大幅提升。幸運的是,微控制器制造商已經增加了新的,高效的總線接口,常與關鍵外設和片上存儲器,可以幫助支持多種數據傳輸之間的多條路徑。這些新的公交車確實有局限性,但是,由于連接一切,一切是在芯片面積和功耗方面過于昂貴。了解常見的使用模式,這些新的片上總線將幫助您創建,最大限度地提高數據傳輸帶寬,高效的設計。本文將快速回顧一下一些常見的智能片上總線的功能并舉例說明例如設計,充分利用這些關鍵功能。一些涉及的主題將包括:片上總線矩陣架構,采用DMA控制器,專用外設數據傳輸功能,智能緩存,公交優先系統,并中斷控制。

本文引用地址:http://www.j9360.com/article/201808/386689.htm通用總線接口架構

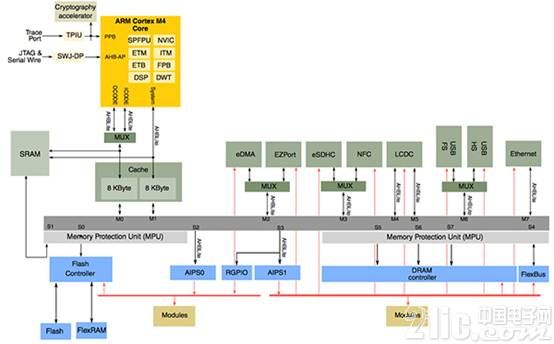

幾個關鍵的架構方法出現在幾乎所有的高性能總線互連結構。這并不奇怪,因為在關鍵戰略支持高帶寬是能夠建立可獨立運行多個并行連接。總線矩陣架構,幾個總線控制器可以獨立訪問多個公交車奴,也許是最常見的構建塊的高效率總線架構。飛思卡爾的Kinetis K70 MCU是需要有效的數據處理和移動互連架構類型的一個很好的例子。如圖1所示,飛思卡爾的Kinetis K70 MCU使用多級總線矩陣,可八個單獨的總線主控器和八個獨立總線從設備之間相互連接。這是可能的多個主機和從獨立運作。內存分配是非常重要的效益最大化。例如,以下操作可能所有操作在沒有重疊平行:

•核心 - 在Flash中的說明和核心只有數據和堆棧的SRAM_L

•USB - 在SRAM_U數據緩沖區

•LCD控制器 - 圖形緩沖區DDR

圖1:飛思卡爾的Kinetis K70 MCU總線互連架構。 (飛思卡爾提供)飛思卡爾還提供了一個模塊化開發平臺,為K70,它的飛思卡爾Tower System的一部分,使通過可重構硬件快速原型和工具再利用。該TWR-K70F120M可與廣闊的選擇塔式系統的外設模塊,包括新的TWR-LCD-RGB它從K70 MCU圖形LCD控制器接受RGB數據。當兩個或多個主機試圖訪問一個從端口,接口將使用仲裁算法,以確定哪些主機將首先訪問端口。兩種常見的仲裁方案,可以經常用于總線訪問是固定的優先級或循環。在一個固定的優先級方案中的主優先級是固定的,通過優先級較低的主人給予高優先級的主站的訪問權限。如果有幾個主站以相等的優先權,以循環優先級方案可以被使用。在這個方案中的主人旋轉優先為,隨著時間的推移,有平等機會獲得資源。通知的DMA訪問總線矩陣的重要性。通常情況下,DMA傳輸是最節能的所以對DMA具有高效的主機訪問總線矩陣是至關重要的。一些資源將有多個連接到總線矩陣 - 注意例如DRAM控制器 - 因為它們是多個主關鍵資源。這通過消除“訪問阻塞”當多個主需要訪問相同的資源,可能會發生,提高了整體性能。

高級外設總線結構,以提高效率

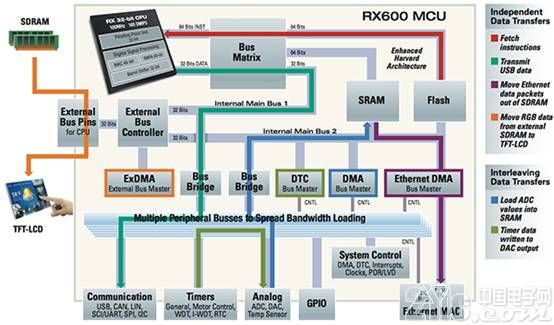

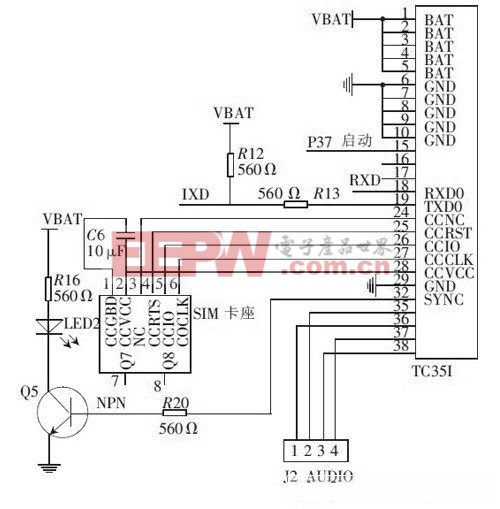

在許多MCU應用,外設的操作是一樣的CPU和內存操作一樣重要。它可以提高轉換效率,如果有與關鍵外設功能以及基于CPU的功能,采用先進的總線接口。瑞薩RX600 MCU有多個外圍總線,可用于更有效地傳播帶寬負載。如圖2所示,RX600不僅具有用于面向CPU動作的總線矩陣(在該圖的頂部示出),但多個外圍總線(在圖的底部示出),以更好地智能外設之間分配帶寬。甲顯著量周流量從來不需要訪問CPU總線矩陣和這個提高了數據傳輸效率,而不增加CPU總線矩陣的大小,通常是更高的性能以及大芯片尺寸和更高功率子系統。

圖2:瑞薩RX600多總線架構擴展帶寬負載。

評論