去耦電容的選擇、容值計算和布局布線

有源器件在開關時產生的高頻開關噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個局部的直流電源給有源器件,以減少開關噪聲在板上的傳播,和將噪聲引導到地。

本文引用地址:http://www.j9360.com/article/201808/385436.htm去耦電容的容值計算

去耦的初衷是:不論IC對電流波動的規定和要求如何都要使電壓限值維持在規定的允許誤差范圍之內。

使用表達式:CSU=ISt

由此可計算出一個IC所要求的去耦電容的電容量C。

SU是實際電源總線電壓所允許的降低,單位為V。

I是以A(安培)為單位的最大要求電流;

ST是這個要求所維持的時間。

去耦電容容值計算方法:推薦使用遠大于1/m乘以等效開路電容的電容值。

此處m是在IC的電源插針上所允許的電源總線電壓變化的最大百分數,一般IC的數據手冊都會給出具體的參數值。

等效開路電容定義為:C=P/(fU^2)

式中:

P——IC所耗散的總瓦數;

U——IC的最大DC供電電壓;

f——IC的時鐘頻率。

一旦決定了等效開關電容,再用遠大于1/m的值與它相乘來找出IC所要求的總去耦電容值。然后還要把結果再與連接到相同電源總線電源插針的總數相除,最后求得安裝在每個連接到電源總線的所有電源插針附近的電容值。

去耦電容選擇不同容值組合的原因:

在去耦電容的設計上,通常采用幾個不同容值(通常相差二到三個數量級,如0.1uF與10uF),基本的出發點是分散串聯諧振以獲得一個較寬頻率范圍內的較低阻抗。

電容諧振頻率的解釋:

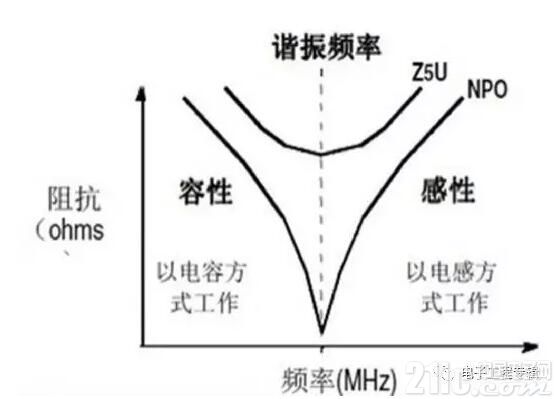

由于焊盤和引腳的原因,每個電容都存在等效串聯電感(ESL),因此自身會形成一個串聯諧振電路,LC串聯諧振電路存在一個諧振頻率,隨著電力的頻率不同,電容的特性也隨之變化,在工作頻率低于諧振頻率時,電容總體呈容性,在工作頻率高于諧振頻率時,電容總體呈感性,此時去耦電容就失去了去耦的效果,如下圖所示。因此,要提高串聯諧振頻率,就要盡可能降低電容的等效串聯電感。

電容的容值選擇一般取決于電容的諧振頻率。

不同封裝的電容有不同的諧振頻率,下表列出了不同容值不同封裝的電容的諧振頻率:

需要注意的是數字電路的去耦,低的ESR值比諧振頻率更為重要,因為低的ESR值可以提供更低阻抗的到地通路,這樣當超過諧振頻率的電容呈現感性時仍能提供足夠的去耦能力。

降低去耦電容ESL的方法:

去耦電容的ESL是由于內部流動的電流引起的,使用多個去耦電容并聯的方式可以降低電容的ESL影響,而且將兩個去耦電容以相反走向放置在一起,從而使它們的內部電流引起的磁通量相互抵消,能進一步降低ESL。(此方法適用于任何數目的去耦電容,注意不要侵犯DELL公司的專利)

IC去耦電容的數目選擇

在設計原理圖的時候,經常遇到的問題是為芯片的電源引腳設計去耦電容,上面已經介紹了去耦電容的容值選擇,但是數目選擇怎么確定呢?理論上是每個電源引腳最好分配一個去耦電容,但是在實際情況中,卻經常看到去耦電容的數目要少于電源引腳數目的情況,如freescale提供的iMX233的PDK原理圖中,內存SDRAM有15個電源引腳,但是去耦電容的數目是10個。

去耦電容數目選擇依據:

在布局空間允許的情況下,最好做到一個電源引腳分配一個去耦電容,但是在空間不足的時候,可以適當削減電容的數目,具體情況應該根據芯片上電源引腳的具體分布決定,因為廠家在設計IC的時候,經常是幾個電源引腳在一起,這樣可以共用去耦電容,減少去耦電容的數目。

評論