如何設計基于FPGA和USB2.0的高精度數據采集系統?

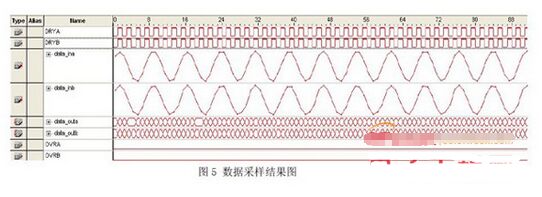

3 系統測試采用以產生頻率為20MHz 的高頻信號發生器,峰值為2.36Vpp 的正弦波作為模擬輸入。系統的測試采用SignalTapII來獲取兩路數據采樣數據,并且模擬轉后后存入到FIFO 中的數據和信號。采樣數據的模擬波形圖如圖5 所示。

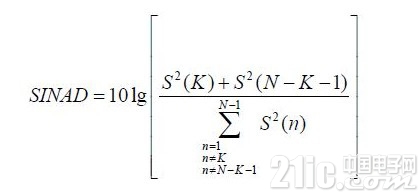

從圖5 可以看出,由于兩路輸入的信號存在一定的增益和偏移誤差,從而導致所收集數據的信號增幅值之間,產生了不一致現象。采用快速傅里葉變化分析法,首先在輸入的輸入信號上采集N 個點做快速傅里葉變換,假設信號譜線在K 和N-K-1 之間,那么就可以得到信噪諧波比SINAD :

為避免信號頻譜泄露,要求波形的采樣率fs 和輸入信號頻率f0,滿足其f0=fs*M/N,其中M 為一個合適的正整數。

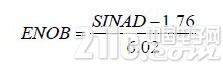

此方法可以進行ADC 的有效位數的測試,實驗ENOB,將其取6 次得到的平均結果約為6.2.后面還要將采集到的數據進行進一步的分析,來檢驗通道間的不匹配對系統性能的影響。

4 結論

介紹了一種基于FPGA 基于FPGA 和USB2.0 的高精度數據采集系統,通過FPGA 對AD 的工作方式,進行合理的配置,并充分利用其內部自帶的邏輯資源,實現對數據的緩存,避免使用其他微處理器進行的數據處理,本設計可以很好的減少芯片數和空間體積,更有利于FPGA 的發揮,具有簡單、靈活、功能多樣的特點。

評論