名家芯思維——FPGA助力人工智能|第68期國際名家講堂(講堂&實操)

主辦單位

本文引用地址:http://www.j9360.com/article/201807/382657.htm工業和信息化部人才交流中心(MIITEC)

承辦單位

江北新區IC智慧谷

協辦單位

南京江北新區人力資源服務產業園

南京集成電路產業服務中心

江蘇省半導體行業協會

中國電科集團

支持媒體

EETOP、半導體行業觀察、芯師爺、中國半導體論壇、芯榜、IC咖啡、半導體行業聯盟、半導體圈、芯世相、芯片超人、芯通社、芯論、電子產品世界網

活動安排

1.名家芯思維——2018年FPGA助力人工智能研討會(免費參與)

活動時間:2018年7月24日(周二上午)

活動地點:南京江北新區產業技術研創園 (南京浦口區團結路99號孵鷹大廈A座3樓316)

臨江路地鐵1號口有免費接駁車送至研創園

2.第68期國際名家講堂:FPGA時序/功耗優化和軟硬件協同設計(需注冊費,詳見下文)

活動時間:2018年7月24-26日(周二-周四2.5天)

活動地點:南京江北新區智芯科技樓7樓(南京江北新區星火路15號)

南京地鐵3號線星火路地鐵站1號或4號出口100米

名家芯思維:2018年FPGA助力人工智能研討會(免費參與)

活動時間:2018年7月24日(周二上午)

活動主題:FPGA助力人工智能

活動地點:南京江北新區產業技術研創園(南京市浦口區團結路99號孵鷹大廈A座3樓316)

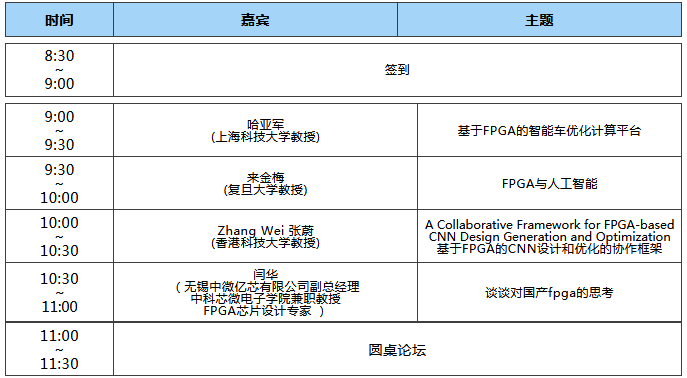

活動議程:

注:以上安排可根據實際情況進行調整。

報名方式

1. 郵件報名

報名回執表下載鏈接:http://www.icplatform.cn/form

填寫報名回執表并發送Word電子版至“芯動力人才計劃”郵箱:icplatform@miitec.cn,

郵件題目格式:報名+FPGA助力人工智能研討會+單位名稱+人數;

郵件內容:含有姓名、單位、部門及職務、電話、郵箱。

2.微信報名

掃一掃下方二維碼,直接報名(推薦)

3.電話報名

汪晨 025-69640094 13901584204

張歡 025-69678210 18262610717

第68期國際名家講堂:FPGA時序/功耗優化和軟硬件協同設計 講堂+實操

專家介紹

哈亞軍 Yajun Ha 上海科技大學教授

個人履歷:

1.1996年獲浙江大學學士學位。

2.1999年獲新加坡國立大學碩士學位。

3.2004年獲比利時魯汶大學博士學位。

4.目前是上海科技大學的全職教授。之前,他是擔任新加坡資訊與通信研究院科學家及比亞迪聯合實驗室主任。同時,他還是新加坡國立大學電子與計算機工程系的副教授。

曾在比利時歐洲微電子中心 (IMEC) 任研究員,在上海航天局航天測控通信研究所參加研究工作。

研究領域:

FPGA的架構、工具和應用、可重構計算、低功耗數字集成電路與系統設計、機器人與智能車以及和智能硬件相關的嵌入式系統研究及應用。

所在機構及協會任職:

1.2016-2017年,擔任IEEE電路和系統I(TCAS I)雜志的副主編;

2.2013-2014年,擔任IEEE超大規模集成系統(TVLSI)雜志的副主編;

3.2011-2013年,擔任IEEE電路和系統II(TCAS II)雜志的副主編;

4.2009年以來,擔任低功耗電子(JOLPE)雜志的副主編。

5.擔任亞太電子設計自動化會議(ASP-DAC)2014年組委會主席;可編程技術國際會議FPT 2010和FPT 2013技術委員會主席;IEEE電路和系統協會新加坡分會主席(2011年和2012年);ASP-DAC指導委員會成員;以及IEEE CAS VLSI和應用技術委員會成員。

6.他是嵌入式系統和FPGA領域的許多知名會議的技術委員會成員,如DAC、DATE、ASP-DAC、FPGA、FPL和FPT。他是上海“千人計劃”學者。他也是IEEE的高級成員。

所獲榮譽:

在TCAS I & II 、TVLSI、TC、JSSC以及DAC和ISSCC等國際知名期刊和會議上發表了近百篇學術論文。

講堂大綱

1.FPGAs: Overview of architectures and tools (FPGAs: 架構和工具的概述)

本部分將從回顧數字系統設計基礎開始,為本課程的其他主題奠定基礎。在同步設計中,設計準則、時間和功耗約束將被強調,因為它們是所有FPGA設計應該遵循的初始要求。接下來,我們將概述一般的FPGA架構和工具,并用供應商提供的FPGA架構和工具的實例來說明。

具體的主題包括:

a.Digital system design basics 數字系統設計的基礎

b.Overview of FPGA architectures FPGA架構的概述

c.Overview of FPGA design tools FPGA設計工具的概述

這堂課也將介紹課程的整體內容,并解釋將會遵循的邏輯與方法。重要的是,課程的主要學習目標將會被闡釋,以及為完成這些目標所需要做的事。

2.Timing Concepts 時間概念

滿足時間要求通常是FPGA實現最重要的挑戰,特別是當所需的時鐘頻率很高時。我們討論了數字電路和系統中使用的各種計時概念,并說明了時間限制,它們來自哪里,以及它們如何幫助改進FPGA實現的計時性能。我們將在相應的實操中加強對概念的理解。

本節的具體主題包括:

a.Synchronous vs. asynchronous circuits 同步vs. 非同步電路

b.Synchronous timing concepts 同步時序概念

c.Global timing constraints 全局時序限制

d.Specific timing constraints 具體時序約束

e.Timing simulation 時序仿真

f.Timing report 時序報告

The corresponding lab will be: 相應的實驗練習為:Lab 1: Understanding Timing Simulation and Report(實驗一: 了解時序模擬和報告)

3.FPGA Timing Closure Techniques FPGA時序閉合技術

根據前一部分討論的概念,本部分將推薦高級FPGA體系結構中所選的組件,這些組件可能有助于改進時間安排。例如,各種定時驗證的IP硬核、高質量的時鐘管理器等等。此外,為了支持FPGAs進出數據傳輸需求的不斷增長,FPGAs中加入了高速I/O模塊,如多千兆收發機和以太網IP核。討論了高速度FPGA電路的高密度編碼技術。最后總結了一種快速高速時序閉合的推薦設計流程。

具體的主題包括:

a.Timing proven IP hard cores 時序已被驗證的IP硬核

b.Using high quality clocking 使用高質量的時鐘

c.Using high speed I/O modules 使用高速I / O模塊

d.HDL coding techniques for high speed circuits HDL編碼技術

e.High speed timing closure design flow 高速時序閉合設計流程

The corresponding lab will be: 相應的實操為:Lab 2: Timing Optimization for Closure(實驗二: 時序閉合優化)

4.Power Concepts 功耗概念

在移動應用中,由于FPGA實現的功耗限制了每次電池充電后的工作時間,因此滿足功耗通常是FPGA實現的關鍵挑戰。我們將討論數字電路和系統中使用的各種電源概念,并展示什么是電源組件,它們來自哪里,以及如何評估FPGA實現的功耗。我們將在相應的實驗中加強對概念的理解。

具體的主題包括:

a.FPGA power consumption components ·FPGA功耗來源

b.Low power FPGA architectures ·低功耗FPGA架構

c.Low power FPGA design tools & algorithms 低功耗FPGA設計工具和算法

d.FPGA power estimation FPGA功率估計

The corresponding lab will be: 相應的實操為:Lab 3: FPGA Power Evaluation(實驗三:FPGA功耗評估)

5.FPGA Power Optimization Techniques FPGA功耗優化技術

基于前一部分討論的概念,本部分將討論實現低功耗FPGA實現的一些功耗優化技術,以及使用FPGA設計工具實現低功耗的正確設計方法。

具體的主題包括:

a.FPGA power optimization techniques FPGA功耗優化技術

b.Low power design guidelines 低功耗設計指導方針

The corresponding lab will be: 相應的實操為:Lab 4: FPGA Power Optimization(實驗四: FPGA功耗優化)

6.Processor and Accelerator Based Computing Architecture (基于處理器和加速器的計算體系結構)

在FPGA計算系統中,我們通常將計算非密集型代碼分配給處理器(PS),而計算密集型代碼分配給基于FPGA邏輯(PL)的加速器。本部分主要介紹處理器+加速器(PS+PL)體系結構的主要概念。主題包括I/O接口、尋址、中斷、直接內存訪問等。

7.Software/Hardware Co-Design Flow 軟件/硬件協同設計流程

本部分介紹了如何使用SDSoC框架進行軟硬件協同設計。我們首先討論如何構建SDSoC聯合設計平臺,該平臺由PS+PL硬件體系結構及其Linux OS系統軟件組成。然后介紹了如何在PS上編譯算法。第三,我們討論了如何使用剖析來分析算法,知道算法的哪一部分應該分配給PS,哪一部分應該分配給PL。最后,我們使用SDSoC來幫助我們快速實現所決定的軟硬件劃分,并對其性能進行評估。

The corresponding lab will be: 相應的實操為:Lab 5: Software/Hardware Co-Design with SDSoC(實驗五: 軟件/硬件與SDSoC協同設計)

8.Software/Hardware System Optimization 軟件/硬件系統的優化

討論了軟硬件協同設計系統的優化問題。利用前一部分得到的共同設計的系統,我們可能想進一步提高系統性能。我們將討論如何使用高級合成工具來優化這方面的PL硬件性能。

The corresponding labs will be:

相應的實操為:

a.Lab 6: Co-Design Optimization(實驗六: 協同設計優化)

b.Lab 7: Building SDSoC Co-Design Platform(實驗七: 搭建SDSoC協同設計平臺)

注冊費用

(1)注冊費用:4800元/期

在線報名請選擇“普通學員注冊”通道

(2)芯動力合作單位學員:3800元/期

在線報名請選擇“合作單位學員注冊”通道

(3)學生福利:

全國高校學生(本碩博)參加國際名家講堂,享受標準注冊費半價福利;

南京本地學校學生專享注冊費:1000元/人。

在線報名請選擇“學生注冊”通道

(4)老學員福利:

凡已付費參加任意一期2018年國際名家講堂,均可本人以半價注冊費參加后續6個月內任意一期2018年國際名家講堂。

在線報名請選擇“老學員注冊”通道

(5)高校福利:

全國高校教師(付費注冊)可免費攜帶1名學生

教師在線報名請選擇“普通學員注冊”通道,攜帶的學生請選擇“特邀注冊”通道

注:

①優惠政策:針對學員推出Bonus Class IV優惠政策,詳情請點擊藍字部分。

②學生注冊費,需提供學生證或所在學校出具的學生證明(加蓋學校或學院公章),掃描件發送至郵箱:icplatform@miitec.cn,審核通過后即可參加。

③含授課費、資料費、活動期間午餐。不含學員交通、住宿等費用(學員自理)。

國信芯世紀南京信息科技有限公司為本期國際名家講堂開具發票,發票內容為培訓費。

請于2018年7月20日前將注冊費匯至以下賬戶,并在匯款備注中注明款項信息(第68期+單位+參會人姓名)。

付款信息:

戶 名:國信芯世紀南京信息科技有限公司

開戶行:中國工商銀行股份有限公司南京浦珠路支行

帳 號: 4301014509100090749

或請攜帶銀行卡至活動現場,現場支持 POS 機付款。

報名方式

1.郵件報名(推薦)

報名回執表下載鏈接:http://www.icplatform.cn/form

填寫報名回執表并發送Word電子版至“芯動力人才計劃”郵箱,郵箱地址:icplatform@miitec.cn

回執表文件名和郵件題目格式為:“報名+第68期+單位名稱+人數”。

2.微信報名

掃描下方二維碼,在線報名(推薦):

報名須知:本次活動,采取線上報名,線下付款的形式,線下付款可以對公打款,或者現場POS刷卡付款,請在線提交報名!

3.電話報名

汪晨 025-69640094 13901584204

張歡025-69678210 18262610717

住宿預訂

酒店名稱:南京新逸天金絲利酒店

酒店地址:南京市浦口區麗景路8號(地鐵三號線東大成賢學院4號出口400米)

協議價格:豪華單人間/標準間 338元/間

預定方式:請需要預訂酒店的學員在7月20 日12點前聯系工作人員。

預定酒店聯系人:

郁大鵬 18017813372

交通路線

1、名家芯思維:南京市江北新區產業技術研創園

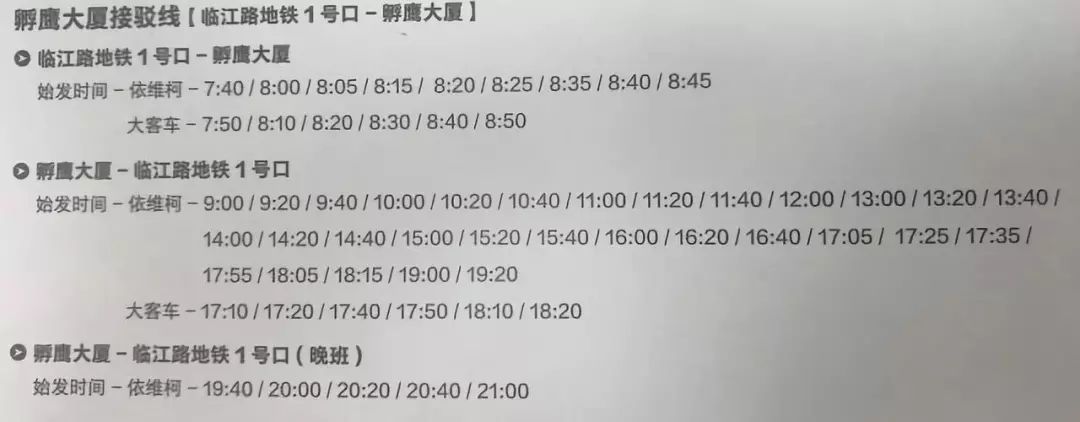

接駁車線路時間如下(地鐵10號線臨江路1號口有免費接駁車送至研創園)

2、第68期國際名家講堂:南京市江北新區智芯科技樓7樓

路線:南京地鐵3號線星火路地鐵站1號口南100米

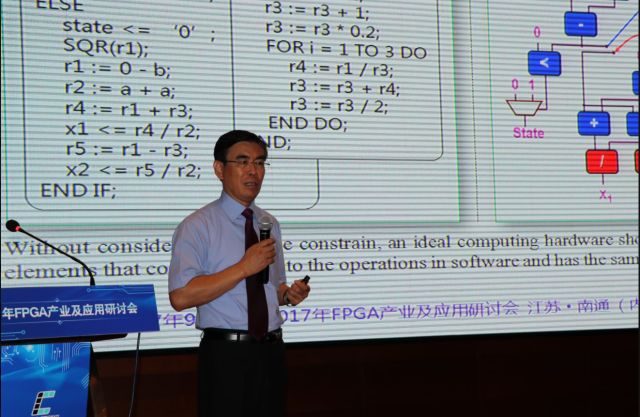

2017年FPGA研討會及講堂現場集錦

2017年9月20日,由工業和信息化部人才交流中心(MIITEC)和比利時微電子研究中心(IMEC)聯合主辦的“名家芯思維”之2017年FPGA產業及應用研討會在江蘇省南通市成功舉辦,200余人參加本次活動。清華大學魏少軍教授,無錫中微億芯有限公司總經理 單悅爾,賽靈思公司(Xilinx)研究院前沿技術拓展經理 陸佳華,中國科學院楊海鋼教授、可編程芯片與系統研究室主任楊海鋼分別進行主題分享。

9月20—22日,“芯動力”人才發展計劃——國際名家講堂第46期“FPGA架構,工具和應用”在南通舉辦。上海科技大學哈亞軍教授與學員們交流探討FPGA架構、工具和應用的相關內容。本次活動130余位來自企業、高校、科研院所的技術研究人員、相關代表前來參加。

哈教授圍繞“FPGA架構,工具和應用”的主題,從理論技術、應用分享等多個不同的角度深入分析FPGA的架構、工具和應用。

哈亞軍教授指出FPGA架構使數字系統得以運用,一般有三部分組成:可編程化邏輯,可編程化路徑和可編程化I/O;討論了FPGA架構中每個組成的作用,并且說明FPGA架構空間的系數,并展示多年來如何發展和改良。此外,聚焦于通用的FPGA架構,提供來自主要FPGA供應商的FPGA架構實例:如Xilinx 和 Altera。

同時,講堂中論述進階的FPGA架構主題。如為支持FPGA中的數據轉換的增長性需求,FPGA中加入了高速輸入、輸出系統,例如千兆級收發器和以太網IP核。論述了在新的FPGA架構中低能耗和高速度I/O,最終比較不同應用中使用FPGA和ASIC為計算平臺。

FPGA應用部分介紹了包括國防航空航天電子設備,醫療電子,汽車影像,實況影像引擎,消費電子,數字顯示,數據中心服務器,高性能計算服務器,工業成像,醫療超聲波,影像及圖像處理高清攝影,有線通信,光傳輸網絡,無線通信處理器等方面的應用。哈教授運用應用及案例剖析FPGA的技術內容和相關應用,使學員們對“FPGA”的相關技術及其應用有了更加全面的了解。

芯動力人才計劃介紹

“芯動力”人才計劃是工業和信息化部人才交流中心設立的服務國家集成電路產業發展的人才專項,通過整合國內外優質智力資源,搭建園區、企業、專家、人才等行業要素廣泛參與、資源共享的交流平臺,構建充滿活力和富含價值的集成電路產業人文生態環境。

“IC智慧谷”是“芯動力”人才計劃的重要組成部分,以提升城市產業品牌、實現集成電路產業人才和項目集聚為目標,由中心與地方政府共同運營。

“芯動力”人才計劃

推動產業演繹人才學-思-創三重奏。

IC智慧谷

協助城市奏響人才聚-留-融三部曲。

“芯動力”人才計劃

為中國集成電路產業和半導體人做良“芯”事

芯動力人才計劃:

聯系人:汪晨、周靜梅

電 話:025-69640094、025-69640097

E-mail:icplatform@miitec.cn

工業和信息化部人才交流中心

2018年6月28日

評論