基于40 nm CMOS工藝的高速SAR ADC的設計

作者 魏祎 電子科技大學 微電子與固體電子學院(四川 成都 610054)

本文引用地址:http://www.j9360.com/article/201802/376171.htm魏祎(1993-),男,碩士生,研究方向:大規模集成電路與系統。

摘要:基于40 nm CMOS工藝,設計了一種高速逐次逼近型模數轉換器。本設計采用了非二進制冗余DAC技術來緩解ADC對建立時間和建立精度的要求,來提高ADC量化的準確性;采用帶有預放大級的高速比較器來提高比較器的精度,同時減小后級Latch的回踢噪聲,采用了兩級Latch來進一步提高比較器的速度;采用基于鎖存器的鎖存單元來提高SAR邏輯控制電路的速度,并且采用了異步時序控制,不需要外部時鐘,有利于提高SAR ADC的速度,并降低了設計的復雜度。設計的SAR ADC在160 MHz的采樣頻率下,在不同輸入信號頻率下均可以實現12 bit的量化精度,SFDR均在83 dB以上。

0 引言

隨著智能設備的普及和通信技術的不斷發展,消費者對智能互聯的需求變得越來越迫切。這就要求通信網絡要有更快的數據速率。而更高的數據傳輸速率就要求更大的帶寬。因此通訊接收機就需要更快的數據轉換器,將模擬的無線通信信號轉換為數字信號,供DSP芯片進行處理。模數轉換器(Analog-to-Digital Converter,ADC)作為連接模擬系統和數字信號處理系統的橋梁起著關鍵的作用。

在同樣精度與速度要求下,與快閃型、折疊內插型、流水線型等ADC相比,SAR ADC結構簡單、功耗低、易于集成等特點,因此得到了廣泛的應用[1-2]。

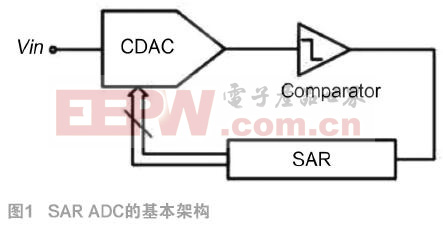

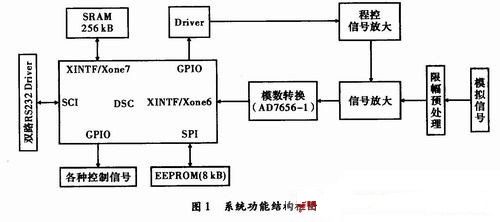

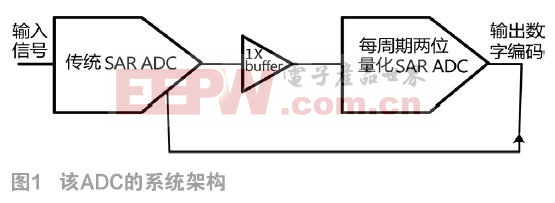

常見的SAR ADC主要由自舉采樣開關、DAC、比較器和SAR邏輯電路組成,其基本架構如圖1所示。其中DAC主要采用電容陣列構成的CDAC。一個N位的SAR ADC的工作原理是采用二進制搜索算法確定輸入信號所在的量化區間。首先,輸入信號通過采樣開關存儲在DAC中;然后通過比較器對輸入信號和DAC產生的參考電壓進行比較,將比較結果輸出到SAR邏輯電路,SAR邏輯控制電路根據比較結果去控制DAC中的開關切換,使DAC進一步產生逼近輸入信號的參考電壓;最后當每一位都比較完成后,DAC的輸出電壓將收斂到與輸入信號相差不超過1/2 LSB(1LSB=VFS/2N)的范圍,比較器的每一位輸出碼組成最終的N位輸出碼。

本設計采用了非2進制冗余DAC技術、靜態鎖存比較器、基于鎖存器的SAR邏輯控制電路,在CMOS工藝下實現了12 bit的高速SAR ADC的設計。

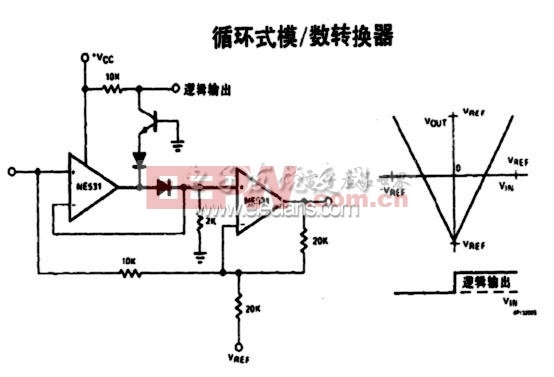

1 DAC的設計

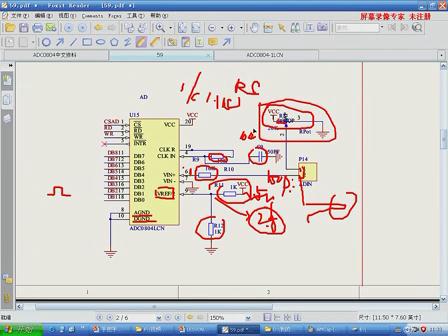

DAC為非二進制傳統電容陣列,陣列基底小于2。由于DAC陣列總電容很小,為抑制電荷注入,采用下極板采樣方式。為保證12 bit動態范圍,選取定基底radix=1.877, 以13位電容陣列的方式來實現12 bit的SAR ADC。電路結構如圖2所示。

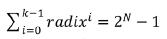

非二進制冗余DAC技術緩解了ADC對建立時間和建立精度的要求[3]。在傳統的二進制電容陣列里,電容的值都是以2為基底,ADC的轉換編碼和輸入信號之間是線性映射的關系。如果將電容陣列的基底設置成小于2,則轉換編碼和輸入信號之間不再是線性映射,這種非線性映射恰恰為DAC的建立提供了冗余,可一定程度放寬DAC的建立精度,同時建立時間也大大縮短。一個N位的非二進制SAR ADC,假設以radix作為電容陣列的基底,由于radix <2,繼續使用N位電容進行量化將導致ADC不足以提供N位精度的動態范圍,假設使用k位電容進行量化,則需滿足

(1)

(1)

根據式(1),如果利用13位電容來實現12位ADC,則基底至少為1.8772。冗余發生在量化編碼為0111…111和1000…000之間,只要輸入信號在此冗余范圍,不管高位量化值是0還是1,最終都能被準確地表示,換言之,只要DAC能夠建立到對應的冗余范圍內,最終就能正確完成量化[4]。

2 SRA ADC的工作原理

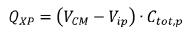

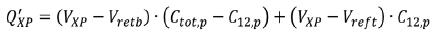

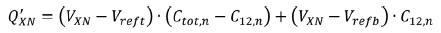

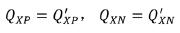

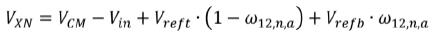

在采樣階段,采用下極板采樣的方式,DAC差分輸出端接共模電壓VCM,所有電容下極板分別接輸入信號Vip和Vin,此時差分DAC輸出端的電荷:

(2)

(2)

(3)

(3)

為了減小采樣開關的非理想效應,先將VCM開關斷開,再將自舉采樣開關斷開,完成對輸入信號的采樣。采樣完成后即進行第一次量化。以差分DAC的P端為例,首先將上極板從共模電平VCM斷開,然后將除MSB電容外所有電容的下極板切換到Vrefb,MSB電容下極板切換到Vrefb,DAC建立完成即進行第一次比較,此時,上極板電荷:

(4)

(4)

互補DAC的N端的切換方式和P端相反,其切換后上極板電荷:

(5)

(5)

根據上極板電荷守恒:

(6)

(6)

可得第一次比較時:

(7)

(7)

(8)

(8)

其中定義模擬權重:

假設第一次比較結果D12=1,即VXP<vxn,則

3 比較器的設計

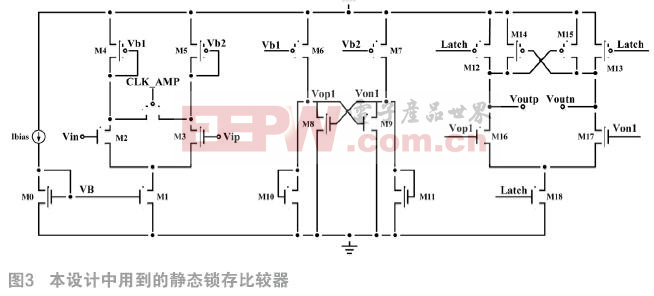

本設計中的比較器采用靜態鎖存比較器加一級動態鎖存器的結構,其結構如圖3所示。靜態鎖存比較器采用的再生單元是A類交叉耦合對[5],比較器的工作電流決定了其轉換速度。第一級為預放大級,對輸入信號進行放大,輸出電流通過鏡像注入再生單元,差分輸入對管的漏端與再生節點之間存在隔離,回踢噪聲較小。比較器采用異步時序控制,當比較器產生比較結果后對比較器進行復位操作。

本設計中SAR ADC的輸入信號為800 mVpp,一個LSB為195 mV。考慮到Latch的比較速度與輸入信號的關系,預放大級的增益設計為20 dB。在實際工作時,比較器的工作速度很快,因此預放大級需要有足夠的帶寬。本設計中預放大級的-3 dB帶寬為1.8 GHz。

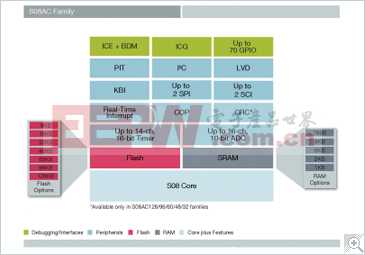

4 SAR邏輯控制電路的設計

采用同步結構的SAR邏輯需要額外的控制時鐘。對于一個N位同步SAR ADC而言,量化過程需要N個時鐘周期,采樣過程需要一個到多個時鐘周期,假設為一個時鐘周期,則ADC的采樣率為外部時鐘頻率的1/(N+1),由于采樣時鐘必須要保證精度且由外部時鐘分頻得到[6-7],因此在同步設計里首先要保證(N+1)倍于采樣率的外部時鐘的精度,不但相當困難,而且十分不經濟。

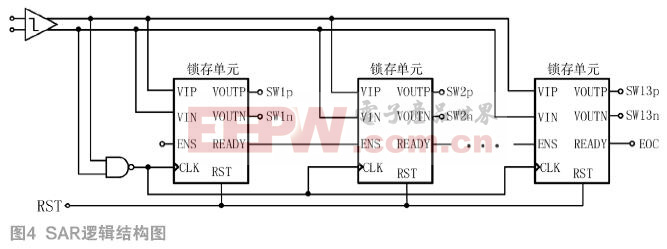

因此本設計采用異步時序控制的SAR邏輯。SAR邏輯控制電路由13個鎖存單元及對應的DAC開關控制信號產生電路組成,如圖4所示,本設計共有13個鎖存單元。

VIN和VIP接收比較器的輸出,ENS接收來自前一級的使能信號,CLK為鎖存單元的控制時鐘,控制內部的鎖存器,RST為復位信號,鎖存單元對比較器的結果進行鎖存后,經過邏輯電路產生VOUTP和VOUTN作為DAC開關的控制信號,來控制電容下極板的切換。其工作流程為,當比較器產生比較結果后,將比較結果輸出到SAR單元,同時將比較結果通過與非門來產生鎖存單元的控制時鐘,控制鎖存單元對比較器的輸出結果進行鎖存,鎖存完成后隨即產生一個使能信號,開啟下一級鎖存單元,等待下一次比較器的結果。當最后一級鎖存單元鎖存比較器結果后,產生的READY信號作為最終量化數據并行輸出的控制信號,并用于產生SAR邏輯控制電路的復位信號,同時將DAC的電容上極板接到VCM,等待下一個采樣周期的到來。

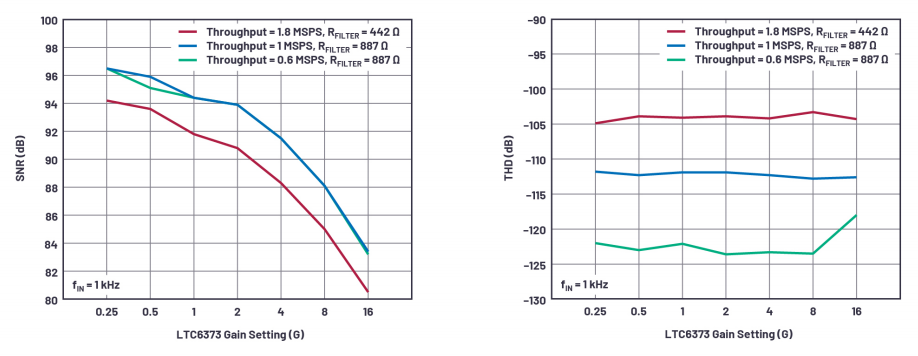

5 SAR ADC仿真結果

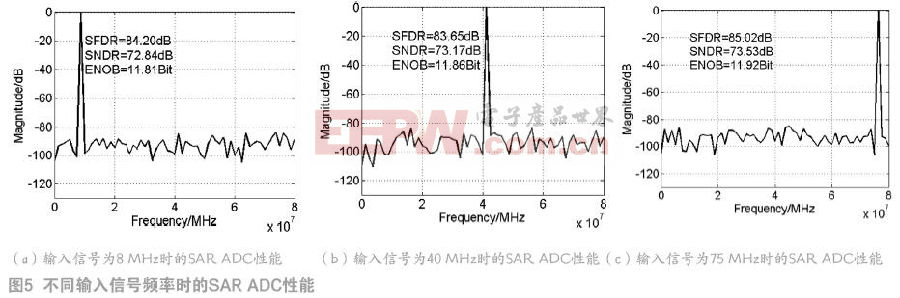

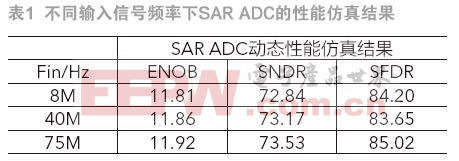

在采樣頻率Fs=160 MHz時,在不同輸入信號頻率下對SAR ADC進行仿真。輸入信號為差分的正弦波,差分擺幅為800 mVpp,參考電壓Vreft=800 mV,Vrefb=400 mV。通過Matlab對ADC的輸出數據進行FFT處理后,得到SAR ADC在不同輸入信號頻率下的動態性能如表1所示。

SAR ADC在不同輸入信號頻率時的性能仿真結果統計如表1所示。

由仿真結果可以看出,本ADC的設計實現在160MHz的采樣頻率下能夠完成13次量化,并保證了12位的量化精度。

6 結論

本設計采用了非二進制冗余DAC技術來緩解ADC對建立時間和精度的要求;采用帶有預放大級的高速比較器來提高比較器的精度,并減小后級Latch的回踢噪聲;SAR邏輯控制電路采用基于鎖存器的鎖存單元來提高SAR的速度,并且采用了異步時序控制,不需要外部時鐘,有利于提高SAR ADC的速度,并降低了設計的復雜度。

經過仿真驗證,本文設計的SAR ADC在160 MHz的采樣頻率下,在不同輸入信號頻率下均可以實現12 bit的量化精度,SFDR均在83 dB以上。

參考文獻:

[1]Y. Chai, J. T. Wu. A CMOS 5.37-mW 10-bit 200-MS/s dual-path pipelined ADC[J]. IEEE Journal of Solid-State Circuits, 2012, 47(12): 2905-2915

[2]Y. Zhu, C. H. Chan, S. W. Sin, et al.. A 34 f J 10b 500 MS/s partial-interleaving pipelined SAR ADC[C]. Symposium on VLSI Circuits, Honolulu, 2012, 90-91

[3]杜翎.基于非二進制量化算法的逐次逼近模數轉換器的設計[D].電子科技大學,2016.

[4]王偉.分辨率可配置型高速SAR ADC的研究與設計[D].電子科技大學,2016.

[5]C. C. Liu, C. H. Kuo, Y. Z. Lin. A 10 bit 320MS/s low-cost SAR ADC for IEEE 802.11ac applications in 20 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2015, 50(11): 2645-2654

[6]L. Du, S. Wu, M. Jiang, et al.. A 10-bit 100MS/s subrange SAR ADC with time-domain quantization[C]. International Symposium on Circuits and Systems, Melbourne VIC, 2014, 301-304

[7]Y. Zhu, C. H. Chan, S. W. Sin, et al.. A 34 f J 10b 500 MS/s partial-interleaving pipelined SAR

ADC[C]. Symposium on VLSI Circuits, Honolulu, 2012, 90-91

本文來源于《電子產品世界》2018年第3期第61頁,歡迎您寫論文時引用,并注明出處。

評論