AI架構創新和高端芯片發展

4 軟件定義芯片架構

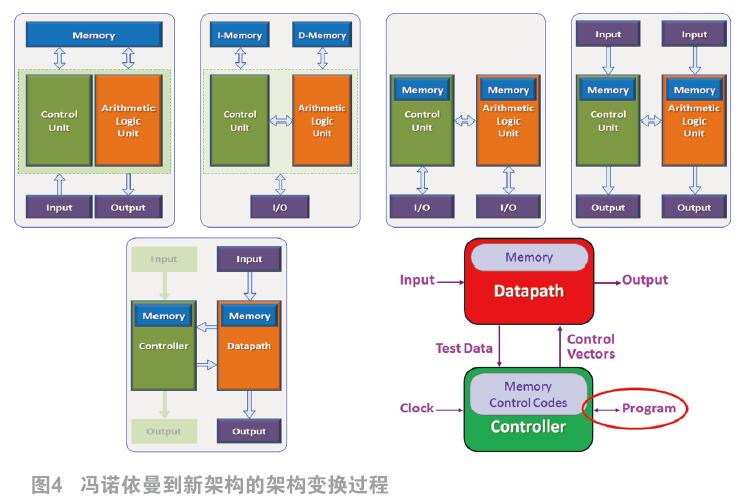

本文引用地址:http://www.j9360.com/article/201802/376161.htm如圖3所示為基本馮諾依曼架構,包括控制單元、算數邏輯單元、存儲器、輸入和輸出五個基本模塊。首先將存儲器分為兩塊,即I-Memory和D-Memory,分別對應指令和數據,這就是HUS結構。Input和Output合并,變成I/O;然后將存儲器分別放入控制單元和算數邏輯單元,再將I/O分為兩部分,一部分和控制單元相關,另一部分和數據邏輯單元相關;再將I/O分開,輸入放在上邊,輸出放在下邊;然后將這個結構逆時針旋轉90度,得到的架構即為軟件定義芯片架構(以下簡稱“新架構”)。馮諾依曼到新架構的架構變換過程如圖4所示。

因此,該架構實際上是從經典的馮諾依曼架構變換得來。但是它和馮諾依曼體系結構又有所不同,即它不再使用指令集,而直接采用信息流,這也是兩者間的本質區別。

另外,與傳統架構比較,新架構還具有以下特點:

1)傳統架構都是馮諾依曼等效架構,是剛性的;而功能化的硬件架構,是應用性的。

2)傳統架構是應用去適應計算的架構,新架構是計算架構適應應用。即,傳統架構是軟件適用硬件,而新架構是硬件適用軟件。

3)在傳統架構中,一個任務一個軟件;而在新架構中,一個任務會有多個等效軟件。

4)在傳統架構中,硬件和軟件是不變的;在新架構中,硬件和軟件是選擇性動態改變的。

5)傳統架構中,為了節省硬件資源,大量復用;新的架構中是使用冗余方式實現的。

5 計算模式的改善

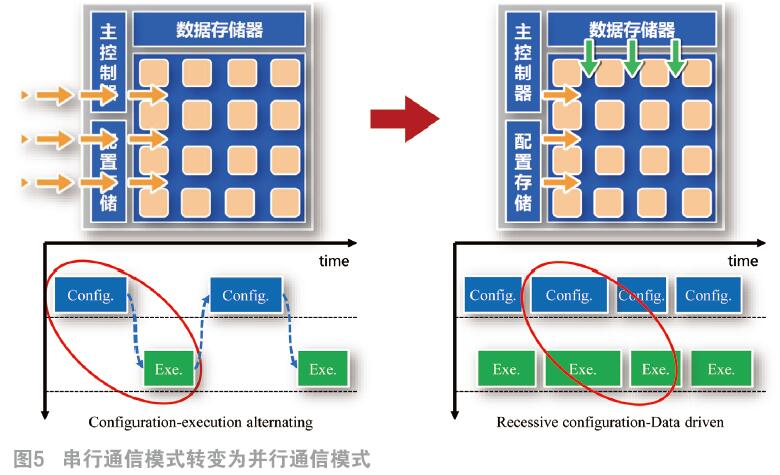

硬件配置時間和執行時間對于硬件架構來說是一個必須考慮的問題。當硬件配置時間多于執行時間時,顯然是不經濟,不合理的。而新架構在剛開始工作的時候,其中將近90%的時間都用來配置硬件,而只有10%的時間是用來進行計算和執行的。顯然這樣的架構需要進一步改善,主要通過以下兩種方式進行改善:

1)首先將配置信息減少。通過采用諸如配置子圖的方式、結構化組織等一系列方法,最終將配置信息減少將近80%。

2)數據不斷寫的過程也會耗費大量時間。很多數據寫進去并不需要翻譯,采用頻次優先方法,用的最多的先寫入,頻次少的就不寫入或少寫入,這樣可以將整個配置時間縮短12倍。

其計算模式變化如圖5所示。傳統架構是串行計算模式,而新架構則是交叉的并行計算模式。經過努力后,我們可以使一個陣列的計算時間占到整個運行時間的90%,而只有10%的時間用來實現配置。這樣將多數時間用來計算的架構才是更合理的架構。

6 針對不規則陣列的架構改善

在上述例子中給出的是規則的運算陣列,而實際上的運算陣列是不規則的,有不同的密度,中間可能出現迭代和循環,分支長短可能不一。在規則的陣列上運行不規則的運算顯然會出現效率的高低。

陣列是硬性放大的,我們無法改變硬件,因而只能改變軟件,具體通過以下方法:

1)把軟件并行化處理。特別是控制性的軟件并行化處理,甚至在時空上也作相應的變換,讓其在時空上也能并行化。

2)改變電源的供電情況。例如,在陣列中并非所有運算單元同時存在,這樣就需要一部分打開,一部分關掉,由于完全關掉后重新啟動需要很長時間,會降低性能,因而要使其部分處于淺度睡眠,有的進入深度睡眠,有的進入淺度睡眠,從而恢復的時候,節省啟動時間。

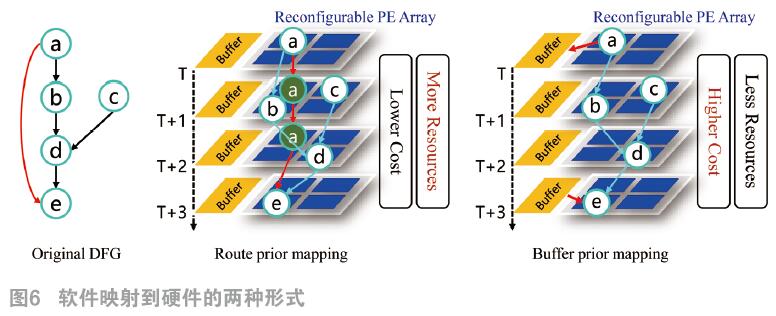

3)將軟件映射到不同的硬件上。不同映射形式會帶來不同的運算結果,這里給出兩種不同的應對方法,如圖6所示。a的數據走中間,可以通過route(計算資源)或者buffe(緩沖層)來傳輸,這兩種傳輸方式哪種更適合新架構,還需要建立一整套模型,通過性能的模型實現各種仿生變換,最終確定最優的執行時間。如果建立面向性能的模型,可以使得性能提升20%;而如果建立面向功耗的模型,可以使功耗降低26%。但是,現在還無法建立兩種模型的統一方案。

7 編程語言

全新的架構需要考慮全新的編程范式。傳統硬件用C語言編程;而出現GPU后,隨之而產生的是OpenCL編程語言;出現FPGA后,又有verilog、VHDL編程語言。而新架構軟件的編程語言是基于傳統編程語言,而基于原有的編程語言,語言不變、硬件不變的情況下,就需要去想新的編程范式。

FPGA很多時候是在編譯時做分析,來進行決策。例如非功能運算是在運行過程中通過依賴關系來決定。這種方法有諸多不便。其中,依賴關系在編程序的時候就知道了,并非到運行的時候才會發現。新架構編程序的過程中就可以發現其依賴關系,在編譯過程中就可以找到各個任務間的依賴關系,在運行的過程中保證其正確性就好。

新架構采用新的編程范式編寫程序與采用OpenCL編寫程序相比,速度提升了10倍;與英特爾的十核Xeon相比,性能仍有0.5~1.9倍的提升。

8 發展的機遇

把軟件定于芯片的方式與傳統的方式進行比較,新架構既具備ASIC的性能、功耗和特點,同時也保證了CPU的可讀性,這樣的結果還是很好的。當我們去做一個CPU、專用芯片或FPGA的時候,我們從定義開始出發,要完成一個電路設計,然后再去做其他的事情。如果你不懂電路設計,就無法運用FPGA進行設計。但是對于新架構而言,已經可以讓軟件設計工程師直接編程序,然后通過一個編譯器直接映射到硬件上去。這里主要需要一個好的編譯器,新架構的編譯器匯集了大量的設計方法訓練。

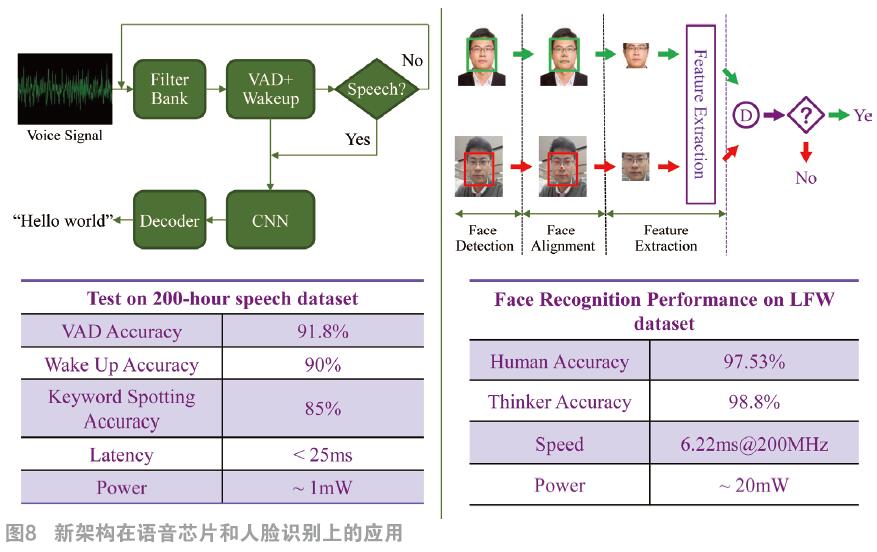

9 新架構的新應用

這樣變化的結構可以應用到AI,AI還有很多新的變化,不同的應用或神經網絡,我們能否通過變結構的方式,只要我們可以識別到一個具體的應用,識別出他用的是一個怎樣的神經網絡,就可以通過改變今天的功能來適應他,產生全新的發展呢?

如圖8所示,采用新架構設計的語音識別芯片,精度已經可以達到91.8%,可以識別聲紋,延時低達25 ms,功耗遠遠小于1 mW,應用到手機上幾乎不耗電;右邊是一個人臉識別,人臉識別結果最主要的是精度,可以達到99%,人類只能識別97%,工作在200 MHz,可以實現6 ms,運算功率,每瓦100萬億次的運算。

10 結論

芯片工藝技術進入10 nm,專用集成電路面臨嚴峻的挑戰,我們就該在架構上進行創新。其實在高端芯片上也是如此,如果跟著CPU的架構前進,我們永遠是跟在別人后面的,能夠在架構創新上超過別人才能引領時代。

硬件架構隨著軟件變化而變化的全新概念在保證芯片的功能滿足要求的同時,又能保證其融合性,也是一項很好的創新。

本文來源于《電子產品世界》2018年第3期第25頁,歡迎您寫論文時引用,并注明出處。

評論