高云半導體推出I3C高速串行接口解決方案

山東濟南,2018年1月9日訊,山東高云半導體科技有限公司(以下簡稱“山東高云半導體”)今天宣布推出基于低密度小蜜蜂?家族的GW1N-9 FPGA芯片的SDR-模式I3C IP (Master-Slave-Combined )高速串行接口解決方案,包括相關IP軟核、參考設計及開發板等完整解決方案。

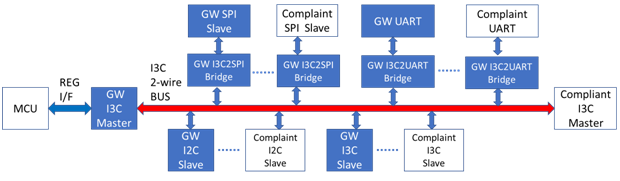

本文引用地址:http://www.j9360.com/article/201801/374142.htmI3C是MIPI聯盟一個新的通訊協議,該協議兼容并擴展了傳統I2C通訊協議,其總線為兩線式串行總線。高云I3C IP遵循MIPI聯盟I3C總線的通訊協議,集I3C Master和Slave于一體,是一個參數可配置、基于高云半導體FPGA芯片的IP設計。該IP可動態地配置成I3C Master或 Slave,實現I3C Master與I3C Slave或I2C Slave的通信,從而完成I3C通訊協議的各種功能。高云I3C Master與 Slave IP及高云I2C Slave IP可與遵循MIPI聯盟I3C通訊協議的其他Master或Slave外設,以及遵循MIPI聯盟I2C通訊協議的其他Slave外設直接相連通訊。

高云半導體軟核研發部門負責人高級經理高彤軍先生強調:“高云開發I3C IP核分兩步走,目前的初級版支持單倍數據速率(SDR)模式,后續升級版會支持雙倍數據速率(DDR)模式,進一步提高數據傳輸速率至33Mbps或以上。此外,今天發布的高云I3CIP,具有兼容并擴展I2C協議的功能,可直接與I2C Slave接入通信;后續升級版還附帶配套設計的I3C至SPI鏈接橋和I3C至UART鏈接橋。今后連帶發布的高云I3C-ECO-IP群組,將包括I3C2SPI-bridge、I3C2UART-bridge、SPI-Master-Slave-Combined IP、UART IP,從而能使I3C Master通過該鏈接橋直接與傳統的SPI和UART 接入通信。這為方便業界迅速運用I3C技術提升其電子產品設計的速度與效能,并兼具維系支持傳統外設,實現新老結合,降低成本,持續創新的最大性價比、性效比產品策略,鋪平了道路。”

高云半導體總裁兼CTO宋寧博士表示:“高云I3C IP及其FPGA設計具有低引線數、可擴展性、低功耗、更高的容量等創新性能,能有效的減少集成電路芯片系統的物理端口、支持低功耗、高數據速率和其他已有端口協議的優點,為支持現代移動手持設備、智能駕駛、IOT設計添加了許多增強的特性。”

I3C應用舉例

l力學感知(陀螺儀、加速計等)

l環境感知(聲、光、溫度、濕度等)

l仿生學感知(指紋、心率、呼吸等)

l通訊(近場通訊、遠紅外通訊等)

GW I3C基本特性

l高度靈活的參數可調設計,允許用戶精確調整數據/時鐘信號的周期,從而實現寬范圍的數據發送速度調節。

l支持靜態地址通訊

l支持動態地址機制

l支持I3C地址仲裁

lSingle Data Rate(SDR)

l支持I2C (Slave Only)消息

GW I3C高級特性

l支持熱接入(Hot-Socket)

l支持熱接入時動態地址分配

l支持Slave請求Secondary Master(SDR-Only)

l支持線載中斷(In-band Interrupts)

l支持CCC’s (Common Command Codes) 命令

GW I3C傳輸速度

高云半導體云源軟件支持GW I3C(Master-Slave-Combined )IP的全流程自動設計。GW I3CSDR模式最高數據傳輸速率達到12.5Mbps。

GW1N-9 FPGA

GW1N-9芯片為I3C協議專門設計可動態切換模式的IO電路,具有這一新特性的IO安排在芯片的上下兩個Bank上。用戶在使用這些IO時軟件模型無需改變,只需在約束文件中將I3C Mode打開即可。

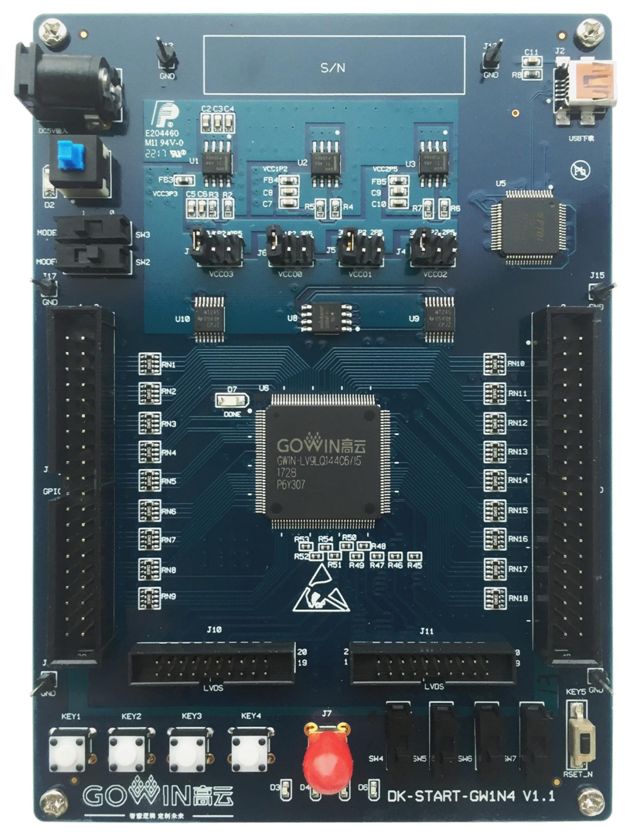

GW I3C IP開發板與參考設計

高云半導體提供通過實測驗證的I3C IP開發板,已配置好相關電路,可將多塊開發板連接在一起進行I3C BUS通訊實驗。

評論