多協議完全集成13.56MHz近場通信收發器集成電路設計

TRF7970A是一款高性能13.56MHz高頻RFID/NFC收發器IC,此器件由一個集成的模擬前端和一個針對ISO15693,ISO14443A,ISO14443B,和FeliCa的內置數據組幀引擎組成。這包括針對ISO14443的高達848kbps的數據速率,包括板上全部組幀和同步任務(在默認模式下)。TRF7970A也支持NFC標簽類型1,2,3,和4操作。這個架構使得用戶能夠建立一個完整且劃算而又高性能的多協議13.56MHzRFID/NFC/NFC系統和一個低成本微控制器。通過使用器件提供的直接模式中的兩個,可執行其它標準,甚至定制的協議。這些直接模式(0和1)使得用戶能夠完全控制模擬前端(AFE)并獲得到原始副載波數據或者非成幀數據(但已經是ISO格式數據)和相關(被提取的)時鐘信號的存取權限。

本文引用地址:http://www.j9360.com/article/201710/369493.htm接收器系統有一個雙輸入接收器架構。此接收器還包括多種自動和手動增益控制選項。接收到的輸入帶寬可被選擇來包含廣泛范圍的輸入副載波信號選項。通過RSSI寄存器可獲得接收到的來自應答機、周圍信號源或者內部電平的信號強度。接收器輸出可在一個數字化副載波信號和任一集成型副載波解碼器間進行選擇。所選擇的副載波解碼器將數據比特流和數據時鐘作為輸出發送。TRF7970A還包括一個接收器組幀引擎。這個接收器組幀引擎執行CRC或者奇偶校驗,移除EOF和SOF設置,并且將數據組織成用于ISO14443-A/B,ISO15693,和FeliCa協議的字節格式。然后通過一個128字節FIFO寄存器,微控制器(MCU)可訪問已組幀的數據。

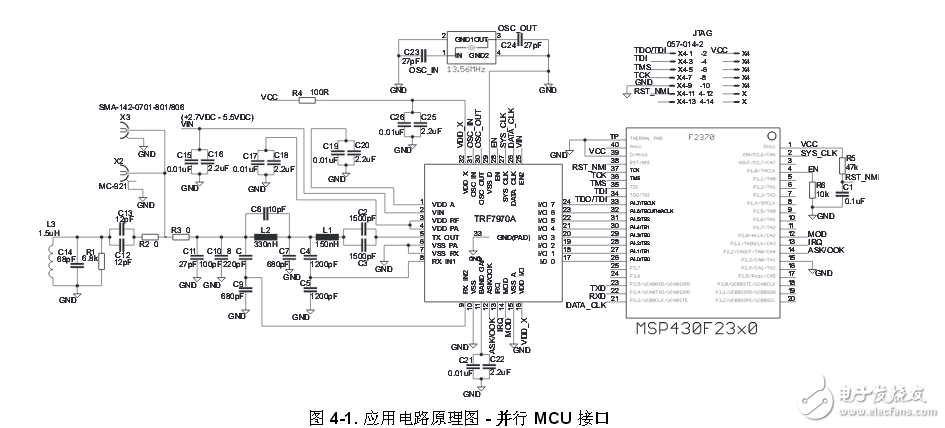

TRF7970A使用并行微控制器接口的讀取器系統

圖4顯示了最靈活的TRF7970A應用電路原理圖。ISO15693,ISO14443和FeliCa系統都可被設定地址。由于DATA_CLK線路上的低時鐘頻率,并行接口是將TRF7970A連接至MCU的最穩健耐用的方法。匹配至一個50Ω端口,這樣可實現到一個適當匹配的50Ω天線電路或者RF測量設備的連接(例如,一個頻譜分析儀或者一個功率計)。

圖顯示了一個并行MCU接口的示例應用電路原理圖

一個MSP430F2370(32kB閃存,2kBRAM)顯示在圖4-1中。最小MCU需求取決于應用要求和編碼風格。如果只需支持一個ISO協議或者一個協議的有限命令集,則對于MCU閃存和RAM的要求將會大大減少。請注意遞歸目錄和防沖突命令比單槽運行要求更多的RAM。例如,ISO15693(含主機接口)目前的基準固件大約為8kB,使用512BRAM;對于所有支持的協議(具有同樣的主機接口),此基準固件接近12kB并且最少使用1kB的RAM。為了實現直接模式0運行需要一個GPIO運行頻率能達到13.56MHz的MCU。

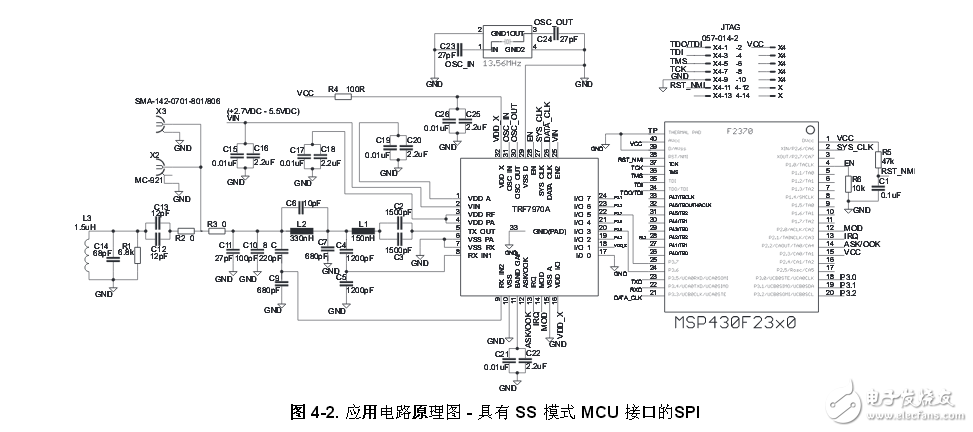

TRF7970A使用包含從器件選擇(SS)模式的SPI讀取器系統

圖顯示了針對使用串行端口接口(SPI)的ISO15693和ISO14443系統而進行了優化的TRF7970A應用電路原理圖。較短的SPI線路,無線電設備頻率線路的正確隔離,和一個恰當的接地區域對于避免干擾十分重要。DATA_CLK線路上的推薦時鐘頻率為2MHz。匹配至一個50Ω端口,這樣可實現到一個適當匹配的50Ω天線電路或者RF測量設備的連接(例如,一個頻譜分析儀或者一個功率計)。電路原理圖顯示了一個具有SS模式MCU接口的SPI的示例應用電路原理圖。

一個MSP430F2370(32kB閃存,2kBRAM)圖。最小MCU需求取決于應用要求和編碼風格。如果只需支持一個ISO協議或者一個協議的有限命令集,則對于MCU閃存和RAM的要求將會大大減少。用戶應該注意遞歸目錄/防沖突命令比單槽運行要求更多的RAM。例如,ISO15693(含主機接口)目前的基準固件大約為8kB,使用512BRAM;對于所有支持的協議(具有同樣的主機接口),此基準固件接近12kB并最少使用1kB的RAM。為了實現直接模式0運行需要一個GPIO運行頻率能達到13.56MHz的MCU。

評論