FPGA航空總線協議接口電路解析

數據總線是飛機航電系統中首先運用的數字電子設備之一,其典型代表是飛機內部時分制指令/響應式多路傳輸數據總線MIL-STD-1553B。它利用一條屏蔽的雙絞線進行帶有時鐘信息的數據傳輸。高可靠性1553B已成為我國航空航天領域廣泛采用的軍用總線標準。由于1553B總線協議控制器基本依賴于進口的專用器件,價格昂貴,還受到限制,并且這些器件需要外圍的硬件電路配合工作,如果完成整個總線接口板的設計,還需要單獨的MCU,集成度不高,這樣就在某種程度上限制了設計能力。隨著嵌入式技術的發展,可編程片上系統設計 SoPC技術已廣泛應用于諸多領域。這里采用SoPC技術,以Virtex-II Pro FPGA為核心,實現1553B航空總線傳輸協議的接口邏輯設計。

本文引用地址:http://www.j9360.com/article/201710/369307.htm1553B航空總線傳輸協議標準

目前廣泛采用的1553B標準是根據1973 年軍標1553原版基礎上發展。1553B是一種集中控制式、飛機內部時分指令/響應型多路串行數據總線標準。具有高可靠性和靈活性。已經成為現代航空機載系統設備互聯的關鍵技術。廣泛應用于飛機、艦船等武器平臺。1553B數據總線的傳輸速率為1Mb/s,協議規定3種字:命令字、數據字和狀態字。字的長度為20 bit,且由同步頭(3 bit)消息塊(16 bit)和奇偶位(1 bit)3部分組成。信息量最大長度為32。總線系統由一個總線控制器(BC)與不多于31個的遠程終端(RT)組成,有時系統中還可加入總線監控器 (MT)。總線上傳輸的信息格式主要有BC到RT,RT到BC,RT到RT,以及廣播方式和系統控制方式。

系統設計

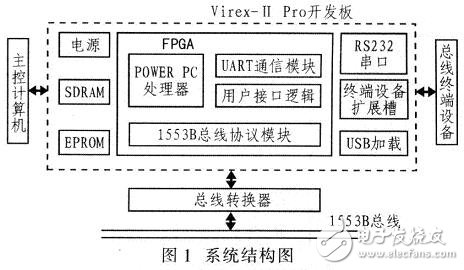

該系統采用Xilinx公司的Virtex-II Pm XC2VP30 FPGA為核心,該器件內部帶有2個PowerPC 405處理器核。總線接口協議實現是基于Xilinx Virtex-II Pro開發系統平臺,Virtex-II Pro開發平臺是整個系統的核心。這樣可以快速搭建1553B總線實現平臺。系統的硬件平臺主要由Vinex-II Pro開發板、總線轉換器、總線終端設備和主控計算機構成,系統結構如圖1所示。

在系統開發中,為了提高開發效率,同時系統主要驗證的就是1553B總線協議模塊,因此可充分利用Xilinx公司的Virtex-II Pro開發板。開發板上具有豐富的資源,主要包括:XC2VP30器件、SDRAM (可擴展到2 GB)、高速SelectMAPFPGA配置PROM、RS232串口、嵌入平臺的USB配置端口、高速系統擴展接口(與FPGA的I/O引腳相連)并可選擇差分或單端模式、PS2接口、AC97音頻接口、板上10/100 M以太網設備等等。這些豐富的板上資源為1553B總線協議邏輯的開發提供支持。

1553B總線協議開發主要在FPGA器件中開發,因此FPGA本身性能的好壞將影響系統的開發。XC2VP30內部具有2個PowerPC 405處理器核、13 969個Slices、分布式RAM為428 KB、136個乘法器單元、塊RAM為2 448 KB、8個DCM、8個多吉比特收發器。因此,選用XC2VP30FPGA完全滿足1553B總線邏輯開發需求。

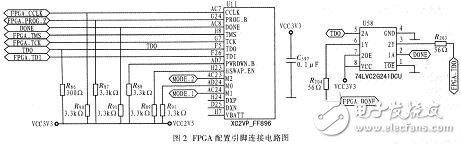

該系統設計采用Virtex-II Pro系列XC12VP30型FPGA,而FPGA的配置則是硬件設計中很關鍵的問題。FPGA配置是對其內容進行編程。采用SRAM工藝的FPGA,每次上電后都需重新配置。XC2VP30通過模式引腳選擇配置模式,其中M2、M1和M0是專用引腳,HSWAP_EN和配置模式引腳相組合,決定I/O引腳在配置過程中是否具有上拉功能。默認情況下,HSWAP_EN置為高電平,此時在配置過程中關閉I/O引腳的上拉功能;當其置為低電平時,I/O引腳具有上拉功能。當選擇某些配置模式時,CCLK可作為FPGA的信號輸出引腳,也可作為外部時鐘的輸入信號,這些引腳不受VCCO的影響,而是采用2.5 V的輔助電源(VCCAUX)。

圖2給出的是FPGA配置引腳連接電路圖。XC2VP30支持5種配置模式,分別是 Slave-serial模式、Master-serial模式、Slave SelectMAP模式、MasterSelectMAP模式和Boundary-Scan (IEEE 1532/IEEE 1149)模式。通過調整配置引腳MO、M1、M2調整配置模式。該系統設計只提供兩種配置模式,在XC2VP30的配置電路中將M0引腳拉為高電平,這樣只能選擇MasterSelectMAP模式和Boundary-Scan模式(即邊界掃描模式)。Master SelectMAP模式是SelectMAP模式的主版本模式,在由XC2VP30所提供的CCLK信號的作用下,器件通過字節寬度數據總線即配置器件 XCF32P的[D7:D0],除了CCLK是由FPGA提供之外,配置時序與Slave SelectMAP模式相似。在邊界掃描模式下,XC2VP30通過專用配置引腳CCLK,DONE,PROG_B,TDI,TDO,MS,TCK按照 IEEE 1149.1標準進行配置。

采用基于SoPC的設計方法,完成了MIL-STD-1553B航空總線接口邏輯的開發,并利用儀器測試系統。將該系統設計的總線協議接口邏輯固化到 FPGA中。可取代國外進口的專用1553B總線控制器器件,從而擺脫長期依賴于國外進口器件的束縛,具有良好的軍事和經濟效益。該系統的創新之處是采用先進的SoPC技術開發FPGA,全面實現1553B總線接口邏輯,系統具有配置靈活,易于擴展等特點。

評論