FPGA芯片最小系統電路設計攻略 —電路圖天天讀(103)

FPGA是英文Field Programmable Gate Array 的縮寫,即現場可編程門陣列。FPGA利用它的現場可編程特性,將原來的電路板級產品集成為芯片級產品,縮小體積,縮短系統研制周期,方便系統升級,具有容量大、邏輯功能強,提高系統的穩定性的同時兼有高速、高可靠性。可以在數字系統設計中完全由用戶通過軟件進行配置和編程,從而完成某種特定的功能。要研究的是Altera 公司推出的一款FLEX10K 系列芯片,通過學習該芯片的工作原理和使用特性,設計一個基于FLEX10K 芯片的最小系統,通過對該最小系統的設計讓大家能夠更好的了解FPGA,并對其產生濃厚的興趣,為更多想要了解學習FPGA 的人們做個很好的開頭。

本文引用地址:http://www.j9360.com/article/201710/369304.htm復位和晶振電路原理圖設計

一個芯片,尤其是可編程芯片,通常在上電的瞬間需要一個短暫的時間進行內部參數的初始化,這個時候芯片無法立即進入工作狀態。通常稱上電初始化這些工作為復位,完成這個功能的電路稱之為復位電路。本FPGA 芯片使用的是低電平復位,支持上電復位和手動復位,RESET 按下之后產生低電平。

圖4-2 復位電路原理圖設計

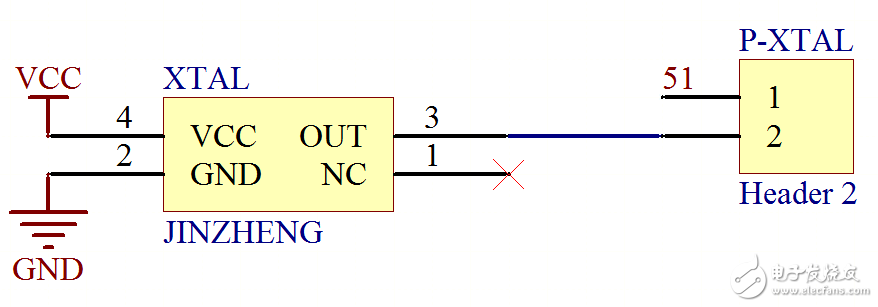

晶振是為電路提供頻率基準的元器件,通常分成有源晶振和無源晶振兩個大類,無源晶振需要芯片內部有振蕩器,并且晶振的信號電壓根據起振電路而定,允許不同的電壓,但無源晶振通常信號質量和精度較差,需要精確匹配外圍電路(電感、電容、電阻等),如需更換晶振時要同時更換外圍的電路。有源晶振不需要芯片的內部振蕩器,可以提供高精度的頻率基準,信號質量也較無源晶振要好。本FPGA 芯片采用50MHZ 的有源貼片晶振作為芯片工作的時鐘輸入(圖4-3)。

圖4-3 晶振電路原理圖設計

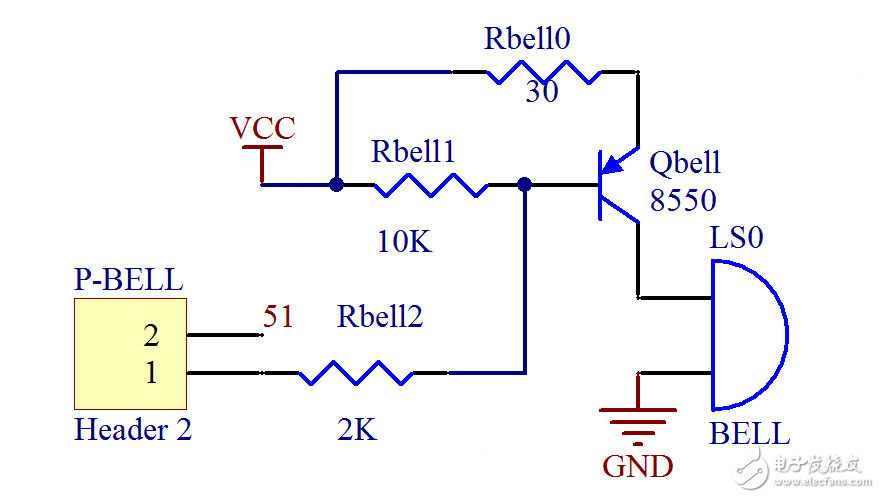

蜂鳴器電路原理圖設計

電路很簡單,需要說明的是開發板上使用的是高品質的蜂鳴器,需要脈沖控制其發聲。電路圖中的晶體管當作開關來使用,當I/O 提供的驅動能力不夠的時候,晶體管能增強驅動能力。低電平有效(圖4-4)。

圖4-4 蜂鳴器電路原理圖設計

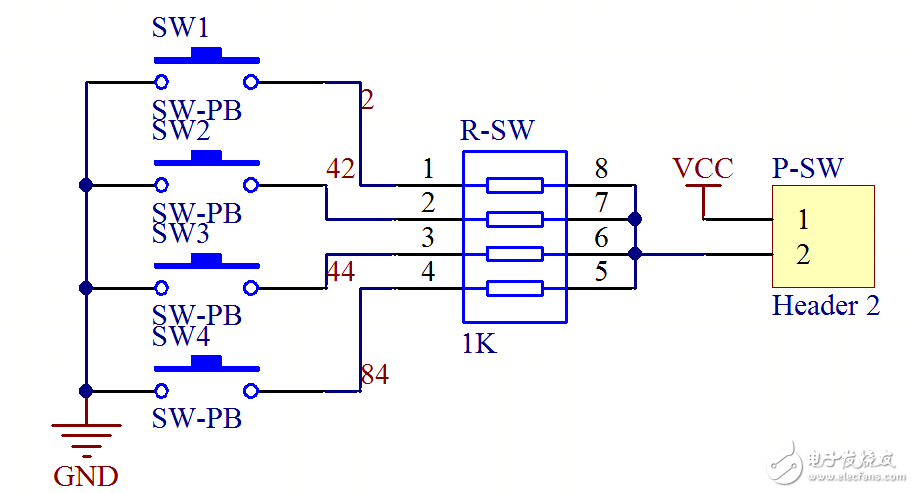

開關電路原理圖設計

最小系統板上使用的四腿按鍵實際上是分兩組,每組中的兩個是相通的,而兩組直接是通過上面的按鈕來控制通斷狀態的。簡單理解成開關就可以了,按下去兩端就形成短路,松開手就形成開路。短路相當于輸入0,開路為1。另外需要說明的是,由于按鍵屬于機械開關,按動過程不可避免存在抖動的現象,所以用戶按下按鍵的時間可以稍微長一點(圖4-5)。

圖4-5 按鍵開關電路原理圖設計

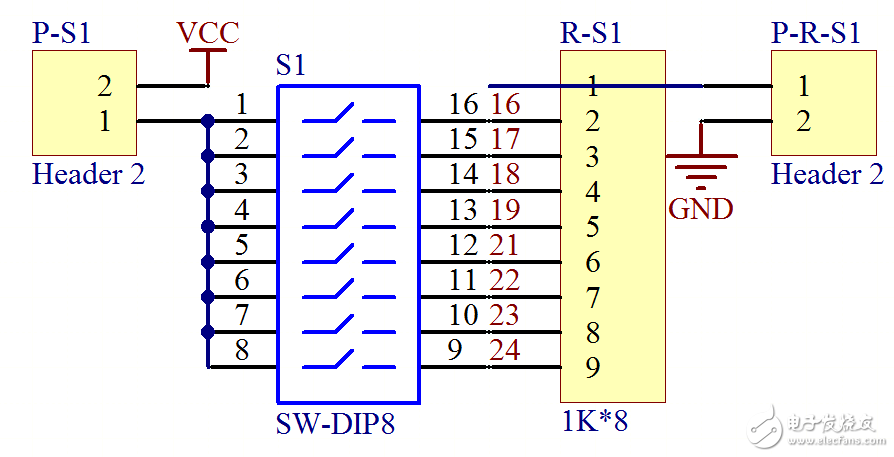

撥碼開關就是相當與一個開關量,撥到ON 就表示接通,OFF 就是斷開,在數字電路中對 0、1,通常用于二進制輸入。本課題最小系統板使用八位撥碼開關作為一個字節的輸入,撥到ON 時相當于輸入“1”,默認輸入“0”(圖4-6)。

圖4-6 八位撥碼開關電路原理圖設計

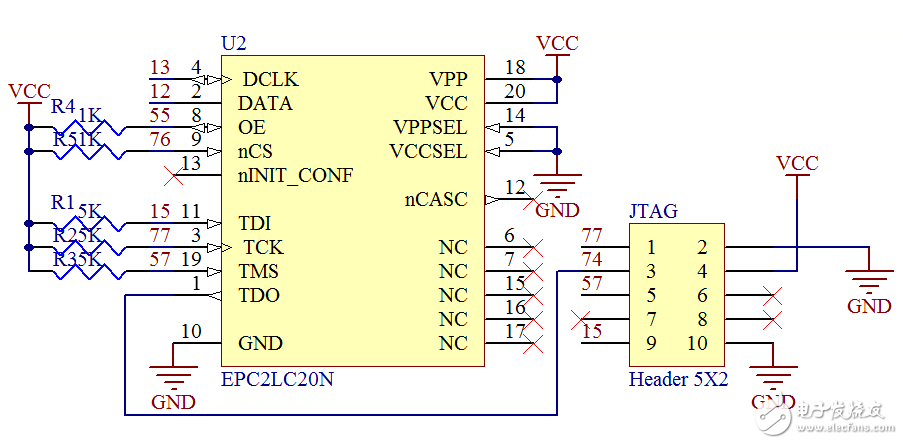

JTAG 模式配置電路原理圖設計

最小系統采用的FPGA 是Altera 公司的FLEX10K10 芯片,所以配置的PROM 選用的型號為EPC2LC20N,是20 腳的PLCC 封裝,上拉電阻R4 是1K,其余的上拉電阻均是5K,TDI、TCK、TMS 和TDO 分別于JTAG 標準接口相連,完成配置電路的設計(圖4-13)。

圖4-13 JTAG 模式配置電路原理圖設計

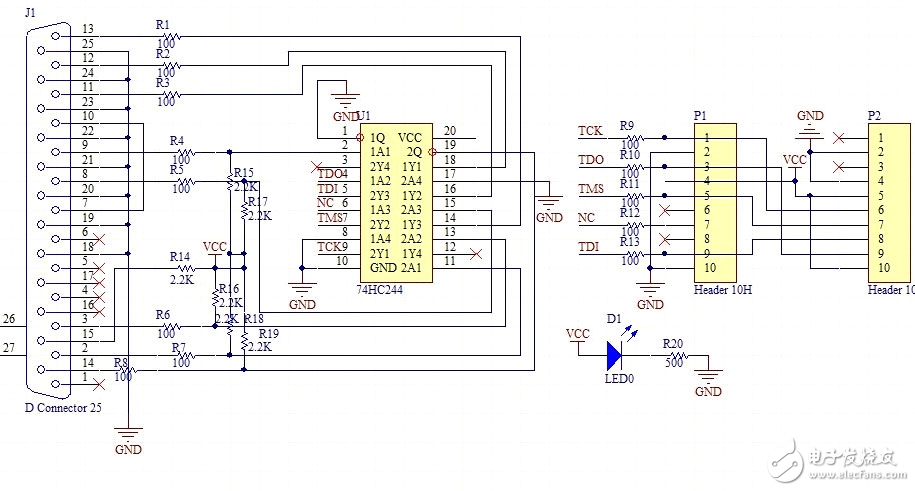

D 型并口下載線電路原理圖設計

此下載線是由一個D 型25 針的并口與計算機相連接,10 針的一端與電路板相連接,數據的下載通過計算機直接配置,此下載線可以支持2.5V、3.3V 及5.0V 電壓的下載模式,是一種可以通用型的下載線(圖4-15)。

圖4-15 D 型并口下載線電路原理圖設計

最小系統電路設計的總體電路原理圖

使用AlTIum 軟件設計的電路原理圖,FPGA 最小系統板包括時鐘電路、復位電路、電源電路、JATG 電路、PROM 配置電路、顯示模塊電路、開關電路以及各種接口電路(圖4-16)。

圖4-16 最小系統電路設計的總體電路原理圖

電子發燒友網技術編輯點評分析:

在當前國內外信息技術高速發展的今天,電子系統數字化已成為有目共睹的趨勢。從傳統的應用中小規模芯片構成電路系統到廣泛地應用單片機,直至FPGA 在系統設計中的應用。電子設計技術已邁人了一個全新的階段。FPGA 利用它的現場可編程特性,將原來的電路板級產品集成為芯片級產品,縮小體積,縮短系統研制周期,方便系統升級,具有容量大、邏輯功能強,提高系統的穩定性,而且兼有高速、高可靠性。越來越多的電子設計人員使用芯片進行電子系統的設計,通過基于FPGA 最小系統開發設計,說明了FAPG 芯片研究的動機和研究意義。

大家如有問題,歡迎在評論處討論。

——電子發燒友網整理,轉載請注明出處!

----------------------------------------

以連接器資料集錦——洞悉連接器現狀與趨勢!

評論