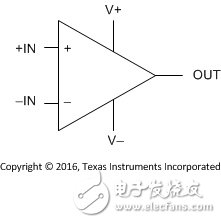

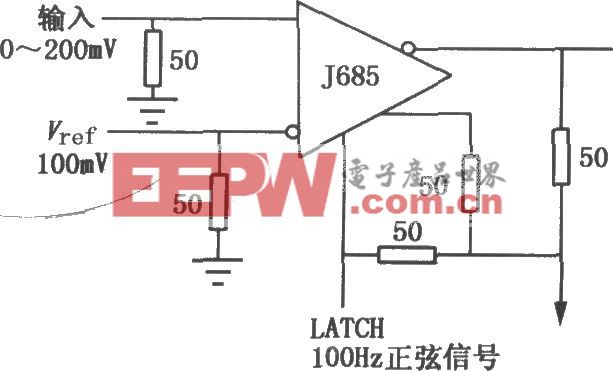

TLV3501比較器電路原理圖、參數封裝與應用

TLV3501電路說明:

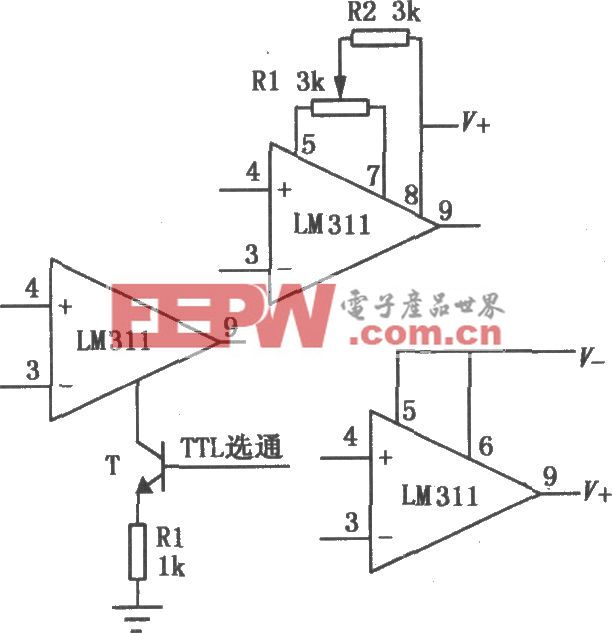

本文引用地址:http://www.j9360.com/article/201710/368887.htmTLV350x系列推挽輸出比較器, 有來自快速延遲時間為4.5ns傳播延遲和操作+2.7V至+5.5V,由于超出擺幅輸入共模范圍使其非常適合低電壓應用的理想選擇。軌對軌輸出可直接驅動CMOS或 TTL邏輯。

Microsize軟件包提供的選項為便攜式和空間受限的應用。單(TLV3501)是提供SOT23-6和SO-8封裝。雙(TLV3502)進來的SOT23-8和SO-8封裝。

TLV3501電路參數:

高速率:4.5ns

軌到軌輸入/輸出

提供電壓:2.7 V to 5.5 V

推挽CMOS輸出級

關閉功能(TLV3501獨有)

微型封裝:6引腳SOT - 23(單),8引腳SOT-23(雙)

低功耗電流:3.2mA

TLV3501封裝類型:SOIC8

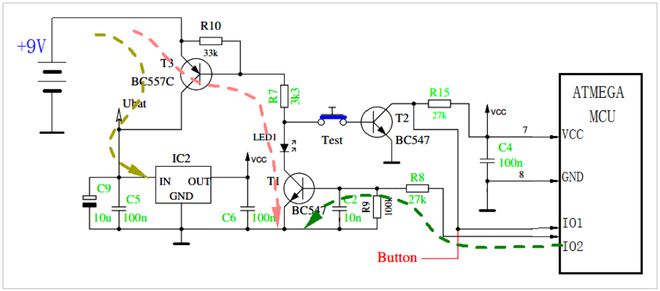

TLV3501電路應用:信號發生器(矢量信號發生器 - VSG) 、電機控制:永久磁性、電機控制:AC 感應、示波器 (DSO)、電機控制:高電壓、透析器 等

評論