基于單片機與FPGA的直接頻率數字合成器的設計方案

1.引言

本文引用地址:http://www.j9360.com/article/201710/367204.htm隨著電子技術的發展,在現代電子產品的故障檢測中,往往需要頻率和幅度都能自動調節的正弦信號源,并且要求該信號源產生的信號頻率穩定性好,轉換速度快,具有調頻、調幅和調相的功能。本文結合實際需要,提出一種基于單片機和FPGA的直接頻率數字合成器的設計方案,能夠產生兩路頻率和相位均可調的正弦波信號,達到了預定的要求。

2.系統方案設計

2.1 系統的性能分析

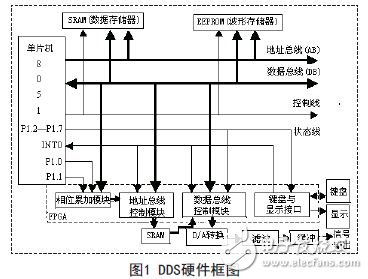

系統主要由單片機最小系統、存儲器電路、FPGA模塊、鍵盤與顯示接口電路、D/A轉換電路、低通濾波電路組成,其硬件框圖如圖1所示。通過鍵盤輸入頻率控制字、相位控制字和幅值控制字,單片機最小系統控制FPGA模塊產生用戶需要的正弦波信號,再經過DA轉換,最后通過低通濾波器生成平滑的正弦波信號。

系統的性能要求:頻率范圍20Hz~20KHZ,步進20Hz;差0o~359o,步進1o;兩路輸出正弦波信號,峰峰值分別在0.3V~5V變化;數字顯示頻率、相位差。

2.2 系統實現的原理

2.2.1 DDS的基本原理

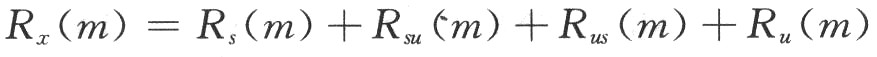

直接數字頻率合成器(DDFS)的基本原理:

DDS是利用采樣定理,根據相位間隔對正弦信號進行取樣、量化、編碼,然后儲存在EPROM中構成一個正弦查詢表,通過查表法產生波形。

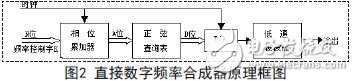

它是由參考時鐘、相位累加器、正弦查詢表和D/A轉換器組成,如圖2所示。

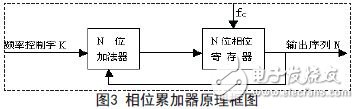

相位累加器由N位加法器與N位累加寄存器級聯構成,其原理框圖如圖3所示。每來一個時鐘脈沖Fc,N位加法器將頻率控制數據K與累加寄存器輸出的累加相位數據相加,把相加后的結果Y送至累加寄存器的輸入端。累加寄存器一方面將在上一時鐘周期作用后所產生的新的相位數據反饋到加法器的輸入端,以使加法器在下一時鐘的作用下繼續與頻率控制數據K相加;另一方面以相加后的結果形成正弦查詢表的地址,取出表中與該相位對應的單元中的幅度量化正弦函數值,作為取樣地址值送入幅度/相位轉換電路。這樣就可把存儲在波形存儲器內的波形抽樣值(二進制編碼)經查找表查出,完成相位到幅值轉換。波形存儲器的輸出送到D/A轉換器,D/A轉換器將數字量形式的波形幅值轉換成所要求合成頻率的模擬量形式信號。

相位累加器的最大計數長度與正弦查詢表中所存儲的相位分隔點數相同,在取樣頻率(由參考時鐘頻率決定)不變的情況下,由于相位累加器的相位增量不同,將導致一周期內的取樣點數不同,輸出信號的頻率也相應變化。

如果設定累加器的初始相位,則可以對輸出信號進行相位控制。由采樣原理可知,如果使用兩個相同的頻率合成器,并使其參考時鐘相同,同時設定相同的頻率控制字、不同的初始相位,那么在原理上就可以實現輸出兩路具有一定相位差的同頻信號。

2.2.2 FPGA實現的直接數字頻率合成器

基于DDS的基本原理,利用Altera公司的FPGA芯片FLEX10系列器件設法將波形采樣點的值依次通過數模轉換器(MDAC)轉換成模擬量輸出,可達到預期的目的,具有較高的性價比。其基本環節由計數器(Counter)、只讀存儲器(EPROM)、數模轉換器(MDAC)和濾波器等組成。

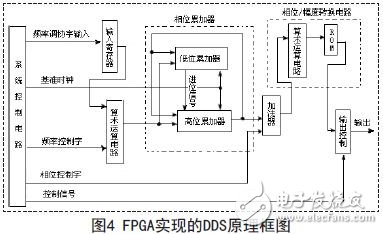

具體方案如下:累加器由加法器和D觸發器級聯組成,在時鐘脈沖fc的控制下,對輸入頻率控制字K進行累加,累加滿量時產生溢出。相位累加器的輸出對應于該合成周期信號的相位,并且這個相位是周期性的,在0~2π 范圍內起變化。相位累加器位數為N,最大輸出為2N-1,對應于2π的相位,累加一次就輸出一個相應的相位碼,通過查表得到正弦信號的幅度,然后經D/A轉換及低通濾波器濾除不需要的取樣分量,以便輸出頻譜純凈的正弦波信號。整個DDS電路的電路結構如圖4所示。

3.系統硬件電路設計

在功能上,單片機與FPGA有很強的互補性。

單片機具有性價比高、功能靈活、易于人機對話、良好的數據處理能力等特點;FPGA則具有高速、高可靠性以及開發便捷、規范等優點。用這兩類器件相結合的電路結構在許多高性能儀器儀表和電子產品中仍將被廣泛應用。

單片機的功能主要是傳送頻率控制字K1和相位控制字K2給FPGA處理;生成波形表存儲于EEPROM中;控制鍵盤的寫入和LED的顯示;控制DAC0832進行幅值轉換。在每次加電前都要通過單片機初始化,將寫好的程序加載在信號產生系統上,然后把從鍵盤上輸入的數據送到中央處理芯片上,信號通過低通濾波器輸出的同時,LED數碼管顯示信號的頻率和相位差。

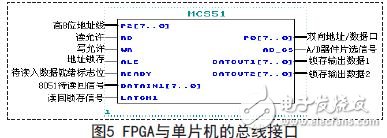

FPGA與單片機的總線接口如圖5所示。

4.系統的實現

4.1 系統的計算與仿真

用MAX+plusⅡ設計DDS系統數字部分最簡單的方法是采用原理圖輸入。相位累加器調用lmp_add_sub加減法器模塊,相位累加器設計的好壞將直接影響到整個系統的速度,采用流水線技術能大幅度地提升速度。波形存儲器(ROM)通過調用lpm_rom元件實現,其LPM_FILE的值。mif是一個存放波形幅值的文件。波形存儲器設計主要考慮的問題是其容量的大小,利用波形幅值的奇、偶對稱特性,可以節省3/4的資源,這是非常可觀的。為了進一步優化速度的設計,可以選擇菜單Assignal GlobalProject Logic Synthesis的選項Optimize10(速度),并設定Global Project LogicSynthesis Style為FAST,經寄存器性能分析最高頻率達到100MHZ以上。DDFS中的分頻、累加器及正弦波的仿真如圖6、7、8所示。

4.2 單片機的編程實現

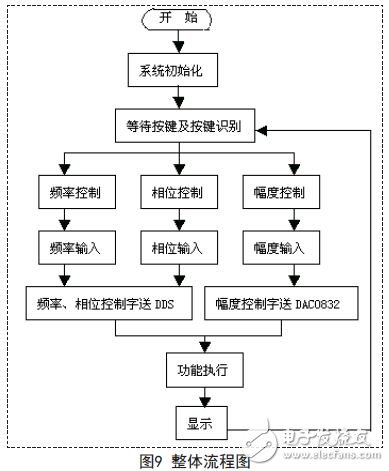

由于使用了8051單片機及FPGA構成的DDS系統,外圍電路變得異常簡單,而FPGA的使用使單片機的程序大大簡化。DDS系統及其與單片機的接口部分用VHDL語言寫。在設計過程中波形頻率隨CPU的頻率而變化,單片機的實時時鐘經過PLL倍頻電路產生系統時鐘頻率fc,fc再經過分頻得到CPU時鐘頻率(CPUCLK)可通過對P_SystemClock(寫)(7013H)單元編程來控制。在設計過程中,波形編輯的第一步就是進行CPU頻率選擇,選擇最高頻和最低頻作為粗調,在用鍵盤和中斷進行微調,以便達到所需的頻率、相位及其幅值。單片機編程的總體流程圖如圖9所示。

5.結束語

本文結合實際需要,提出一種基于單片機和FPGA的直接頻率數字合成器的設計方案。方案以FPGA為核心模塊,以單片機為控制模塊,采用直接數字頻率合成技術設計了雙通道相位關系可調的信號發生器,輸出信號頻率范圍為0~20KHz,頻率分辨率高于20Hz,相位調節步進1o.兩個通道不僅可以輸出相同頻率的信號,還可以輸出不同相位、不同幅值的正弦信號。經系統仿真表明,本方案可達到預定要求,應用方便靈活。

評論