VGA的驅動顯示以及邏輯分析儀的使用

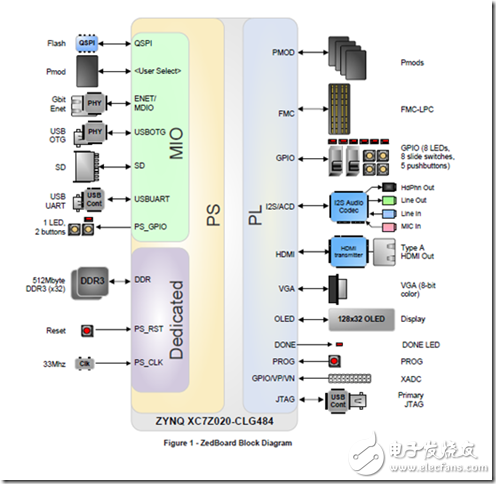

Zedboard的接口框圖如下:

本文引用地址:http://www.j9360.com/article/201710/365508.htm

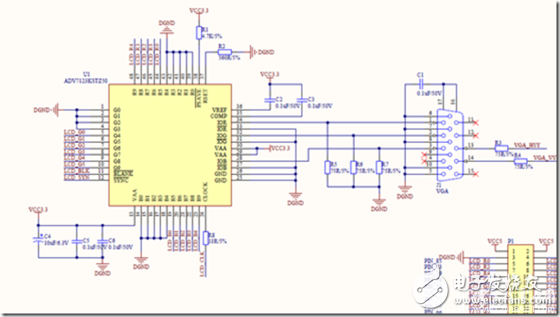

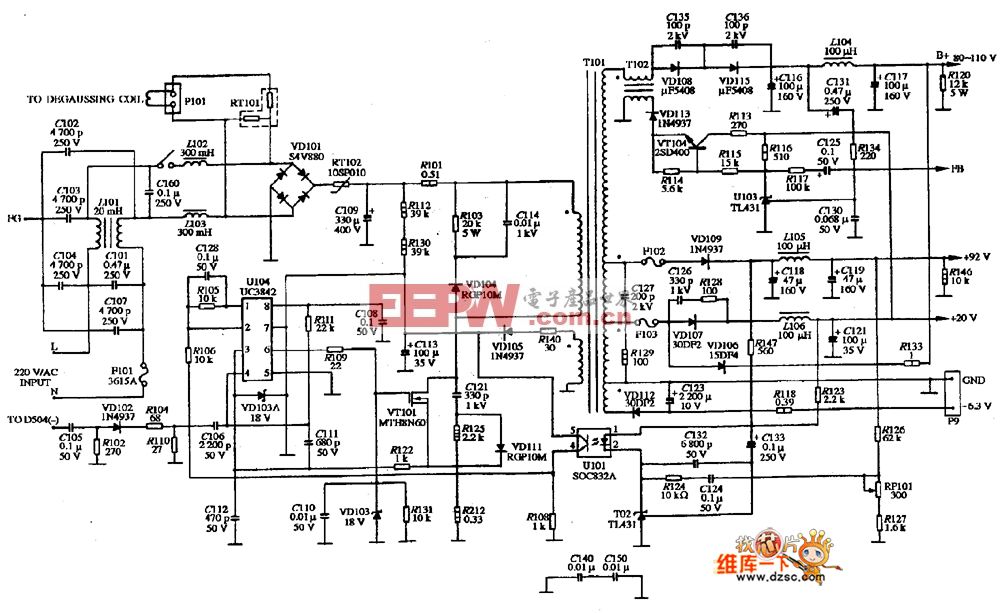

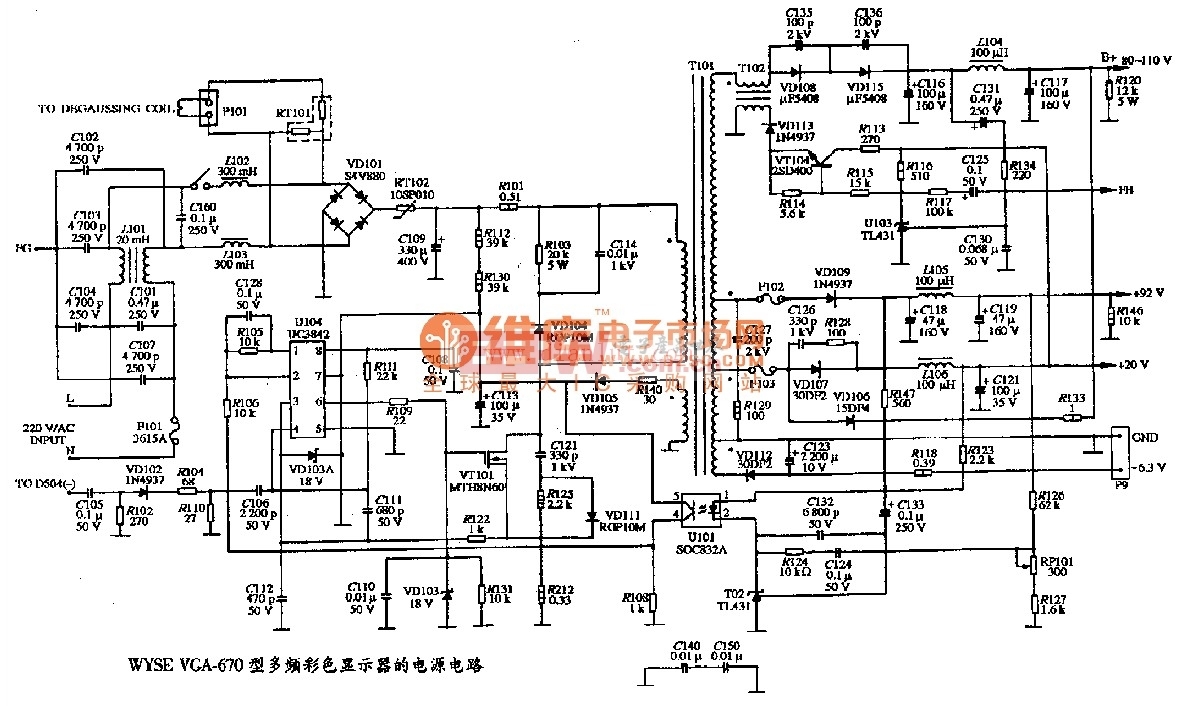

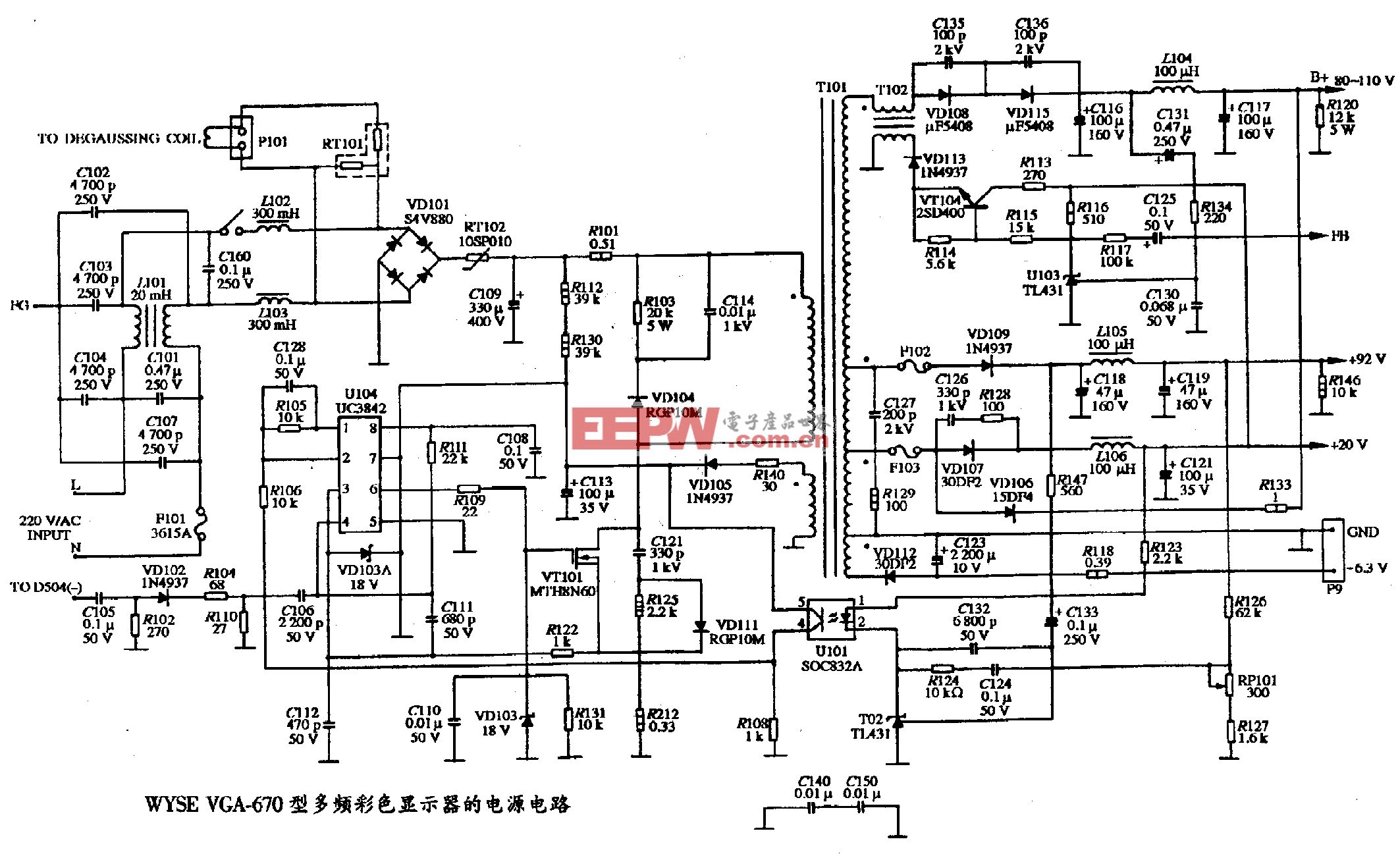

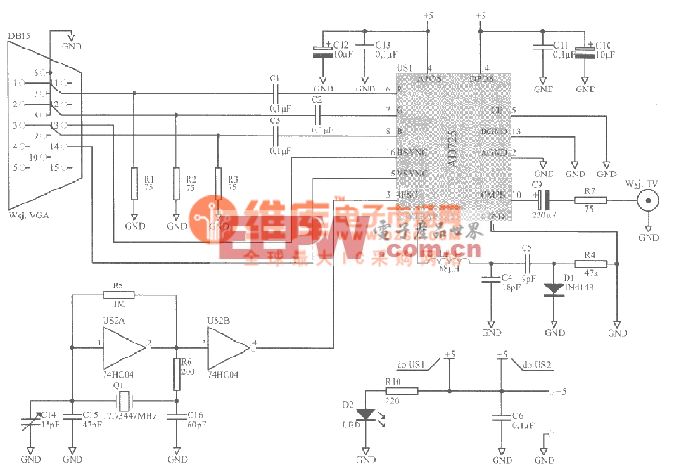

掛在PL側的模塊有HDMI、VGA、OLED等,下面將詳細介紹在Zedboard上驅動VGA的過程,開發環境為Vivado 2016.2。Zedboard是通過權電阻網絡來搭建的DAC電路,

關于VGA的驅動原理,請看下面的時序圖:

程序中就是通過計數器來模擬產生行、場同步信號。這里主要介紹下Vivado的開發流程。Vivado下新建工程,選擇開發板Zedboard,如圖:

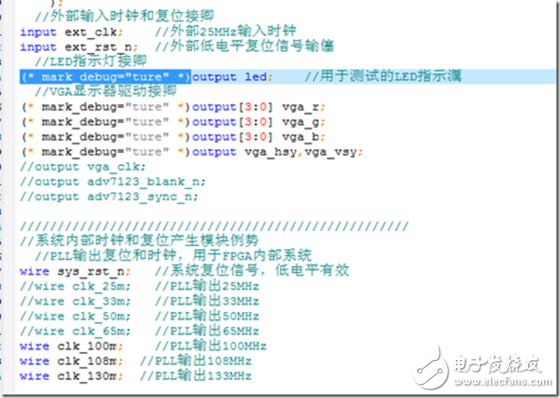

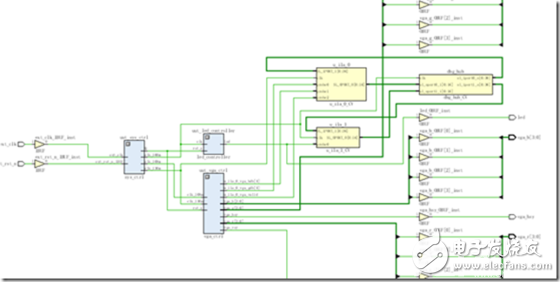

將修改好的工程代碼都加進來,這里通過clock Wizard重新生成所需要的時鐘,方法和quartus大同小異,移植好的工程如圖:

然后執行Run Synthesis、Run ImplementaTIon和Generate Bitstream就可以生成.Bit文件下載到FPGA里了。這里我又想用下在線邏輯分析儀的功能,那么首先需要在代碼里對需要查看波形的信號前加(* mark_debug=ture *),就算該信號在工程中沒有連接,也不會別編譯器優化掉。如圖:

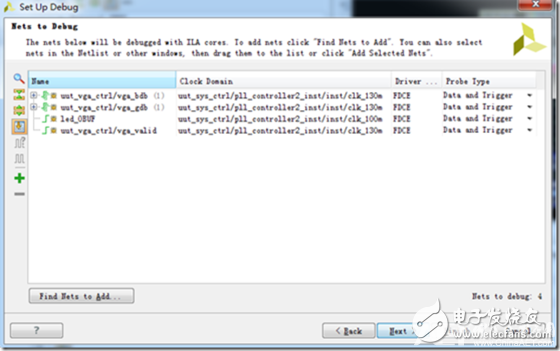

我們將要在邏輯分析儀中觀察VGA的紅、綠、藍信號。選擇Set Up Debug,將感興趣的信號加進來。

注意時鐘域別弄錯了,設置好后,我們發現RTL視圖里多了調試模塊

然后在Hardware Manager中執行 Open Target,連接上目標開發板后,Program device,下載完后,邏輯分析儀窗口就會自動出來。

最后的顯示效果如下:

評論