基于OR1200的SoC程序無線智能加載系統設計及驗證

作者/ 黃誠1 唐明華2 1.湘潭大學 物理與光電工程學院(湖南 湘潭 411105) 2.湘潭大學 材料科學與工程學院(湖南 湘潭 411105)

本文引用地址:http://www.j9360.com/article/201708/363622.htm*基金項目:國家自然科學基金(編號:51472210)

黃誠(1992-),男,碩士生,研究方向:數字電路SoC設計等。

摘要:SoC是當前微電子芯片發展的趨勢,然而由于受帶開發環境的PC終端、額外硬件接口、連接線等條件的約束,很難支持SoC產品的二次開發。本文提出一種SoC無線程序加載系統設計方案,通過無線控制實現不同程序的加載,不需要添加額外的接口與復雜的模塊,不需要連接下載線和IDE開發環境等工具,簡化了芯片的二次開發,增加了芯片的利用率。并且在FPGA板上測試通過。

引言

隨著SoC技術的不斷發展,其產品在市場上的占用比例也越來越大。對于SoC的開發流程,它需要有一套相應的IDE開發工具,包括裝有配套開發環境的PC、硬件接口和連接線。開發完成后應用于嵌入式領域,但是由于受帶開發環境的PC終端、電路板、連接線等條件的約束,一般很難支持二次開發。

為了解決上述技術問題,本文提出一種能方便實現二次開發、芯片利用率高的基于SoC的無線智能程序加載方法。使用帶藍牙功能的終端發送不同的命令即可選擇flash程序區中不同的程序加載到內存模塊,通過無線控制實現不同程序的加載,不需要添加額外的接口與復雜的模塊,不需要連接下載線和IDE開發環境等工具,并提供一種無線智能程序加載SoC系統。經過在FPGA開發板上測試,該方法能很好地應用在智能終端領域中,例如智能玩具小車,主控采用本發明的SoC芯片,就能設定小車的三種工作場景——遙控控制小車、小車自動避障和小車循跡,通過帶藍牙的終端向主控發送相應的命令就能改變小車的工作模式,增加小車的功能。

1 系統總體結構

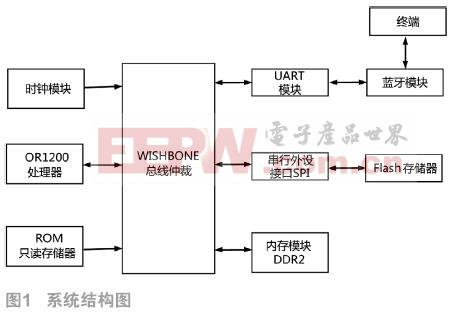

本文中的無線智能程序加載SoC系統包括時鐘模塊、處理器模塊、只讀存儲器ROM模塊、Wishbone總線仲裁模塊、SPI控制器模塊、內存DDR2模塊和通用異步收發傳輸器UART模塊。所有模塊均通過Wishbone總線連接到處理器。總線仲裁采用輪循機制實現主設備與從設備之間的訪問。本系統改變了傳統的把一個程序存儲在flash中,當燒錄下一個程序時就會覆蓋上一個程序的做法,而是把flash劃分成三個程序區,燒錄flash時,把不同的程序放在不同的程序區。當從SPI flash啟動時,程序指針首先指向只讀存儲器ROM里的bootload區,以完成程序從flash拷貝到內存,再從內存開始執行指令。本系統在此基礎上增加了bootload的功能,不僅能完成程序的拷貝,還能監測串口,根據收到的命令選擇一個程序區的程序拷貝到內存,使得芯片封裝好之后,無需接線,無需相應的IDE軟件來加載程序,通過手機或帶有藍牙模塊的終端就可以加載不同的程序,簡化芯片的二次開發,在智能終端領域能有很好的應用。總體框架圖如圖1所示。

2 硬件系統設計

2.1 硬件頂層結構設計

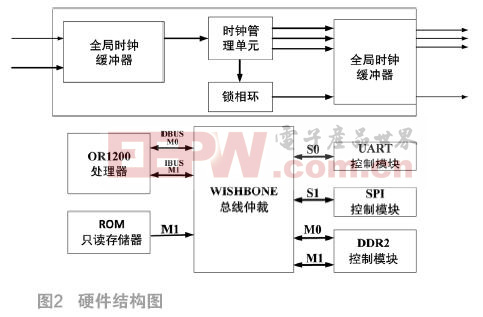

系統硬件頂層采用硬件描述語言Verilog HDL設計,以總線作為分割介質來看整個系統,包括一個主設備和四個從設備。其中主設備為處理器OR1200,從設備為只讀存儲器模塊、內存模塊、串行外設接口模塊和通用異步手法傳輸器模塊。如圖2所示。

2.2 總線仲裁設計

總線仲裁設計主要包含兩組仲裁,一組為處理器中的指令總線IBUS,通過高位地址判斷從只讀存儲器ROM取指令還是從內存模塊DDR2中取指令;另一組為處理器中的數據總線,通過高八位地址判斷訪問哪個外設,具體訪問哪個寄存器通過低位判斷。其中主設備采用輪詢的機制搶占總線,核心設計思想為:統計主設備的個數n,然后定義n位的變量token={00....01},通過一定周期把1向左循環取到每個主設備,而實現仲裁的輪循機制。

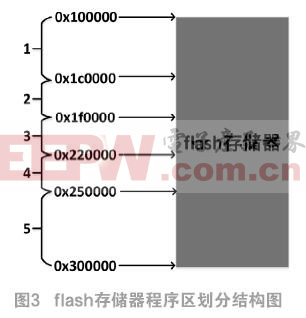

2.3 flash存儲器程序區劃分結構設計

如圖3所示,flash存儲器地址從0x100000到0x1c0000是bit文件放置區1,0x1c0001到0x1f0000是程序區Ⅰ2,地址從0x1f0001到0x220000是程序區Ⅱ 3,地址從0x220001到0x250000是程序區Ⅲ4,地址從0x250001到0x300000是擴展區5。SoC系統bit文件利用Xilinx ISE中的impact工具燒錄進去,其他程序區的程序通過硬件描述語言中的readmemh命令寫入。

3 軟件設計

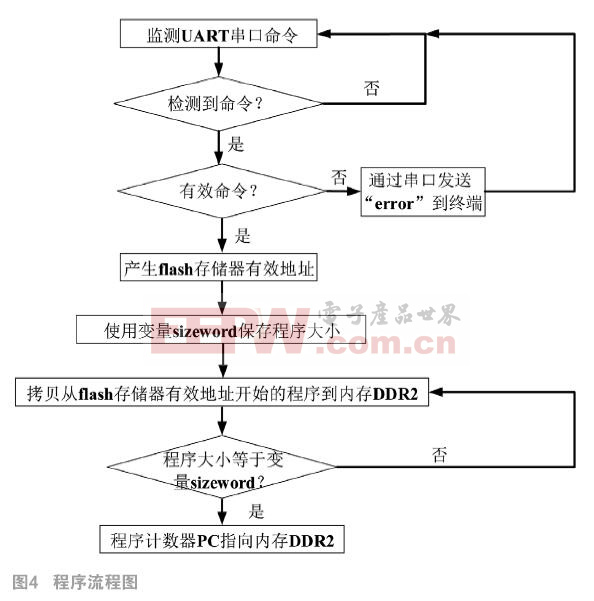

系統在上電啟動的時候,程序指針PC指向只讀存儲器ROM中Bootload區的一段代碼,這段代碼一般完成程序從flash存儲器拷貝到內存,再將程序指針跳轉去內存一條一條執行的功能。本文中的軟件設計在此基礎上增加了改進,如圖4所示。首先優化串行外設接口SPI和通用異步收發傳輸器UART,并實時監測終端發過來的命令;若監測到命令,校驗接收到的命令是否為有效命令,若為有效命令則根據接收到的命令選擇flash存儲器相應程序區的有效地址,否則通過通用異步收發傳輸器UART和藍牙模塊向終端發送“錯誤”提示,繼續等待命令。得到有效的地址后,初始化串行外設接口SPI,產生串行外設接口SPI時序和發送讀命令,根據flash程序區的有效地址拷貝程序到內存模塊DDR2中,直到程序大小等于程序大小變量sizeword的值,最后執行跳轉命令,將處理器指向內存模塊DDR2的起始位置,實現系統的自啟動。程序流程圖如圖4所示。

4 仿真與下板測試

OR1200處理器是OpenRisc家族中的一員,在軟件編譯的時候我們需要安裝OpenRisc交叉編譯工具鏈;采用Xilinx的Virtex-5開發板,同時需要安裝ISE等EDA工具。

編譯工具鏈把前面設計的加載啟動代碼(bootloader)從匯編語言編譯成硬件描述語言,并實例化到SoC系統頂層中。然后進行flash存儲器的分區并燒錄程序,本文通過readmemh命令向程序區Ⅰ、程序區Ⅱ和程序區Ⅲ依次燒錄hellowa.c、hellowb.c和hellowc.c。這幾個測試程序會通過串口分別打印出“Hello word A”、“Hello word B”和“Hello word C”。這樣我們就可以很直觀地判斷系統在執行哪個程序。

將板子上電,并利用Xilinx ISE中的impact工具將編譯好的SoC系統bit文件燒錄至flash存儲器0x100000到0x1c0000區域,當編譯綜合通過,下板成功后,我們就可以抓取波形和串口打印判斷結果。其波形圖和串口打印如圖5和圖6所示。從波形圖中我們可以看出串口控制器輸出14個字符,正好是“Hello World A/B/C”,放大波形我們可以看到第一個數據為0x48,正好是字符“H”的ASCLL碼。而從窗口上打印的輸出更為明顯。給串口發送命令“0”,選擇flash程序區1 hellowa.c,從0x100000開始拷貝程序,仿真測試結果輸出“Hello word A!”。給串口發送命令“1”,選擇flash程序區Ⅱ hellowb.c,從0x130001開始拷貝程序,仿真測試結果輸出“Hello word B!”。給串口發送命令“2”,選擇flash程序區Ⅲ hellowc.c,從0x160001開始拷貝程序,仿真測試結果輸出“Hello word C!”。

5 結論

本發明基于SoC的無線智能程序加載方法中,首先將flash存儲器劃分成若干個程序區,并通過加載指令把不同的程序分別加載到不同的程序區,然后運行加載啟動代碼,初始化串行外設接口并監測串口接收到的命令,從flash存儲器中選擇相應程序區,實現程序到內存模塊的拷貝,最后執行跳轉命令,將處理器指向內存模塊的起始位置,實現系統的自啟動;整個加載過程簡單,不需要接線和留出程序加載接口,也不需要相應的IDE軟件來加載程序,通過手機或帶有藍牙模塊的終端就可以加載不同的程序,適用范圍廣。

參考文獻:

[1]唐明華,黃誠,劉新,等. 一種基于SoC的無線智能程序加載方法及系統. 國家發明專利. 專利申請號: 201610139229.2. 中國,2015.

[2]蘇紀娟,孟祥玲,朱慶明.系統芯片技術國內外發展現狀[J]. 軍民兩用技術與產品. 2015(13).

[3]王龍興.集成電路的過去、現在和將來(一)世界集成電路的發展歷史[J].集成電路應用. 2014(01).

[4]李爭,李范鳴,陳捷,等.基于Wishbone SoC總線接口的高性能SDRAM控制器[J].科學技術與工程. 2008(12).

[5]鄭文靜,李明強,舒繼武. Flash存儲技術[J]. 計算機研究與發展. 2010(04).

[6]陳光武,范多旺,于超,等.基于Wishbone片上總線的IP核的互聯[J].微計算機信息. 2009(20).

本文來源于《電子產品世界》2017年第9期第54頁,歡迎您寫論文時引用,并注明出處。

評論