極點跟隨的LDO穩壓器頻率補償方法

便攜電子設備無論是由蓄電池組,還是交流市電經過整流后(或交流適配器)供電,工作過程中,電源電壓都存在變化。例如單體鋰離子電池充足電時的電壓為4.2 V,放電后的電壓為2.3 V,變化范圍很大。而各種整流器的輸出電壓不僅受市電電壓變化的影響,還受負載變化的影響。因而近年來,低壓差線性穩壓器(LowDropout Linear Regulator)以其低成本,高電池利用率,潔凈的輸出電壓等特點,被廣泛應用于移動電話、掌上電腦等消費類電子產品,以及便攜式醫療設備和測試儀器中。

LDO|0">LDO穩壓器的頻率補償設計,不僅直接決定了頻率穩定性,而且對LD0穩壓器的性能參數,尤其是瞬態響應速度,有很大的影響。此外,隨著當前半導體集成電路工藝的發展,越來越多的功能電路能夠被集成于單一芯片中,而現有的LDO穩壓器頻率補償技術,對芯片上頻率補償電容的需要,大大阻礙了LDO穩壓器芯片集成度的提高和與其他功能電路的系統集成。

本文對LDO穩壓器的頻率穩定問題,和現有的頻率補償設計技術進行了理論分析。在此基礎上,提出了一種新型的頻率補償方法,并給出了電路實現途徑。通過一個采用TSMC0.18 μm混合信號半導體工藝,最大輸出電流為100 mA的LDO穩壓器設計,對該方法做出了進一步的說明。最后,結合LDO穩壓器的HSpice仿真結果,對本文提出的頻率補償方法的效果進行了討論。

2 LDO穩壓器頻率補償

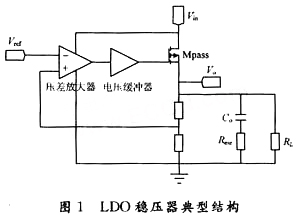

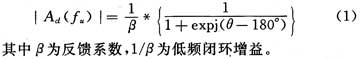

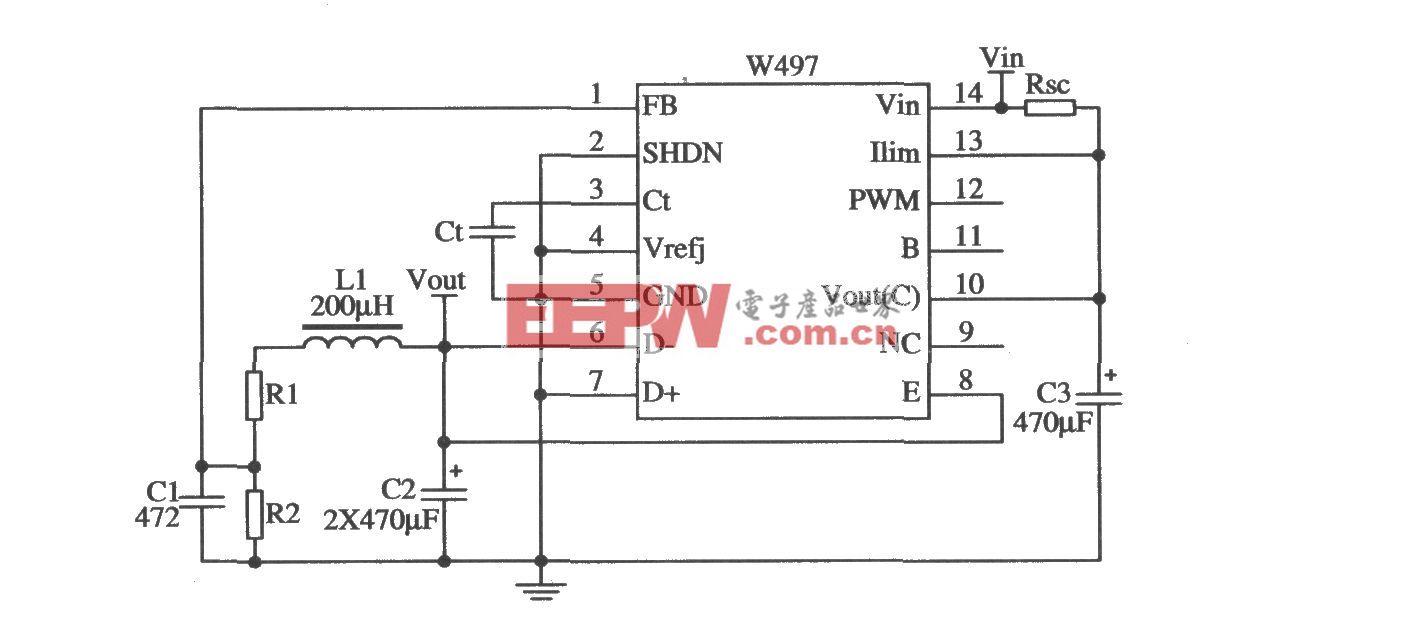

LDO穩壓器的典型結構,如圖1所示。圖1中,Vref為具有良好溫度特性的電壓參考信號,Vin為不穩定的輸入電壓信號,Vo為輸出電壓信號。LDO穩壓器利用由壓差放大器、電壓緩沖器、電壓調整管Mpass和反饋網絡構成的負反饋環路,維持Vo穩定。

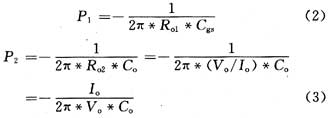

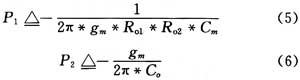

圖1中存在兩個低頻極點,分別為位于電壓緩沖器輸出端的極點P1,和LDO穩壓器輸出端的極點P2。P1與P2的值由電壓緩沖器的輸出等效電阻Ro1,Mpass的柵、源極電容Cgs,LDO穩壓器輸出端的等效電阻Ro2和外接電容Co決定:

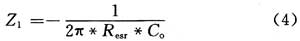

傳統LDO穩壓器的頻率補償方法,如圖1所示,利用了輸出端電容Co及其等效串聯電阻Resr,產生一個左半平面(LHP)零點Z1:

由于以上原因,當前的LDO穩壓器,多采用內部頻率補償。一類內部頻率補償技術借鑒了傳統LDO穩壓器的零、極點抵消方法,并利用前饋技術,或芯片內部的RC網絡和電壓控制電流源,產生所需的零點。但是,要做到芯片內產生的零點與相應極點的完全匹配,是非常困難的。而未能相互抵消的零點和極點,會成為LDO穩壓器通帶內的零、極點對(doublet),造成Vo建立時間的增加。另一類廣泛使用的內部頻率補償為米勒頻率補償。米勒補償具有極點分離的特性,即通過跨接在Mpass柵極和漏極的米勒電容Cm,將P1推向低頻,P2推向高頻。米勒補償后,P1與P2由式(2)、式(3)變為:

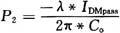

由式(5),欲使P1遠小于P2,則Cm會很大,電路內部對其充放電的過程造成Vo的壓擺時間tsr變長。因Co很大,由式(6),P2處于低頻,限制了增益帶寬GBW。米勒補償對tsr和GBW的影響,直接增大了LDO穩壓器的環路延時td(參看式(7))。雖然通過嵌套的米勒頻率補償方法或電容倍增電路,能夠減小Cm,但未能根除Cm對LDO穩壓器芯片的集成度的影響。

3 極點跟隨頻率補償

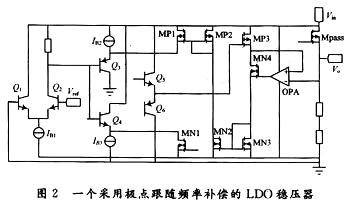

LDO穩壓器空載時,由式(3),P2為0 Hz(實際上,此時

,λ和IDMpass為Mpass的溝道調制系數和漏極電流),P1只需大于0 Hz,P1與P2的間距(P1/P2)就足以保證頻率穩定性。隨著輸出電流的增大,P2向高頻移動,如果P1能夠跟隨P2的變化,則P1與P2的間距得到維持。極點跟隨的頻率補償,即是當輸出電流變化時,通過使P1跟隨P2的變化,獲得頻率穩定性的方法。

,λ和IDMpass為Mpass的溝道調制系數和漏極電流),P1只需大于0 Hz,P1與P2的間距(P1/P2)就足以保證頻率穩定性。隨著輸出電流的增大,P2向高頻移動,如果P1能夠跟隨P2的變化,則P1與P2的間距得到維持。極點跟隨的頻率補償,即是當輸出電流變化時,通過使P1跟隨P2的變化,獲得頻率穩定性的方法。 一種使P1跟隨P2變化的電路實現,可利用共集電極和共漏極電壓緩沖器的輸出電阻,分別與偏置電流和偏置電流的開方成反比的規律,根據輸出電流來動態地調整電壓緩沖器的偏置電流,使P1也受輸出電流控制。

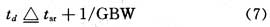

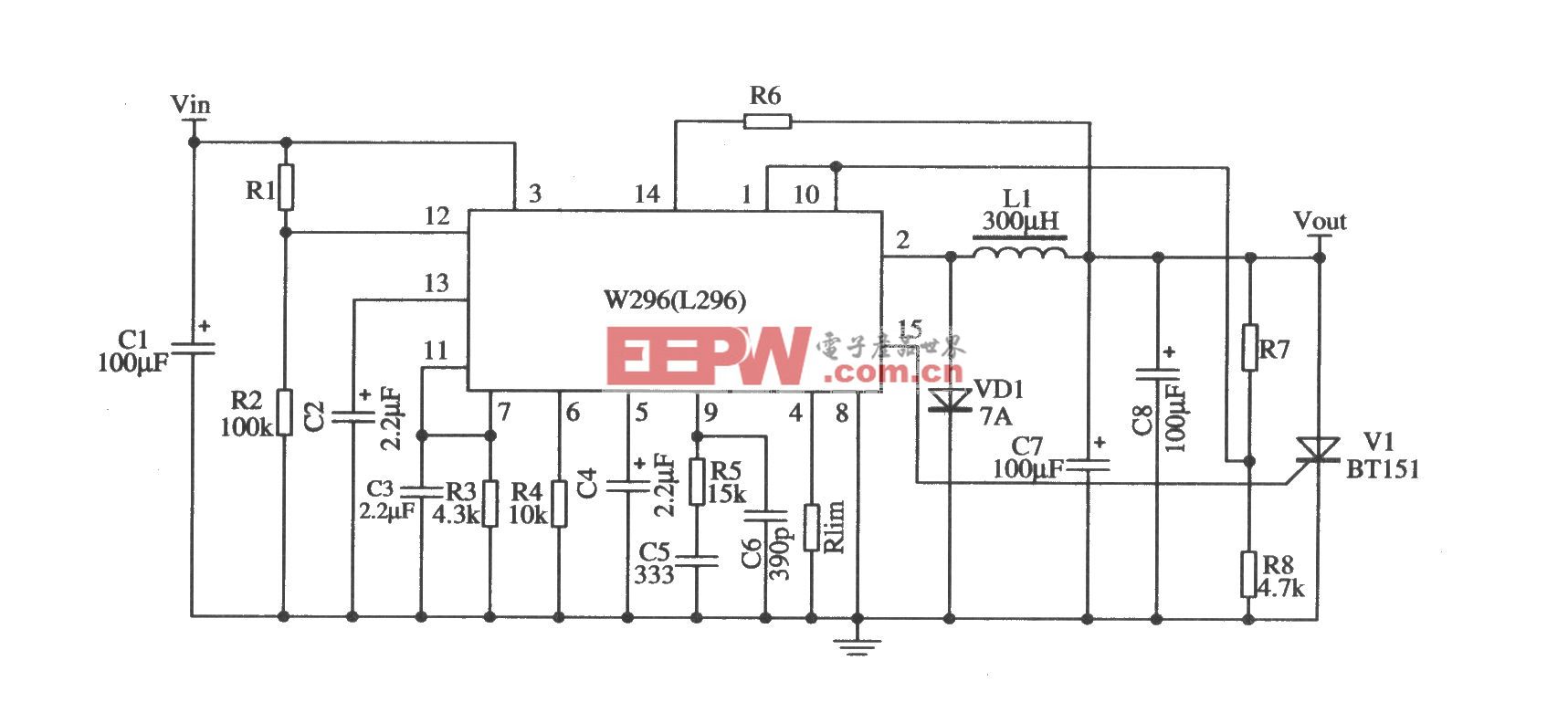

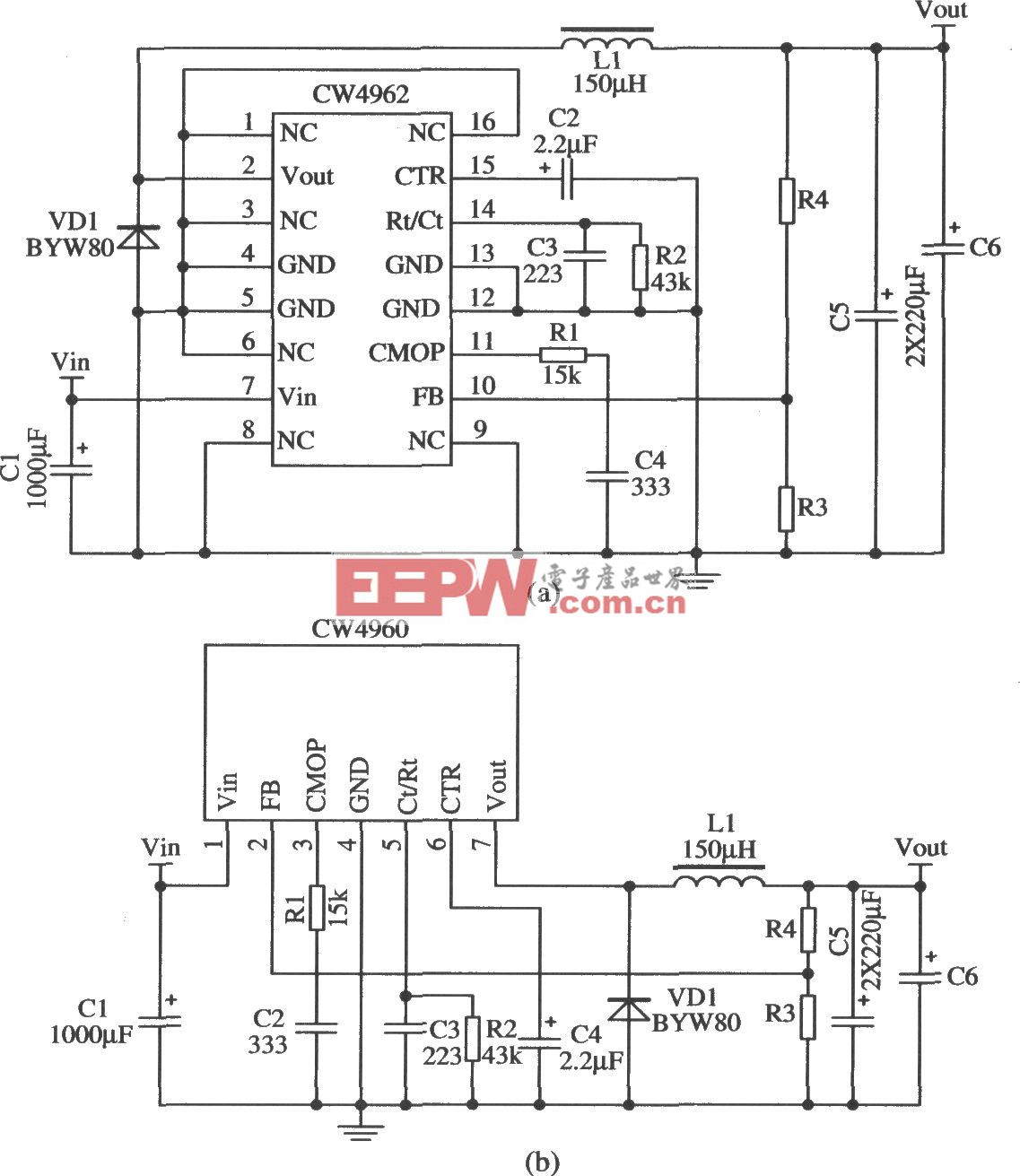

一個采用了極點跟隨頻率補償的LDO穩壓器,如圖2所示。其中,完成頻率補償的動態偏置電壓緩沖器,包括了由MOS晶體管MP3,MN4和運算放大器OPA組成的輸出電流監測電路,由MN1~MN3和MP1~MP2組成的電流鏡電路,以及由電流源IB2,IB3和雙極晶體管Q3~Q6組成的電壓緩沖器。

4 仿真結果與討論

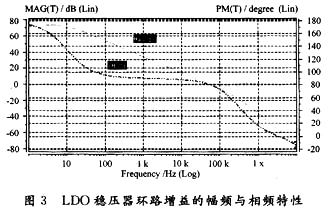

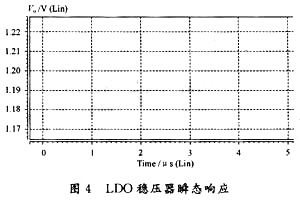

采用TSMC 0.18 μm混合信號Spice模型,和高精度仿真工具HSpice,對圖2中的LDO穩壓器進行了設計與仿真驗證。在Co=1 μF,Io=100 mA的條件下,環路增益T的幅頻與相頻響應的仿真結果如圖3所示,在單位環增益頻率內,幅頻特性與單極點系統相同,以-20 dB/dec的速度衰減,相位裕度大于80°。

5 結語

本文提出的極點跟隨的頻率補償方法,提供了LDO穩壓器良好的頻率穩定性和瞬態響應,且無需芯片上頻率補償電路,因而不僅適用于高負載變化響應速度的單芯片LDO穩壓器,在集成電源管理和片上系統(SOC)方面,也有較好的應用前景。

評論