CPLD MAX II低成本架構

在高密度應用環境下,基于查找表(LUT)的LAB和行、列布線模式具有更高的裸片尺寸/成本效率。由于MAX II CPLD基于LUT架構,達到了降低成本的目的,結合其即用性、非易失性和可再編程特性,使MAX II 系列成為有史以來成本最低的CPLD。

注釋:

隨著LAB數量的增加,布線資源指數性的增長,使得布線資源主導裸片面積

隨著LAB數量的增加,布線線形增長,獲得高效的裸片面積

低成本設計

MAX II器件的構造采用了低成本設計方法,首先它選擇了一種流行的低成本的封裝。通過使用限制焊盤面積的,錯列I/O焊盤方案,獲得單個I/O成本最低的管腳方案,從而實現最小的裸片尺寸。其次,該器件在I/O引腳所包圍的環內組裝了最大數量的LE。這種基于LUT的架構在I/O約束的最小的空間內獲得了最大可能的邏輯容量。

MAX II架構

突破性的新型MAX II CPLD架構包括基于LUT的LAB陣列、非易失性FLASH存儲器塊和JTAG控制電路(見圖2)。多軌道連線設計采用了最有效的,直接將邏輯輸入連接到輸出的連線,從而獲得了最高的性能、最低的功耗。更多關于MAX II架構的詳細信息可參見MAX II器件系列數據手冊。

與QuartusII軟件設計一致性

為簡化設計優化過程,MAX II器件架構和Quartus® II軟件裝配算法保持精確的一致性,在管腳鎖定時優化tPD、tCO、tSU和fMAX性能。當設計的功能改變時,Quartus II軟件采用管腳鎖定約束和按鈕式編譯流程,提高了滿足或超過性能要求的能力。免費的Quartus II基礎版軟件支持所有MAX II器件。

電壓靈活性

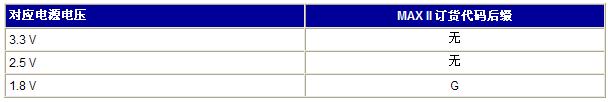

MAX II架構支持MultiVolt™內核,該內核允許器件在1.8V、2.5V或3.3V電源電壓環境下工作。目前對應電源電壓有兩個器件系列可選(見表1和圖3)。該特性使設計者得以減少電源電壓種類數量,簡化板級設計。

圖3. MultiVolt內核操作

注釋:

VCCINT = 1.8 V 旁路調節器

MAX II器件還支持Altera的多電壓I/O 接口特性,允許和其他器件保持1.5V、1.8V、2.5V或3.3V邏輯級的無縫連接(見圖4)。EPM240和EPM570器件含兩個I/O區,EPM1270和EPM2210含4個I/O區,每個I/O區可以采用獨立的VCCIO供電。

圖4. 多電壓I/O能力

評論