VHDL編碼中面積優化探討

VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起來的。這種用語言描述硬件電路的方式,容易修改和保存,且具有很強的行為描述能力,所以在電路設計中得到了廣泛應用。利用VHDL語言對PLD開發,面積(Area)是一個很重要的指標。通過“面積”優化可以使用規模更小的可編程邏輯芯片,從而降低系統成本;改善電路性能,降低器件功耗;為以后的技術升級留下更多的可編程資源,方便添加產品的功能。

VHDL包含的語句非常豐富,不同的描述可以實現同樣的邏輯功能。但應注意,實現同樣功能的不同描述,可能在綜合出的電路規模上存在差異,也就是說,對資源的利用率有所不同。本文就有關VHDL編碼方面的面積優化問題進行討論。

2 常見問題

2.1 避免引入不必要的寄存器元件

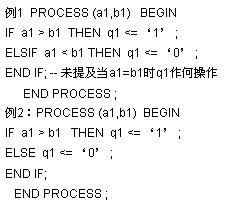

在描述組合邏輯電路時,應使用完整的條件語句結構。因為不完整條件語句的使用會引入不必要的寄存器元件,既浪費邏輯資源,又降低電路的工作速度,影響電路的可靠性[1]。例如用IF條件語句設計一個純組合電路的比較器,比較以下兩例:

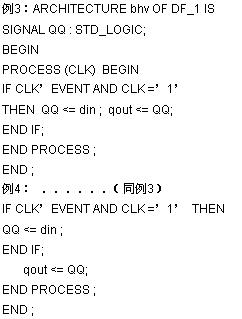

信號可以作為設計實體中并行語句模塊間的信息交流通道,是具有全局性特征的數值容器。在時序電路設計中,為了在設計更大的電路時使用由此引入的時序電路的信號,常在電路內部定義節點信號。通過信號完成進程之間的通信,從而保證結構體中多個進程能夠并行同步運行。寄存器描述中有節點信號時,不同的描述會產生不同的綜合結果。如以下兩例:

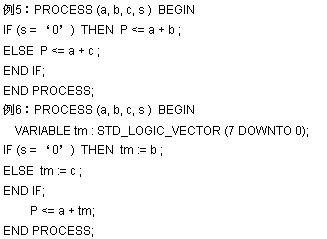

在設計數字系統時常常需要反復地調用一個同樣結構的模塊,這類模塊往往是算術模塊。如例5中兩個加法器是在s不同取值時分別使用的,且輸入a一直接入加法器。略作修改,如例6,可以只用一個加法器完成同樣功能,從而有效地減小使用面積。

CASE語句描述的程序可讀性較好,因為它把條件中所有可能出現的情況全部列出來了,可執行條件一目了然,且條件句的次序并不重要。故而是常用的條件語句之一。因為它的執行過程更接近于并行方式,一般地,綜合后,對于相同的邏輯功能CASE語句比IF語句(順序條件語句)的描述耗用更多的硬件資源[1]。

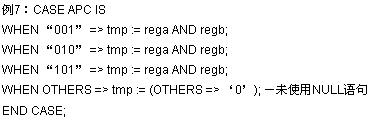

另外,Max+plusⅡ有時對NULL會出現擅自加入鎖存器的情況,在用CASE語句描述組合邏輯電路時,應盡量避免使用NULL來表示未用條件下的操作行為,改用確定操作,如例7。

因為變量值是立即獲得的,如果先寫后讀就會產生長的組合邏輯和鎖存器。因此,在編寫代碼時,對變量要先讀后寫,如例8。

就綜合而言,簡單的比較運算符(=和/=)在實現硬件結構時,比排序操作符(>、>=、、=)構成的電路芯片資源利用率要高。因此,如有可能,應盡量用比較運算府代替排序操作符。

2.7 盡量采用可計算型下標名

下標名用于指示數組型變量或信號的某一元素。如果下標名是一個可計算的值,則此操作數可很容易地進行綜合。否則,只能在特定的情況下綜合,且耗費資源較大。所以,在進行電路設計時盡量采用可計算型下標名,以提高資源利用率。

3 結束語

功能強大的EDA開發軟件和專業的綜合工具的不斷發展,使應用VHDL進行PLD設計變得更簡單、更快捷。但決不能忽視VHDL語言的使用。隨著所設計電路規模的增大,對有限的芯片資源的利用率問題就顯得尤其重要。在不影響速度要求前提下,應盡可能地進行面積優化。適當地進行編碼是優化設計的重要保障,對高質量、高效率地完成VHDL是十分有意的。

參考文獻:

[1] 潘松,黃繼業.EDA技術實用教程.北京:科學出版社,2002

[2] 趙剛 等.EDA技術簡明教程.成都:四川大學出版社,2004

[3] 林瑤,使用VHDL語言中幾個常見問題的探討,微計算機信息:2004年,20卷,9期,136~137頁

創新點:寄存器描述中有節點信號時,根據由節點信號向端口賦值語句在程序中的不同位置,綜合的結果存在差異:此語句在IF條件語句之內時寄存器占用的邏輯資源比它在IF條件語句之外時多一倍。

評論