基于Simulink的數字下變頻器設計及其FPGA實現

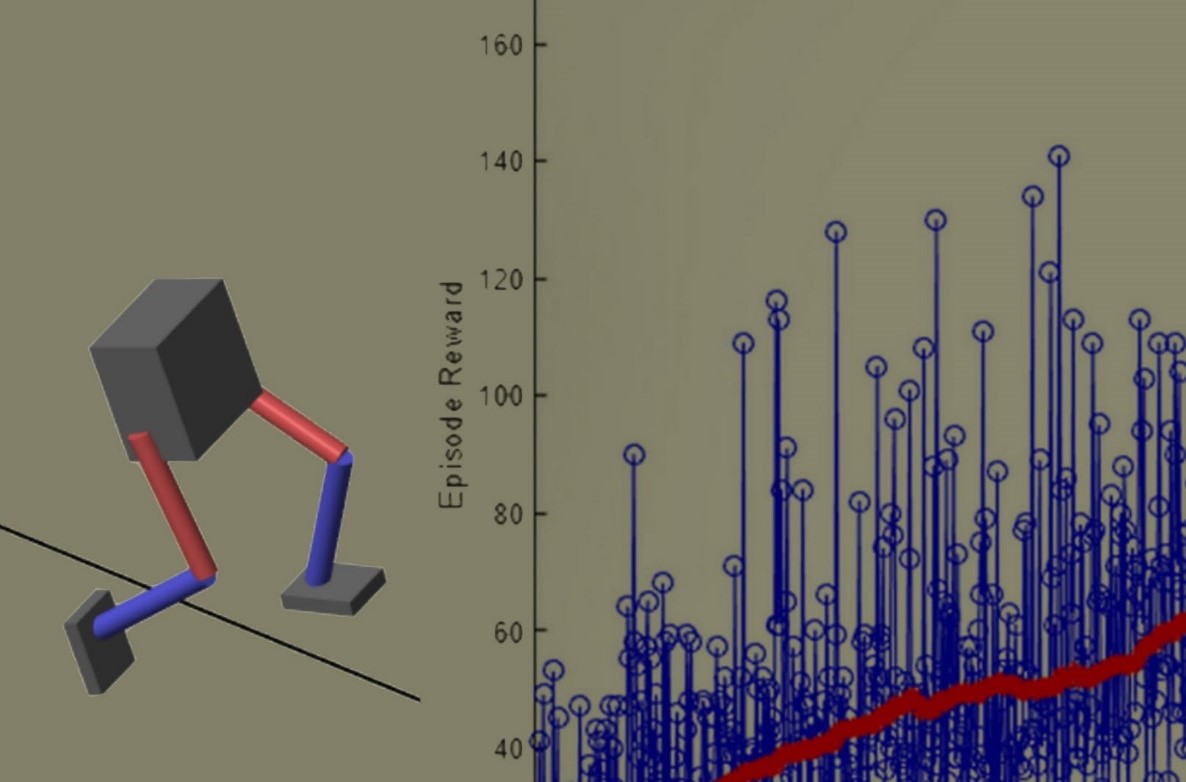

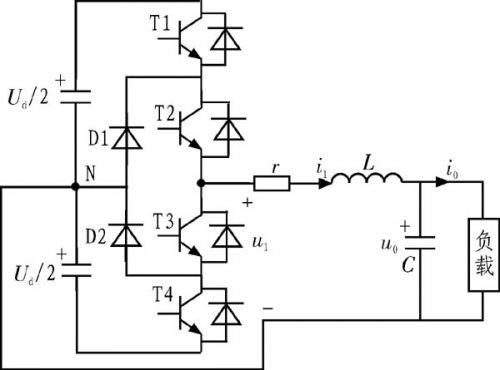

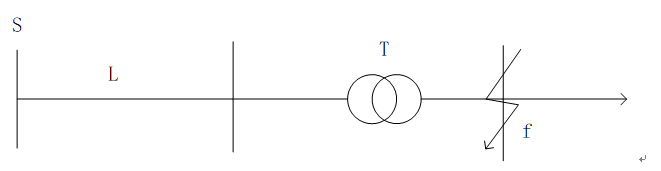

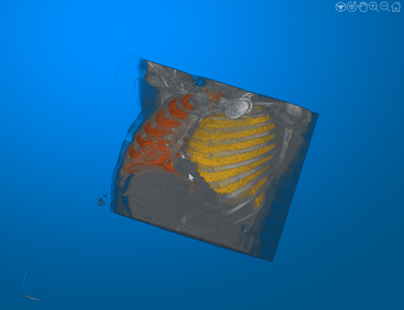

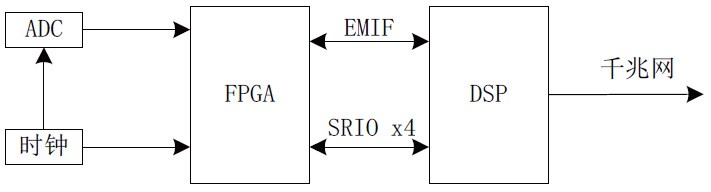

數字下變頻是數字接收機中一個重要組成部分,實現將高速ADC轉換后的數字信號進行抽取和濾波,得到低速的數字基帶信號。針對傳統(tǒng)模擬接收機系統(tǒng)帶寬較窄,系統(tǒng)體積大,同時缺少靈活性的缺點,本文利用MATLAB的Simulink工具箱結合Altera公司的DspBuilder軟件,仿真和設計了一體積較小(只需要一片FPGA)、可靈活配置的中頻數字寬帶接收機,并進行了FPGA的硬件實現。實驗結果表明:設計的數字中頻接收機具有系統(tǒng)帶寬較寬,體積較小,可以進行靈活的配置,能滿足不同的性能要求等優(yōu)點。

基于Simulink的數字下變頻器設計及其FPGA實現.pdf

評論