基于SoPC架構的四通道SSI通信控制器

在嵌入式系統應用領域中,需要完成的任務越來越復雜,應用環境也越來越惡劣,要求嵌入式計算機在體積不斷減小的情況下,具有更強的處理功能和較低的功耗。本文采用FPGA[1]設計技術,利用VHDL硬件描述語言[2],將4個同步串行接口協議SSI IP核[3]模塊組成一個功能可擴展的SoPC架構的從通信控制器,從而使主從控制器協同工作,保證了整個嵌入式系統在通信速度達到技術要求的前提下,能更有效地降低系統功耗與體積。

1 SoPC設計方法

可編程片上系統SoPC(System on Programmable Chip)(或稱基于大規模FPGA的單片系統)是一種靈活、高效的SoC解決方案,將處理器、存儲器、I/O口等系統需要的功能模塊集成到一個PLD器件上,構成了一個可編程片上系統,具有靈活的設計方式(可裁減、可擴充、可升級),并具備軟硬件在系統可編程功能。

圖1為典型的基于IP核庫的SoPC設計流程,主要是利用軟硬件協同方法完成整個系統設計。

2 通信控制器架構模塊組成

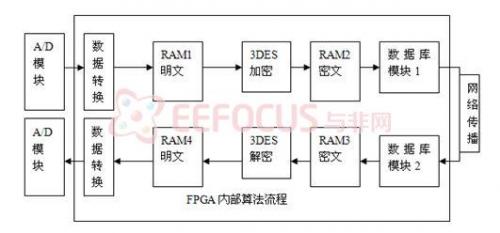

本文采用了一種全新的SoPC體系結構,整個嵌入式系統主要由主控制器和FPGA(從控制器)兩大功能單元組成,其結構如圖2所示。主控制器選用TI公司的TMS320C6713 DSP,虛框內的電路單元則為所設計的多通道同步通信控制器(也即從控制器)。通過TMS320C6713處理器芯片自帶的EMIF模塊與基于FPGA實現的多通道同步通信控制器進行數據交換。基于FPGA實現的從處理器內部選用MC8051 IP軟核來控制和管理4路SSI協議通信控制器,TMS320C6713與MC8051之間通過雙端口RAM共享數據和交換信息,整個系統采用中斷控制方式,實現主/從控制器協同處理任務。

由圖2可知,該SoPC架構控制器內部可劃分為4大模塊:從處理器MC8051 IP核、4路SSI協議通信控制器、雙端口RAM和中斷邏輯單元。下面分別對4個主要組成模塊進行介紹。

2.1 從處理器

為了提高同步通信控制器的自主性與靈活性,在FPGA內部嵌入一個微控制器80C51 IP核作為同步通信控制器的核心控制單元。MC8051 IP軟核的特點主要有:指令集與工業標準的8051控制器兼容;新的體系結構使單片機處理速度提高了10倍;無多路復用I/O端口,實行輸入和輸出接口完全隔離;256 B的內部RAM;最高可達64 KB的內部ROM和最高可達64 KB的外部RAM;容易調整或改變VHDL源代碼實現相關的核擴展功能;可通過VHDL常量進行參數化設置。

圖3是MC8051 IP核的內部功能結構圖。從圖中可以看到,該IP核包括的子模塊有:算術邏輯單元MC8051_ALU、串行接口單元MC8051_SIU、定時器/計數器單元MC8051_TMRCTR、核心控制單元MC8051_CONTROL、內部數據存儲單元MC8051_RAM、內部程序存儲單元MC8051_ROM和外部數據存儲單元MC8051_RAMX。其中,N表示MC8051_SIU和MC8051_TMRCTR兩個單元根據實際需要可靈活制定的個數,其范圍值為1~256,可在VHDL代碼中改變參數C_IMPL_N_TMR的值進行設置。

2.2 SSI協議控制器

同步串行接口SSI(Synchronous Serial Interface)[4]通信協議是同步串行通信協議的一種類型,該協議主要包含幀同步信號GATE、時鐘信號CLK和串行數據DATA三類信號,其時序關系如圖4所示。

在圖4中,幀同步信號GATE有方式1和方式2兩種可選擇方式協調控制時鐘信號CLK和串行數據DATA。方式1用虛曲線①表示,在該方式下,整個系統空閑時,GATE一直處于高電平狀態,當觸發一個瞬態低電平脈沖后,DATA在GATE信號的上升沿根據系統配置要求進行傳輸,同時GATE保持高電平。方式2用實曲線②表示,該方式下當系統空閑時,GATE一直處于低電平狀態,當觸發一個瞬態高電平脈沖后,DATA在GATE信號的下降沿進行傳輸,同時GATE保持低電平。在上述兩種方式中,DATA可在CLK的上升沿或者下降沿保持穩定并進行采集。

SSI IP核接口信號圖如圖5所示。

本文中共定義了4路(A~D)相同結構的SSI IP核,MC8051通過中斷和查詢方式對4路通信協議控制器進行數據的收/發操作控制。

2.3 雙端口RAM

MC8051中的外部數據存儲器MC8051_XRAM存儲空間最高可達到64 KB,本設計用VHDL語言生成一個32 KB的外部數據擴展雙端口存儲器MC8051_XRAM,一端供MC8051 IP核操作,另一端供DSP操作,通過地址線譯碼,從而為MC8051_XRAM和4路SSI協議控制器提供cs_x和cs_a~cs_d等片選信號。輸入MC8051_XRAM模塊的地址線為addra(15:0),實際使用到的地址線空間為addra(14:0),支持32 KB尋址空間。

2.4 中斷邏輯單元

中斷邏輯單元的操作地址為FFD3H,當DSP向該地址進行寫操作時,中斷邏輯單元將向多通道同步通信控制器發出低有效的中斷信號;當多通道同步通信控制器中的MC8051向該地址進行寫操作時,中斷邏輯單元將清除中斷。該中斷邏輯單元的信號接口信息如表1所示。

選中A路通道對并行數據的發送進行仿真測試,其測試仿真如圖7所示。從圖可以看出,并行數據Data在MC8051工作時鐘Wr_clk和外部分頻時鐘Exclk作用下,通過設置A通道內的寄存器組合達到最終串行數據的發送。從而可以驗證,數據發送仿真功能正確。

選中B路通道對外圍串行數據的接收進行仿真測試,其測試仿真如圖8所示。從圖可以看出,串行數據Rxd在MC8051工作時鐘Clk和外部分頻時鐘Exclk作用下,通過配置B通道內的寄存器組合得到并行數據的接收。從而可以驗證,數據接收仿真功能正確。

本文以Xilinx公司的FPGA器件為設計平臺,采用VHDL硬件描述語言,設計了一種SoPC架構的從通信控制器,并對設計方案進行了仿真與驗證,得出了設計方案的正確性,并已成功用于某遙測數據工程實踐中,因其兼具較高的數據傳輸率、IP核的可移植性和靈活擴展性而容易推廣使用。

評論