FPGA系統設計的仿真驗證之: 功能仿真和時序仿真的區別和實現方法

7.4功能仿真和時序仿真的區別和實現方法

這里我們使用一個波形發生器作為例子,來說明如何使用Modelsim對QuartusII生成的IPCore和相應的HDL文件進行功能仿真和時序仿真。這個例子里面使用到了由QuartusII生成的一個片上ROM存儲單元。這種存儲單元和RAM一樣,都是基本的FPGA片上存儲單元,在以后的設計里面會經常使用到。

7.4.1功能仿真

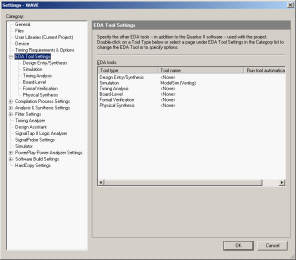

(1)在QuartusII中設置第三方仿真工具,選擇“Assignments-Settings-EDAToolSettings-Simulation”,選擇“ModelSim-Verilog”。如圖7.17所示。

圖7.17EDA工具設置

(2)編譯工程。編譯帶有IPCore的工程文件。

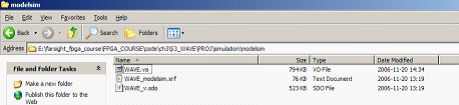

(3)編譯完成后會在工程目錄下生成“simulation-modelsim”的目錄,如圖7.18所示。其中包含了3個文件:“.vo”是仿真網表文件,可以用來代替設計文件;“.xrf”是Quartus編譯生成的信息文件;“.sdo”是工程延時信息。

圖7.18編譯生成文件

(4)加入仿真庫文件。

仿真庫的路徑為“C:alteraquartus50edasim_lib”,包含了如下3個仿真庫文件。

·220model.v:帶有用戶原語類型的Quartus自帶的IP核的庫文件。

·altera_mf.v:Quartus自帶的IP核的庫文件。

·cyclone_atoms.v:相應系列的器件庫。

在本例中需要添加altera_mf.v,cyclone_atoms.v兩個庫文件。

(5)編寫測試文件(詳見7.5節)。

(6)將測試文件粘貼到剛才生成的目錄中,如圖7.19所示。

圖7.19添加測試文件

(7)打開modelsim。

(8)創建工程并添加源文件,如圖7.20所示。

圖7.20為工程添加源文件

(9)編譯工程。結合庫文件一起進行編譯、如圖7.21和7.22所示。

圖7.21全部編譯前

圖7.22全部編譯后

(10)修改wave.vo文件。將文件中的延時信息注釋掉,即:

//initial$sdf_annotate(WAVE_v.sdo);

(11)重新編譯wave.vo文件。

(12)打開開始仿真對話框,如圖7.23所示對話框。

選擇頂層模塊wave_top,開始進行仿真,如圖7.24所示。

圖7.23選擇開始仿真的文件 圖7.24選擇頂層模塊文件

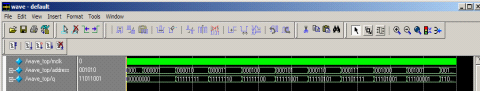

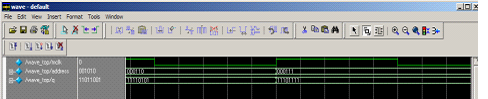

(13)添加信號。右鍵選擇添加信號到波形圖。并在命令行中敲入“run1ms”,按“回車”鍵,開始仿真。結果波形如圖7.25和圖7.26所示,分別是二進制顯示、十進制顯示。

圖7.25二進制顯示

圖7.26十進制顯示

放大查看細節的波形時序,可以發現,功能仿真的結果是沒有延遲的,如圖7.27所示。

圖7.27功能仿真結果無延遲

7.4.2時序仿真

(1)將功能仿真第(10)步中對wave.vo文件做的注釋改回來,重新進行編譯。

(2)重新打開開始仿真對話框,選擇頂層模塊,如圖7.28所示。

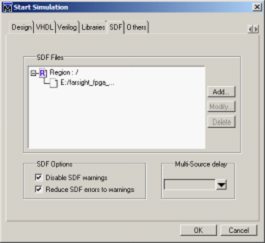

(3)選擇“SDF”選項卡,如圖7.29所示。

圖7.28選擇頂層模塊仿真 圖7.29“SDF”選項卡

(4)加入“.sdo”文件,將兩個SDFOptions都選中,如圖7.30所示。

圖7.30添加“.sdo”文件

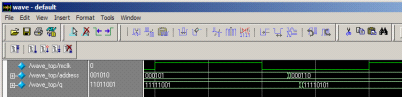

(5)和功能仿真一樣,為波形窗口添加信號,開始進行仿真。

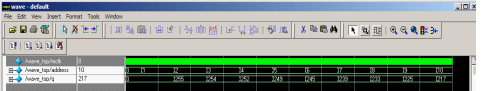

(6)通過波形圖,查看時序仿真的延時,如圖7.31所示。

圖7.31查看時序仿真延遲

評論