利用FPGA實現外設通信接口之: 典型實例-字符LCD接口的設計與實現

10.8典型實例18:字符LCD接口的設計與實現

10.8.1實例的內容及目標

1.實例的主要內容

本節旨在設計實現FPGA與字符LCD的接口,幫助讀者進一步了解字符液晶的工作原理和設計方法。

2.實例目標

通過本實例,讀者應達到以下目標。

·學習字符型液晶顯示器的控制原理。

·掌握利用FPGA設計驅動的基本思想和方法。

·熟練掌握狀態機的使用。

10.8.2字符LCD接口實例內容

紅色颶風開發板配套的字符液晶模塊為2行,每行16個字符。本實要求顯示功能如下:第一行顯示“WelcomeRedLogicWorld!”,第二行顯示“RedLogicWorld!”,由于一行只能顯示16個字符,因此要整屏左移顯示。

10.8.3FPGA代碼設計實現

本設計的程序主要包含兩個模塊,一個模塊為char_ram,另一個模塊為LCD的驅動模塊lcd。

char_ram模塊的主要功能是根據輸入的地址,輸出相應字符在CGRM(字符存儲發生器)中的地址。因為在控制LCD顯示時,只需用戶提供相應字符的地址,就可以顯示出該字符。

在char_ram中,先設置好所有字符對應的地址,然后給需要用到的字符定義新的地址用于選擇輸出。

Lcd模塊用于驅動lCD正常工作。LCD是一個慢顯示器件,因此時鐘一定要滿足要求,在這里通過50MHz分頻得到輸入的時鐘周期約為100µs(約10Hz),以滿足慢顯要求。LCD的驅動模塊利用一個狀態機來實現。具體程序參考實例源代碼。

10.8.4ModelSim仿真驗證

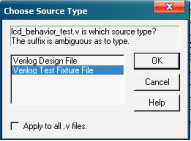

通過AddSource的方法直接將測試代碼加入到工程當中。選中要加入的測試代碼文件:led_behavor_test.v,彈出如圖10.37所示的對話框,選擇“VerilogTextFixtureFile”。

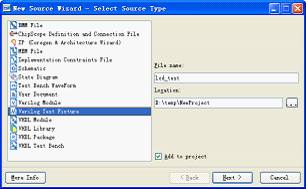

用戶也可以直接新建一個仿真文件,選擇“NewSource”,選擇“VerilogTestFixture”,輸入測試文件名稱,如圖10.38所示,單擊“Next”按鈕。

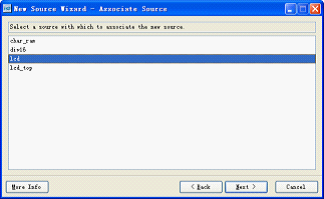

選擇lcd模塊(對哪個模塊進行測試,就選擇哪個文件),如圖10.39所示。

圖10.37選擇源文件類型

圖10.38新建仿真源文件

圖10.39選擇被測試模塊

新建測試文件后,ISE會自動生成一部分代碼,其余內容可直接從源工程中提供的測試文件中復制。

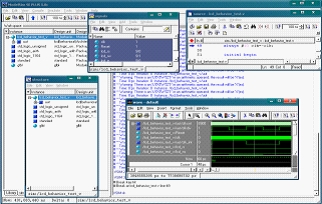

添加后選中測試文件可以看到如圖10.40所示的信息。

圖10.40仿真文件信息

在Processforsource下有4個M的圖標,分別對應4個級別的仿真。從上至下,第一個為行為仿真,第二個為翻譯后仿真,第三個為映射后仿真,第四個為布局布線后仿真。在這里先做行為仿真,只需雙擊第一個圖標,就可啟動ModelSim仿真,結果如圖10.41所示。

圖10.41行為仿真

默認情況下,ModelSim會彈出4個窗口,在這里主要觀察Wave窗口,如圖10.42所示。

圖10.42行為仿真波形窗口

上面列出的很多信號是人為添加的,具體如何添加以及具體Wave窗口下的許多用法在這里不做詳細敘述。需要特殊說明的是,如果用戶自己裝的是ModelSimXE版本,是無法完成這個仿真的,因為這個工程代碼是用VHDL寫的,測試代碼是用Verilog寫的,ModelSimXE版本是不支持混仿真的,建議安裝ModelSimSE版本,SE下是支持混合仿真的。

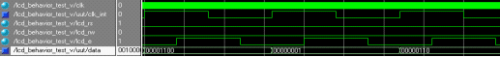

ModelSim仿真結果如圖10.43和圖10.44所示。

圖10.43LCD寫數據仿真結果

圖10.44LCD寫指令仿真結果

這兩個波形分別為寫數據和寫指令的仿真結果。寫數據即向DDRAM寫入要顯示的字符對應的地址,其中clk為系統的輸入時鐘50MHz,clk_int為分頻后得到的約10Hz輸入時鐘,lcd_e為使能信號,寫數據時RS=1,R/W=0,寫指令時RS=0,R/W=0。

10.8.5小結

本節對利用FPGA來驅動字符型液晶模塊的方法做了介紹,并通過編譯下載在紅色颶風的開發板上實現了預定功能。

評論