FPGA并行計算抽象接口的設計與實現

1 設計摘要

FPGA芯片具有可編程、可重配置、可并行計算的特點。隨著摩爾定律的發展,計算科學已經步入并行化的時代,具有并行處理能力的CPU/GPU隨即面世。而FPGA芯片憑借其并行計算的能力,已經可以輕松將科學計算、邏輯運算、ASIC設計等應用并行化,為了能將該特性普及化,本設計為基于C語言開發的程序開發了一個FPGA的并行計算接口,凡是以C語言設計的程序,均可通過調用本設計的接口,把復雜的算法、數值處理交給FPGA芯片完成,在不需要程序員學習FPGA知識以及使用FPGA開發工具的前提下,大大地減輕CPU的負荷以及從根本上提高了程序的執行效率,是FPGA并行化應用的一次全新嘗試。

2 系統原理與技術特點

系統以基于PC機的Windows操作系統為基礎,將FPGA芯片作為一個PCI Express總線設備,通過PCI Express總線與PC機的CPU通信,在Windows下開發該PCI Express設備的C程序驅動,提供函數接口供C程序調用。Windows下的C程序通過該驅動接口向PCI Express總線發送信號,接入PCI Express總線的FPGA芯片收到該信號后,根據信號的內容調用相應的片內模塊進行相應的計算,依靠其并行化的特點,可以將大多數的算法與數值處理并行化,最后再將計算結果通過PCI Express總線返回給運行于PC機的C程序,從而實現C程序的并行化,此過程相當于使用外圍的PCI Express設備為PC機的程序提供并行化的硬件加速服務。

傳統的CPU都屬于ASIC器件,存在設計過程復雜,靈活性不高,不可重配置的不足,而作為可重構計算的體系結構代表,FPGA在可重配置和并行運算方面具有獨特的優勢。

系統的技術特點有以下幾點:

(1)并行化加速的實現無需使用新的編程語言和編譯器;

(2)利用FPGA的可編程特性以及豐富的IP核資源,可實現多種類型計算的并行化,因此該硬件加速設備可適用于多個場合;

(3)可具有跨操作系統特性。只需開發相應操作系統(如Linux)下的PCI Express設備的驅動,便可在其他操作系統下使用FPGA的加速功能。

(4) PCI Express總線采用串行的全雙工傳輸,提供高速的數據傳輸率。PCI Express規格從1條通道連接到32條通道連接,有非常強的伸縮性,以滿足不同系統設備對數據傳輸帶寬不同的需求。例如,PCI Express X1規格支持雙向數據傳輸,每向數據傳輸帶寬250MB/s,PCI Express X1已經可以滿足主流聲效芯片、網卡芯片和存儲設備對數據傳輸帶寬的需求,而速度更快的PCI Express X16,即16條點對點數據傳輸通道連接來取代傳統的AGP總線,適合于需要大量復雜數學計算的應用。PCI Express X16也支持雙向數據傳輸,每向數據傳輸帶寬高達4GB/s,雙向數據傳輸帶寬有8GB/s之多,因此,選擇PCI Express作為傳輸總線,不會存在系統瓶頸問題。

(5)PCI總線的資源占用情況

(6)用戶在編寫程序時,只需要include本文所提供的.h文件,便可調用.h頭文件中提供的并行計算函數接口,同時將源代碼與本文提供的對應C源文件文件共同編譯,即可通過調用PCI總線接口驅動來完成所需的計算。

3 系統軟件流程

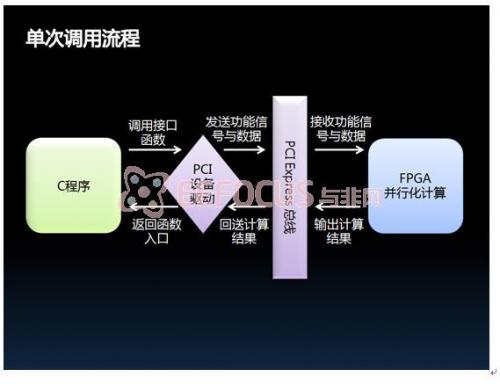

圖 1 單次調用接口的軟件流程

上圖所示為C程序一次調用并行計算接口的過程,C程序與FPGA芯片的通信通過PCI Express總線來完成。FPGA芯片根據接收到的信號來判斷應該采用哪個獨立模塊來進行請求的計算。

圖 2 多進程C程序調用并行接口的流程

上圖所示為多進程程序在調用該并行接口時的過程。關鍵在于在向FPGA芯片發送請求信息時附帶發出該請求的進程ID號,這樣在接收總線發回的數據時才能根據進程號對號接收。

4 系統框架

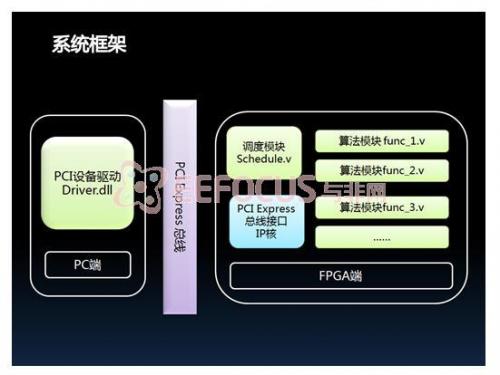

圖 3 系統框架

上圖所示為系統的組成結構。PC端主要有Windows下的PCI設備驅動(采用WinAPI編寫)、PCI Express物理總線;FPGA端主要有PCI Express總線IP核、調度模塊以及具體各種算法的Verilog HDL模塊。

5 系統功能

5.1 PCI設備驅動程序功能

(1)讀寫FPGA芯片數據

(2)緩存請求與結果數據

(3)調度多進程請求與分配多個進程的計算結果

(4)異常處理

5.2 FPGA調度模塊功能

(1)相應PCI總線請求,判斷需要調用哪一個算法模塊。

(2)根據請求類型調度相應的計算模塊,并將請求的數據提供給該模塊

(3)接收計算模塊回應的計算結果,再通過PCI Express總線接口的IP核將數據回送給PC

5.3 FPGA PCI Express總線接口IP核功能

(1)通過PCI Express總線讀寫數據

評論