一種使用USB對ADSP_TS101S進行鏈路口加載的方案

ADSP_TS101S(以下簡稱TS101)是美國ADI公司推出的TigerSHARC系列數字信號處理器中一款高性能的靜態超標量處理器,它專為大規模信號處理任務和通信應用進行了結構上的優化,廣泛應用于雷達等高速實時信號處理系統。

將程序代碼加載到DSP內部程序空間時,通常采用開發器的JTAG接口將執行文件加載到DSP內存里進行調試;在硬件仿真完成后,又通過JTAG接口將生成的ldr文件燒寫到與TS101相連的FLASH里固化。然而在很多情況下,使用開發器加載或固化程序很不方便,甚至無法實現,因此需要開發一種脫離開發器的TS101加載方式。基于這種需求,設計實現了基于USB總線的TS101鏈路口加載,只需一根USB線纜,即可實現TS1 01的程序在線重加載和固化。

1 Link Port協議

鏈路口(Link Port)是TS101的一種高速互聯接口,它的通信是通過一個8位的數據總線和3個控制信號進行的,有4組LINK管腳。其中LxC LKIN和LxCLOUT是時鐘/應答輸入和輸出管腳;LxDAT[7:0]-數據輸入輸出總線;LxDIR是LINK的方向指示信號。Link Port的最簡單的連接方式(如圖1所示)用了LxCLKIN,LxCLKOUT,和LxDAT。每個ADSP-TS101 DSP的LxCLKOUT與其它的LxCLKIN相連,兩片TigerSHARC101 DSP芯片之間用LxDAT數據總線相連。

Link Port的最小傳輸單位是8個時鐘周期,數據總量為4倍字長(16字節,在時鐘的雙沿觸發)。傳輸被發送端初始化,只有當接收端設置LxCLKOUT(對于發送端為LxCLKIN)為高電平,發送才能被初始化為一次傳輸。LxCLKOUT為高電平意味著接收端為接收模式并且接收緩沖器為空。

2 TS101的軟件設計流程及加載引導方式

TS101的軟件設計流程如圖2所示。其中,鏈接描述文件(.LDF)定義了整個系統的存儲器配置和程序中數據及代碼的具體存放位置。加載核文件(.DXE)是指加載引導核程序,其大小為32 bit,放在加載文件的起始部分,其功能是用來實現TS101的正確引導。ADI公司在其DSP集成開發環境Visual DSP++安裝目錄的ldr子目錄下提供了標準加載核文件及相應的源程序(.ASM)和鏈接描述文件。一般可直接使用提供的標準加載核文件或對其相應的源程序進行簡單修改,重新編譯鏈接生成所需的加載核文件。加載文件是由引導加載器(elfloader)將可執行文件進行一定的格式變化,并在起始位置附加上加載核文件生成的。

加載程序的外部設備可以直接向鏈路口緩沖寫入數據,只要寫入速率不超過DSP的主時鐘頻率即可。此處的外部設備采用計算機的USB總線。鑒于FPGA在數字電路系統設計中具有可靠性高、設計靈活、易于開發等優點,本文采用FPGA進行Link Port與USB的接口設計,使USB的輸出滿足Link Port的協議,以實現DSP的鏈路口加載。

3 USB總線及其與Link Port的接口

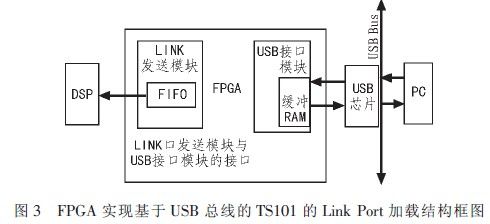

采用FPGA實現基于USB總線的TS101的Link Port加載結構框圖如圖3所示。

3.1 Link Port發送模塊

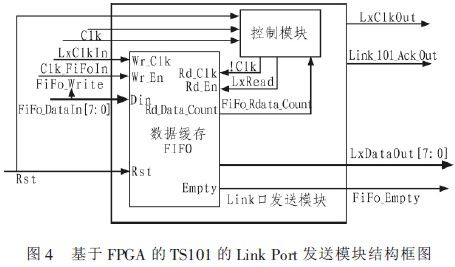

ADI公司網站上有推薦的實現TS101的Link Port收發協議的VHDL代碼,但是比較復雜,鑒于本文只需要使用Link Port的發送功能,且無需緩沖,故根據圖1所示的最小Link Port配置編寫代碼,實現Link Port發送功能。基于FPGA的TS101的Link Port發送模塊結構框圖如圖4所示。

圖4 中的FIFO負責對輸出數據進行緩沖,當輸入數據的速率高于Link Port時鐘的頻率時,Link Port的數據可以先存在FIFO數據中,當存入一定數量以后,再以Link Port的時鐘把數據讀出。當輸入數據的速率低于Link Port的時鐘數率的時候,Link Port的數據同樣可以先存在FIFO中,當存入整數倍的4字數據量后,再以Link Port的時鐘的數率發送出去。

圖4中的控制模塊是Link Port發送模塊的關鍵模塊,主要負責產生讀FIFO的讀使能信號和Link Port的發送時鐘根據Link Port發送的時序特點,使用狀態機來實現數據流的控制。當Link Port沒有工作時,保持等待狀態。需要傳輸數據時,首先檢查LxCLKIN是否為高電平,若是,則說明接收端為接收模式并且接收緩沖器為空,可以初始化一次發送,否則要等待。開始傳輸數據時,數據首先被寫入FIFO中,當判斷到FIFO的輸出信號EMPTY為高時,將處于默認高電平的LxCLKOUT信號拉低,在經過6個時鐘周期的低電平后(在此期間檢測LxCLKIN是否一直為高電平),LxCLKOUT拉高形成第一個LINK時鐘上升沿,這個時候應該在數據線上產生FIFO內的第一個輸出數據。LxCLKOUT下一周期拉低,第2個數據輸出,這樣經過16個時鐘周期以后表示一次4字傳輸完畢。然后檢測FIFO中剩余的數據FIFO_RDATA_COUNT,若大于4則繼續上面的傳輸操作,否則,說明FIFO中只剩最后一個4字,這次傳輸LxCLKOUT的最后一個時鐘上升沿產生以后,不再變低,一直保持高電平。然后,把本模塊中的所有臨時寄存器和FIFO復位。在產生完足夠長度脈沖長度的清零信號后狀態機重新進入等待狀態。

3.2 USB接口模塊

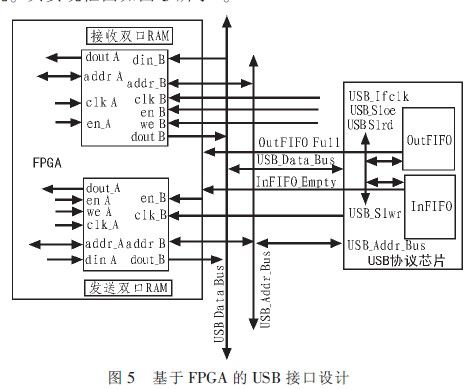

USB接口模塊采用FPGA控制USB協議解析芯片來實現。其實現框圖如圖5所示。

本方案中,USB2.0協議解析芯片選用CYPRESS公司的CY7C68013A,它將一個USB外設所需的所有功能集成在一塊芯片上。芯片提供了3種傳輸數據的方式,文中選擇從FIFO(SlaveFIFO)模式。在SlaveFIFO模式下,8051微控制器不在數據的傳輸通路上,只負責設備的初始化和相應主機的控制傳輸請求,高速大批量的數據傳輸通過外部的主控者通過SlaveFIFO接口直接將數據填充到FX2LP的端點中(或者從里面讀出),然后由硬件控制將數據傳輸給主機。

Slave FIFO的讀寫方式有兩種:同步讀寫以IFCLK為時鐘,IFCLK可以外部輸入,也可以使用內部的30 MHz或者48 MHz時鐘;異步讀寫時IFCLK信號無效,只需要提供讀寫信號即可進行數據讀寫。本文選擇同步讀寫。

FPGA采用Xilinx公司的XC3S1000。FPGA在其內部建立2個雙口RAM,來緩存收發數據;并與協議解析芯片的各控制信號相連,實現對其的讀寫控制。文中僅使用這個芯片的接收邏輯實現加載文件的USB總線傳輸,發送邏輯只用來做輔助調試和狀態監測。

3.3 LINK口發送模塊與USB接口模塊之間的接口

USB接口除用于加載TS101外,還可用于TS101正常工作時與PC機的數據傳輸,故對于不同意義的下行信息,需要根據其功能做不同處理。

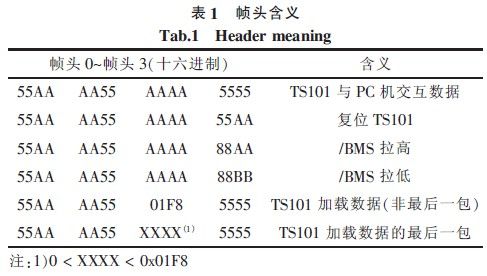

上位機向FX2LP發送數據時,是通過將需要發送的數據打包(每包的大小由固件程序決定),每隔固定一段時間向下發送一包實現的。在這里,每包數據包含512個字節,其中前8個字節用來當幀頭,后504個為需要下傳的數據。可通過幀頭的不同來區分下行信息的不同意義。其具體含義如表1所示。

FPGA輪詢每包數據的幀頭,如果是TS101與PC機交互數據,則送到雙口RAM中;如果是TS101加載數據,則送到LINK口發送模塊中;如果是/BMS拉高(低)指令,則通過相應的管腳拉高(低)/BMS;如果是復位TS101指令,則通知復位邏輯對TS101進行復位,同時復位數據緩沖FIF O。

在實現基于USB總線的TS101的LINK加載時,上位機將DSP加載文件(.ldr文件)打包后,通過USB線纜向FX2LP發送。.ldr文件的大小不一定為504字節的整倍數,因此最后一包數最后可能有很多0。必須把這些0去掉,否則可能在加載TS101時導致其死機。為解決該問題,在幀頭定義中,用幀頭2來區分是否為最后一包數,如果不是最后一包數,上位機打包時,幀頭2賦為01F8(即504),如果是最后一包數,則把將有效數據長度賦給幀頭2。FPGA不斷將TS101加載數據送到LINK口發送模塊中,當發現是最后一包數據時,讀取有效數據的長度,并啟動一個計數器,當計到該長度時,讓FIFO讀使能失效,則只有ldr文件的有效數據被加載到TS101中。

4 TS101程序在線重加載和固化的實現

首先通過上位機發送/BMS拉高指令,讓FPGA將TS101的/BMS管腳拉高,然后發送復位TS101指令,復位TS101和FIFO;之后,發送/BMS拉低指令,讓FPGA將TS101的/BMS管腳拉低,最后,將ldr文件打包為TS101加載數據包并向下發送。發送完畢后,TS101即可運行該程序。

若要實現TS101程序的固化,則可將要燒寫的程序生成為ASCII格式的ldr文件,轉化為.dat格式,通過include指令編譯到EPROM(FLASH)的燒寫程序中,生成為Link加載ldr文件,通過USB總線進行加載。燒寫完成后,可通過閃燈或通過USB總線上傳狀態信息來指示燒寫結果。

5 結束語

文中提出的基于USB的TS101鏈路口加載方法成功應用于某雷達信號處理平臺的程序加載,其功能驗證是通過使用本方法加載各種DSP應用程序并進行功能測試來完成的。使用該方案能穩定可靠的實現TS101程序的重加載,并且能對與之相連的FLASH芯片AT29LV040A進行成功燒寫。

評論