鋰離子電池管理芯片的研究及其低功耗設計 — 鋰離子電池管理芯片的電路實現 (三)

4.3關鍵模擬電路設計

本文引用地址:http://www.j9360.com/article/201706/348222.htm4.3.1偏置電路及基準源 電路電池管理芯片中,偏置電路設計是整個系統設計的基礎和關鍵,具體可以分為電流偏置和電壓偏置電路,而且這兩者相互之間可以轉換。偏置電路的功能是用來 給其它的電路模塊提供穩定的電壓或電流,也被稱為基準電流或基準電壓,所以其穩定性對整個電路的性能有較大影響。

1設計考慮

電池管理芯片對偏置電路的指標要求有一定的特殊性。總的說來,無論是電壓基準還是電流基準都要求其輸出特性穩定,包括低的電源電壓相關性(即高

PSRR)、低溫度系數,良好的負載特性,低的電流消耗(最好在1uA以內)及工藝無關性。其中,輸出對電源電壓的相關性是可以用輸出敏感度來表征

式中,Y表示輸出的電壓或電流。而溫度系數反映了輸出值隨溫度的變化量,通常定義如下:

對于高性能偏置電路來講,理想偏置電路所提供的電壓或電流與電源電壓、溫度和工藝等因素是無關的。但在實際的電路中,這些不可能同時實現。只能通過電路結構原理上的改進及優化設計,版圖布圖、工藝的改進等方面更進一步提高偏置電路輸出電壓或電流的穩定性。

應 該指出,在偏置電路的所有設計指標中,輸出與電源電壓相關性或者PSRR是一個關鍵的設計指標。如果PSRR特性退化,必然造成抗噪聲能力減弱。尤其對數 模混合系統,數字部分的大量噪聲干擾,通過襯底和電源耦合等各種途徑,影響到模擬信號的品質。PSRR是抗電源噪聲耦合的重要指標,良好的PSRR特性可 以保證,在規定的范圍內,無論電源如何改變,電路輸出的變化可控制在規定范圍內,即近似認為不變。下面將從偏置電路的輸出特性入手,分析具有較高電源電壓 抑制比的低功耗偏置電路的原理、設計及實現。

2基于UT的亞閾值自偏置電路

在一般的電流偏置結構中,輸入電流I IN由電源電壓和電阻決定,即I IN對電源電壓的靈敏度很高。為了使產生的偏置電流I OUT對電源電壓具有較低的靈敏度,可以利用一些與電源電壓相關度不高的電壓來產生偏置電流。常用的電壓有VBE、VTH、VGS、UT、齊納二極管的反向擊穿電壓等,這些電壓隨電源的變化較小,利用這些電壓可以極大改善輸出電流對電源電壓的靈敏度。如果對基于VBE和VTH的電流源加以改進,形成自偏置結構,可進一步減小輸出電流對電源電壓的靈敏度。

自偏置結構的基本思想是使IIN不再基于電源電壓和電阻,而是基于跟蹤電流源本身的輸出電流IOUT。其原理框圖如圖4.3.1所示:

圖4.3.1中,兩個變量IIN和IOUT的關系由電流源和電流鏡共同決定。從電流源的角度來看,輸出電流和輸入電流間的函數關系將隨不同的電流源而變化;從電流鏡的角度來看,如果電流鏡為單位增益,則輸入電流與輸出電流保持相等。

即輸出電流和輸入電流互為變化的基準。整個電路的工作點位于電流源和電流鏡輸出特性的交叉點。

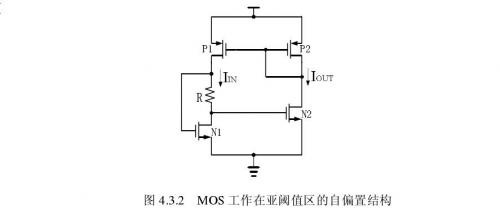

相 對而言,基于熱電壓U T的自偏置結構的溫度系數較小。U T的產生有兩種方法:一是可以利用兩個PN結的差值來獲得,二是可以利用MOS管工作在亞閾值區時具有類似PN結的I-V特性來產生。第二種方案中,由于 MOS管工作在亞閾值區,可使得電路的功耗變得很小,在低功耗設計中很有競爭力。圖4.3.2給出了MOS工作在亞閾值區的自偏置結構:

圖中,N1、N2和R組成Peaking電流鏡,其優點是可以方便地得到電流為幾μA甚至是nA級的電流;P1和P2則組成基本電流鏡。

在該電路中,假設I IN很小,則R上的壓降也較小,N1工作在飽和區。根據KVL知:

其中, 實際上,如果輸入電流IIN很小,則VOVN1﹤2nUT時,根據使用的工藝模型求得k≈100μA/V2,若取W/L=10,則只要電流小于5μA,N1就工作在亞閾值區。

實際上,如果輸入電流IIN很小,則VOVN1﹤2nUT時,根據使用的工藝模型求得k≈100μA/V2,若取W/L=10,則只要電流小于5μA,N1就工作在亞閾值區。

根據式(4.3.4),VOVN2﹤VOVN1時,所以N1和N2均工作于亞閾值區,當滿足VDS﹤4UT,有ID=(W/L)LESexp[VGS/(nUT)]根據電路原理圖可求出輸出電流IOUT:有根據電路原理圖可求出輸出電流IOUT:

式中,S表示各管的W/L比, IES是一個與工藝有關的參數,可表示為IES =μCOXnUT2exp[(-VT0-nUT)/ nUT].假定由P1和P2組成電流增益為1的電流鏡,當電路穩定時,其工作電流可通過上式求得:

從上式可以看出輸出電流與VDD無關,但在實際電路中,由于存在溝道長度調制效應,IIN和IOUT隨VDD的增加而緩慢增加,且IOUT/IIN的比值也稍有變化。

再求輸出電流的溫度系數,將式(4.3.7)兩邊分別對T求導,有

從式(4.3.8)可以看出,由于UT具有正的溫度系數,約0.086mV/℃,電阻也具有正的溫度系數,所以能夠互相抵消一部分。和基于VBE和VTH的自偏置電路相比,基于UT的自偏置電路的溫度系數顯然較低。

3無電阻的亞閾值電流偏置電路

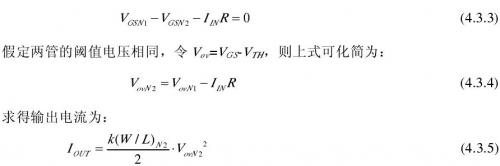

由式(4.3.7)可以計算出,要降低偏置電路的消耗,將M1和M2偏置nA級電流工作,則需要提高電阻R的值。根據MOS在線性區的工作特性,可以用MOS來代替電阻,基于這種想法可以實現無電阻的MOS亞閾值自偏置結構,電路圖見4.3.3.

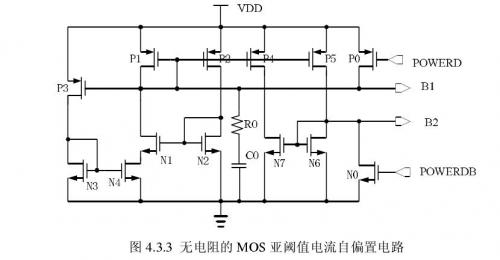

由圖4.3.3可知,如果支路電流較小,則N 1和N2工作在亞閾值區,N4工作在線性區,其中P1和P2構成比例電流鏡。圖中可以得到

若P1和P2為等比例電流鏡,則有SP1=SP2。上式可化簡為:

通常,取(SN1 /SN2)﹤19,所以VDSN4為100mA左右,只要保證VGSN4〉VTH+80mA,則N4即可工作在線性區,作為電阻來使用。為了保證電流精度,設計時應保證P1~P5及N3、N6、N7工作于飽和區,而工作區域的設定主要依靠W/L的調節來實現。

其中 式(4.3.14)可以看出,輸出電流與熱電壓 UT的平方成正比,而與電源電壓無關,從而可以達到恒流的目的。

式(4.3.14)可以看出,輸出電流與熱電壓 UT的平方成正比,而與電源電壓無關,從而可以達到恒流的目的。

4電流求和型的亞閾值電壓基準源

前面所提出的電壓或電流源能夠保證與電源電壓基本無關,但是,式(4.3.14)

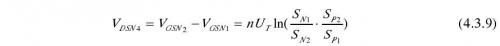

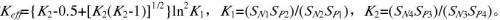

可 以看出,輸出的溫度穩定性不夠。因此,基準源的設計主要是在電路結構上采取補償技術以抵消溫度特性,即利用各具有正溫度系數和負溫系數的電壓量,配以適當 的權重系數,獲得零溫度系數的穩定輸出。典型結構的帶隙基準源可以歸為電壓求和型,輸出電壓V REF =V BE +KU T,其中,K是調節溫度系數的權重系數,輸出基本是固定值1.26V.其中,采用運放結構的帶隙基準源性能較優,但同時有大的失調電壓和較高的功耗;即使 不考慮運放對最低工作電壓的影響,其最低的電源電壓也僅在1.5V左右。由于在電池管理芯片中,電壓基準源是集成是系統內部的。在保證一定性能的前提下, 功耗、工作電壓乃至芯片的面積都是設計的重要指標,因此可以采用無運放的簡單補償電路結構。而采用電流求和模式[106-109]的帶隙基準源可以克服利 用電壓求和的低電壓場合工作局限性,其基本原理圖如圖4.3.4所示。

從圖4.3.4中可以得到:

可 見,這種基準源的模式是先得到電流值(括號內的兩項):一路和U T相關,并具有正溫度系數(Proportional To Absolute Temperature, PTAT)的電流,另一路是和V BE相關的,并具有負溫度系數(Inversely Proportional To Absolute Temperature,IPTAT)的電流,再通過從電阻上取壓降來獲得基準輸出電壓,所以這種模式通常被稱為電流模式基準源。式(4.3.15)可 知,當R=R 1時,和電壓求和模式完全等價;取不同的R值,就可以得到不同的電壓值,輸出較電壓求和模式的靈活;只要保證R和R1采用相同類型的電阻,即溫度系數也相同,就不會對輸出基準電壓的溫度系數產生影響。

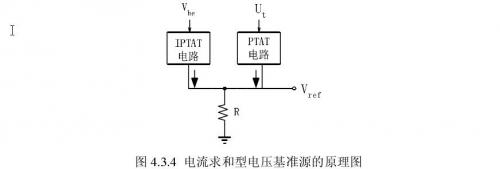

根 據分析可知,由于采用電流求和模式既可以利用帶隙基準源的原理產生高性能的輸出結果,又可以得到調節范圍較大的輸出電壓,比電壓求和模式有明顯的優勢。此 外,電流求和模式更有利于在較低的電源電壓下工作。電路設計的難點在于,如何產生I PTAT以及如何利用I IPTAT,同時各支路電流應盡可能減小以降低電路功耗。為了能利用P阱CMOS工藝實現,本文設計了一種電流求和型的電壓基準源,電路結構見圖 4.3.5 。

從圖中可以看出,電路可以分為三個主要部分:PTAT電流產生電路、IPTAT電流產生電路和電流求和電路。此外,為了使電路在加上電源電壓后能正常工作,還設計了啟動支路。

PTAT 電流產生電路采用了自偏置結構,其原因如下:根據前面的分析,基于U T的亞閾值自偏置電路,具有較高的電源電壓抑制比,同時,如果不考慮電阻的溫度系數,則輸出電流將和U T一樣,具有正溫度系數。電路由R1、P3、P4、N3和N4組成。通過選擇合適的R1值來使N3和N4工作在亞閾值區;為保證電流精度,P3和P4需工 作在飽和區。計算過程和前面類似,當SP3 =SP4時,則輸出電流

式(4.3.16)可以看出,不考慮電阻R1的溫度系數,電流IP4與熱電壓UT成線性關系,同樣具有正溫度系數。

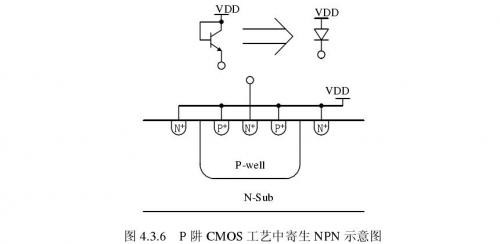

在P阱CMOS工藝中,如何利用產生IPTAT電流,最后實現相對于地而非電源電壓的基準電壓是一個設計難點。CMOS工藝中寄生NPN示意圖見圖4.3.6.圖中可知,和N阱工藝不同,P阱工藝中輸出的V BE是相對于V DD的壓降。

因此,圖4.3.5中的IPTAT電流由Q0、R0、P1、P2、N1和N2產生。其中N1、N2組成的電流鏡和由P1、P2組成的電流鏡疊加后,形成一個反饋回路,保證A點和B點電位相等。流過R0的電流則為

不考慮電阻R0的溫度系數,則此電流具有與VBE相關的負溫度系數,而與電源電壓無關。

圖4.3.5中的電流求和電路由N5、N2、P5、P4、P6、P7電流鏡以及求和電阻R2構成,所輸出的基準電壓V REF可表示為

從(4.3.18)式可以看出,通過調整電路中P4~P7、N2~N5的K值、R0以及R1值,理論上可以實現在R2上輸出具有零溫度系數的基準電壓VREF。適當調整R2值,可以使輸出基準可調;或者利用電阻分壓結構,可以輸出不同的基準電壓,因此電路輸出比較靈活。此外,電路中電阻值和器件參數均取比值,能最大程度地避免工藝漂移引起的輸出變化。

(4.3.18) 式還表明,要盡可能降低兩部分電流產生電路的功耗,使電路的電流有效地消耗在求和電阻上,這既可以降低電路總功耗,又可以在電路輸出一定基準電壓時減小求 和電阻值,節省芯片面積。在IPTAT電流產生電路中,可以通過提高R0阻值,同時降低流過Q0的電流來降低電流消耗;在PTAT電流產生電路,N3和 N4正確工作在亞閾值區則保證了極低的消耗電流。

圖4.3.5中的電流產生電路均有兩個平衡工作點,即零點和正常工作點。因此,都需要一個啟動電路,使電路能在上電的過程中脫離零點而穩定工作;從電路功耗考慮,啟動電路在電路進入正常工作后應斷開,沒有電流消耗。

以 PTAT電流產生電路為例,設計時從P4的漏極加入了RC電路,構成自偏置電路的啟動電路。上電的過程中,即當有一個階躍型電壓加到電路的瞬間,C1近似 為短路,R3和C1給P4提供了從電源到地的直流通路,經過3~5個RC時間常數后,C1中電流降為零,而此時P4也進入了穩定工作狀態,電路完成啟動。 同樣,IPTAT電流產生電路中加入了啟動電容C0以使電路在上電后能進入正常工作狀態

5取樣電路

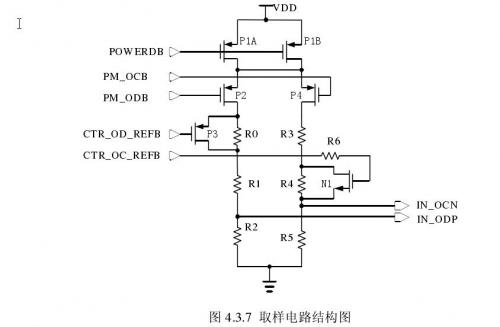

如果從輸出與電源電壓的相 關性角度,電阻分壓型偏置電路的相關度為100%,顯然不適合充當需要有穩定電流或電壓輸出的偏置電路。但是,這也從另一方面說明,電阻分壓電路輸出能很 好地跟隨電源電壓的變化,可以充當電池管理芯片中的另一個重要電路—取樣電路。這是由電阻I-V特性是典型的線性所決定的。圖4.3.7是系統所用的兩個 分壓電路,分別對過充電壓、過放電壓進行采樣。

圖中的控制信號均由數字模塊產生。POWERDB是電路進入Power Down模式的控制信號,PM_OCB和PM_ODB則是根據負載特性對取樣模式進行選擇的信號,而CTR_OD_REFB和CTR_OC_REFB通過 調節分壓電阻比,來實現過充和過放的遲滯釋放功能。

和有源電阻分壓電路相比,圖7.3.7所示的電路有線性好,分壓比可調,不受工作電壓大小限制的優點,更重要的是,利用電阻分壓,既可以盡可能地避免了工藝漂移引起的輸出信號變化,又可以配合較成熟的Trimming技術來有效控制輸出信號的精度。

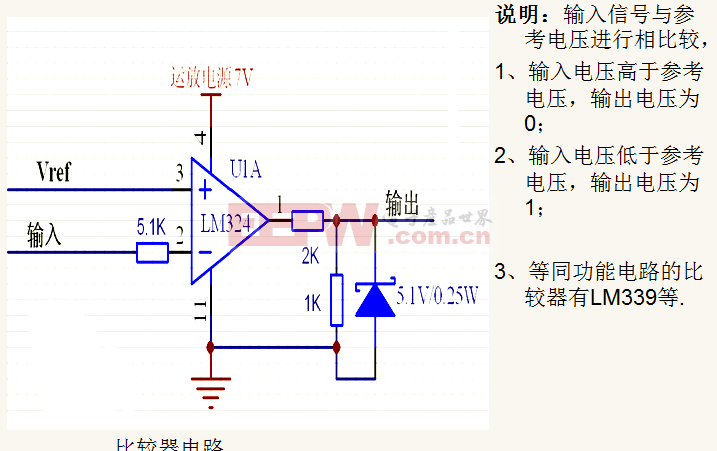

4.3.2比較器電路

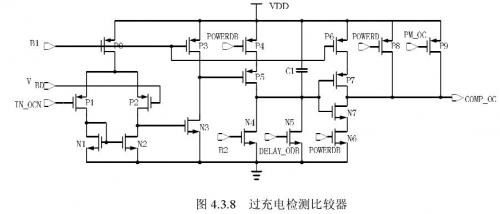

比 較器是電池管理芯片中較常見也較重要的模擬電路模塊之一。其中,過充比較器更是較為關鍵的模塊,不僅要求它具有較高的檢測精度和較強的抗干擾能力,同時還 要求它消耗電流較小,設計難度較大。以下對具有代表性的過充比較器電路進行分析設計。圖4.3.8為過充電檢測比較器的結構圖。

圖 4.3.8中,電路的比較功能主要由前兩級完成,功能實現并不困難,但需要著重從影響性能各個因素考慮設計該電路。輸入級中,差分對采用PMOS管,主要 基于電路噪聲和電源電壓抑制比的考慮。一方面,由于電路工作于低頻條件下,此時1/f噪聲是器件重要的噪聲源。PMOS管的1/f噪聲比NMOS小,為了 減小輸入噪聲,采用PMOS管作為差分輸入管,除瞬間干擾,過充電釋放檢測的延時可以短一些。這樣,過充電釋放的延時直接在過充電比較器中對電容充電實 現。另一方面,P差分對輸入的電源電壓抑制比高于N差分對輸入,這是因為輸出管N3不是將電源電壓的變化直接饋通至輸出端,而是利用電流源P3的隔離,使 輸出端受電源電壓的影響減小。

比較器消耗電流可以從兩個方面考慮,一是減小偏置電流,將P0、P3、N4和P6偏置在亞閾值區。二是在過 放電狀態下,用Power Down狀態信號POWERD、POWERDB將整個電路關斷,前三級用偏置電路關斷,P4用于關斷從V DD、P5和N5組成的通路,P8和P9保證比較器在Power Down狀態和功耗管理狀態下輸出正確的信號。

由失調和1/f噪聲分析可知,增大輸入級管的柵面積可以減小失調和1/f噪聲。

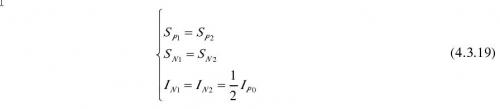

綜合考慮失調和噪聲性能,偏置電流取10nA時,P管和N管都能偏置在亞閾值區,再與偏置電路提供的信號相配合,可以確定P0的寬長比。在靜態情況下,要求比較器輸入級完全對稱:

由于N1與N2中電流相等,且N1的柵極和漏極相連,根據平衡條件,N2的漏極電壓應基本上等于N1的柵極電壓,則

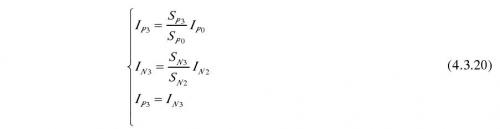

由(4.3.19)式和(4.3.20)式可以確定P3、N3的尺寸。至此,過充比較器的前兩級已設計完成。還需驗證比較器是否滿足分辨率要求,設計過充比較器的檢測精度為±25mV,提高分辨率的方法是提高比較器的增益,前兩級的增益公式為

在亞閾值區的增益比強反型大,一般能滿足要求。

后兩級參數的選擇主要根據COMP_OC的上跳變延時T RISE確定。根據對系統的分析,過充電保護釋放檢測精度相對低一些,設計其延時為0.4ms ~0.8ms.顯然TRISE主要通過恒流IN4對電容C1放電產生的延時Δt和前兩級的延時決定。

4.3.3其它重要功能電路

1過流短路保護電路

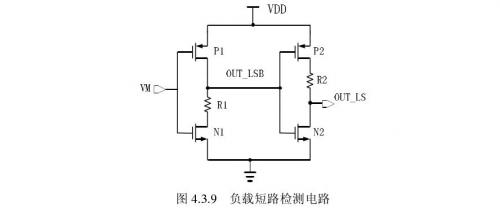

負載短路檢測電路如圖4.3.9所示,當電池在放電過程中出現負載短路時,保護電路VM端的電位就會大于或等于特定的值VSHORT。短路保護電路的主要作用是當VM≥VSHORT時, 通過兩級反相放大,使OUT_LSB輸出由低電平變為高電平,立即將外接開關管FET1關斷,實現短路保護功能。OUT_LS信號控制電路的Power Down狀態,當出現短路保護狀態時,OUT_LS由高電平變為低電平,此時若過放比較器輸出COMP_OD由高電平跳變到低電平(即出現過放狀態),再 經過過放延時后,保護電路進入Power Down狀態。

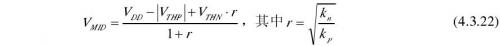

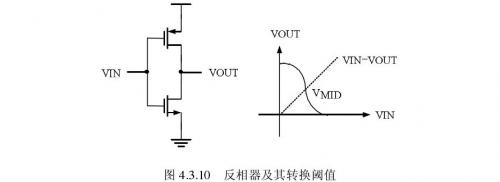

電路的工作原理十分簡單,它通過兩級反相器來實現信號翻轉,反相器及其轉換閾值V MID的定義如圖4.3.10.因此有

式(4.3.21)可知,增加PMOS的寬長比或減小NMOS的寬長比可以使VMID分別向VDD與GND方向移動。因此,為了達到短路保護的設計要求,可調節寬長比來調整V MID,同時為了限制信號翻轉時的電流,可在兩MOS管之間加上電阻,調節電阻同樣可調整VMID。本電路的功能主要由第一級反相器完成,第二級反相器用于改善波型。

2非正常充電電流檢測電路

非正常充電電流檢測比較器的主要功能是檢測充電過程中的過流現象;另外,可以用此電路實現充電器檢測功能,即在過放電狀態下連接上充電器,假如VM電壓低于充電檢測電壓VCHA,則解除過放電遲滯。因此,上述兩個功能都可歸結為檢測負電壓。

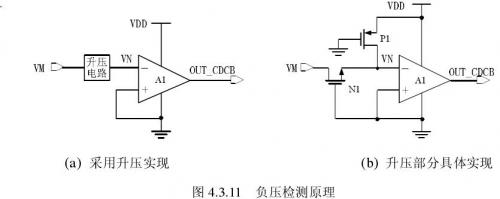

負電壓的檢測不同于正電壓的檢測,為了簡化設計,在過零比較器的基礎上引入升壓電路,如圖4.3.11(a)所示,當VM≥VCHA時,使得VN≥0,這樣就避開了負的基準電壓源的設計。

為 了降低功耗,可以采用CMOS電路來實現上述的負壓比較器,如圖4.3.11(b)所示。PMOS管P1和NMOS管N2的柵極都接地。當N1的柵源電壓 小于它的閾值電壓時,N1截止,而P1始終導通,VN端電位因為大于A1比較器同相輸入端的GND電位,而使輸出OUT_CDCB為低電平。隨著VM端電 位向負方向的增大,N1逐漸導通,最后使得VN端電位變負,輸出OUT_CDCB由此變為高電平。

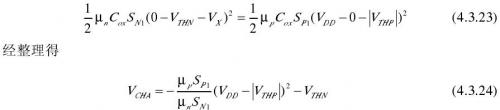

圖4.3.11中V N =0時的輸入電壓即為檢測電壓V CHA,此時P1和N1處于飽和狀態,而且下列關系式成立

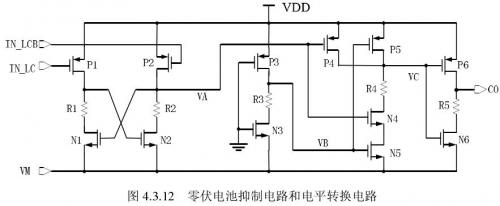

由(4.3.24)式可知,本電路中檢測電壓|VCHA|的取值只能大于N1的閾值電壓,改變P1和N1的寬長比可改變檢測電壓VCHA。當N1未導通時,電路消耗的電流較小;當N1導通時,就會有電源到地的通路,為了減小消耗的電流,一般取P1的寬長比小于1. 3零伏充電抑制電路零伏電池抑制電路目的是在電池電壓低于一定值(V0INH)時,使CO端輸出有效的低電平,禁止充電器對電池進行充電。而電平轉換電路的功能也是要使CO端輸出有效的低電平,以控制驅動片外的充電控制功率管FET2,因此兩種功能可組合在同一電路中實現。如圖4.3.12為零伏電池抑制電路檢測結構圖。

電平轉換功能主要由P1、P2、N1、N2、R1和R2組成的電路完成;零伏抑制功能主要由P3、N3和R3完成;P4、P5、N4、N5和R4組成的與非門在電平轉換功能和零伏抑制功能之間進行選擇。

以 R3為例,分析電路中電阻的作用:當電池電壓V DD很低時,接上電的瞬間,VM為一個絕對值很大的負值,N4管很容易導通,但如果此時V DD還沒有低到使P3管關閉時,就會在VDD端到VM之間產生直流通路,形成大電流,為了避免這種情況出現,在P管和N管之間加入電阻,從電阻的上端輸出 信號。

由于P3、N3的柵極接地,出現兩管同時導通的可能性最大,時間最長,R3就應取稍大些。

電路需要將邏輯低電平轉化為與VM相同的電位。而VM的電位有可能很負,在電路轉換瞬間,VDD端和VM之間的高電壓很容易將普通的MOS管擊穿。基于此,本電路的所有管子都采用高壓非對稱管。

4.3小結

本章的內容是上章的系統分析設計基礎上,選擇適當工藝后的具體電路實現。

首先分析了電池管理芯片所適用的低功耗混合信號設計流程,探討了所涉及的設計工具,并指出在電路實現層次,模擬電路和數字電路模塊可以分別設計驗證,并為下一章的版圖實現和后模擬驗證提供了正確的設計思路。

數字模塊設計中,分析了系統的有限狀態機模型,同時在上一章所提出的功耗管理模型基礎上,設計了延時模塊和邏輯控制模塊,不僅能完成系統所需要的基本功能,而且能及時檢測負載性質和狀態,由數字電路內部輸出相應的功耗管理信號。

模 擬電路模塊設計時,首先對電池管理芯片中可通用的基礎電路進行了重點分析設計。采用線性電路實現了電源電壓取樣;從降低數模電路的電源耦合噪聲、降低電流 消耗出發,提出了基于熱電壓U T的亞閾值自偏置電路的設計思想;在此基礎上,為了進一步提高所用工藝實現的可能性,分別設計了無電阻電流偏置電路和電流求和型電壓基準源電路。接著,詳 細介紹了模塊中檢測精度要求最為嚴格過充比較器,對其它的比較器電路有一定的實踐指導作用。最后,對芯片中的關鍵功能模塊給出了完整的設計方案。

本章也是下一章中芯片驗證及實現的基礎。

評論