基于ADF4106的低相噪本振設計

作者/ 曹陽1 ,2 1.中國電子科技集團公司第41研究所 研發1部(安徽 蚌埠 233006) 2.電子信息測試技術安徽省重點實驗室(安徽 蚌埠 233006)

本文引用地址:http://www.j9360.com/article/201705/359748.htm*基金項目:國家科技重大專項面向R12 LTE-Advanced終端綜合測試儀(編號:2016ZX03002010)

曹陽(1989-),男,助理工程師,研究方向:通信測量儀器的研究與開發。

摘要:為了實現低相噪的本振信號輸出,本文設計出一種基于鎖相環芯片ADF4106的低相噪本振源。通過實際調試,測試結果滿足設計要求,并作為第二點頻本振應用于一款通信測試儀器的中。

引言

低相噪本振是通信測試儀器等現代電子設備系統的核心模塊,它對電子設備系統的性能起著決定性的作用。對于低相噪本振的設計,許多人做了大量的研究[1-4],本文利用鎖相環芯片ADF4106設計出一種低相噪本振源,作為第二點頻本振應用于一款通信測試儀器中,為測試儀器提供一個5400MHz的下變頻信號。

1 方案設計

1.1 設計指標

輸出頻率:5400MHz

相位噪聲:≤-110dBc@1kHz

相位噪聲:≤-118dBc@10kHz

輸出功率范圍:10~12dBm

1.2 設計方案

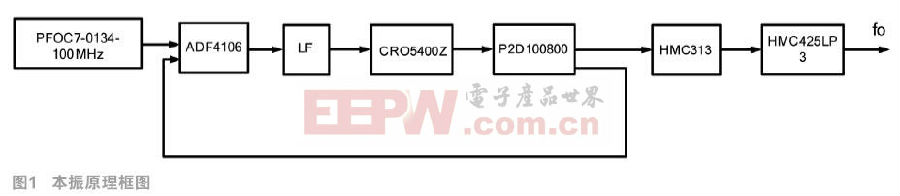

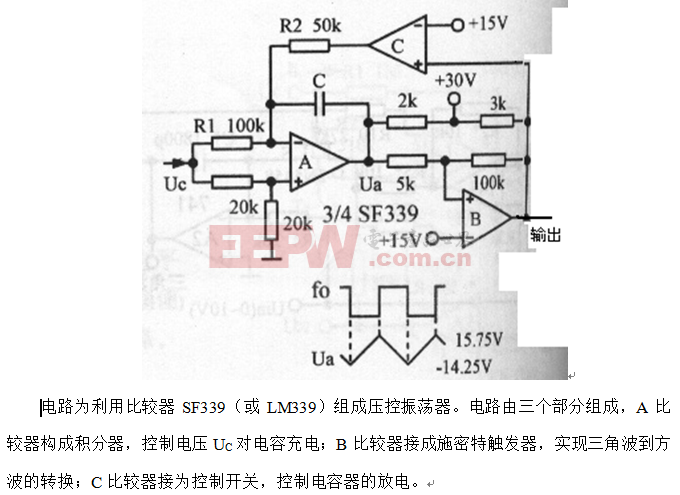

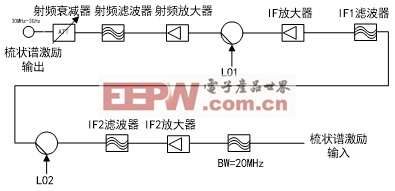

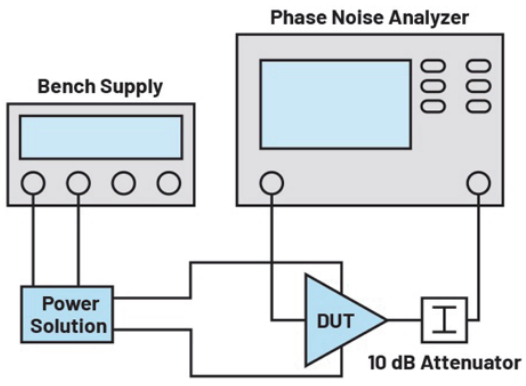

本方案利用Z-COM公司的壓控振蕩器CRO5400Z產生5400MHz的輸出頻率,經過功率分配后,一路通過功率調理電路后輸出給整機作為第二點頻本振,另一路反饋進入具有分頻、鑒相功能的ADI公司的可編程鎖相環芯片ADF4106,與100MHz參考經過分頻后進行鑒相,通過環路濾波器濾波后驅動壓控振蕩器產生5400MHz的輸出頻率。原理框圖如圖1所示。

2 關鍵電路設計

2.1 ADF4106電路設計

ADF4106由一個數字鑒相器PD、一個充電泵CP、一個可編程的基準分頻器、可編程的A(6位)、B(13位)計數器及一個雙模式的前置分頻器(P/P+1)組成。內部結構原理圖如圖2所示。

利用ADF4106和環路濾波器LF(Loop Filter)、壓控振蕩器VCO(Voltage Controlled Oscillator)可以構成一個鎖相環PLL(Phase Locked Loop)。根據ADF4106datasheet提供的公式:

![]()

評論