基于82527的CAN總線智能流量傳感器節點設計

引言 本文引用地址:http://www.j9360.com/article/201612/329372.htmCAN(ControllerAreaNetwork,控制局域網)屬于工業現場總線,是德國Bosch公司20世紀80年代初作為解決現代汽車中眾多的控制與測試儀器間的數據交換而開發的一種通信協議。1993年11月,ISO正式頒布了高速通信控制局域網(CAN)的國際標準(ISO11898)。CAN總線系統中現場數據的采集由傳感器完成,目前,帶有CAN總線接口的傳感器種類還不多,價格也較貴。本文給出一種由8051單片機和82527獨立CAN總線控制器為核心構成的智能節點電路,在普通傳感器基礎上形成可接收8路模擬量輸入和智能傳感器節點。

1 獨立CAN總線控制器82527介紹 82527是Intel公司生產的獨立CAN總線控制器,可通過并行總線與Intel和Motrorola的控制器接口;支持CAN規程2.0B標準,具有接收和發送功能并可完成報文濾波。82527采用CHMOS5V工藝制造,44腳PLCC封裝,使用溫度為-44~+125℃,其引腳的排列和定義參見參考文獻[1]。 (1)82527的時鐘信號 82527的運行由2種時鐘控制:系統時鐘SCLK和寄存器時鐘MCLK。SCLK由外部晶振獲得,MCLK對SCLK分頻獲得。CAN總線的位定時依據SCLK的頻率,而MCLK為寄存器操作提供時鐘。SCLK頻率可以等于外部晶振XTAL,也可以是其頻率的1/2;MCLK的頻率可以等于SCLK或是其頻率的1/2。系統復位后的默認設置是SCLK=XTAL/2,MCLK=SCLK/2。 (2)82527的工作模式 82527有5種工作模式:Intel方式8位分時復用模式;Intel方式16位分時復用模式;串行接口模式;非Intel方式8位分時復用模式;8位非分時復用模式。本文應用Intel方式8位分時復用模式,此時82527的30和44腳接地。 (3)82527的寄存器結構[2] 82527的寄存器地址為00~FFH.下面根據需要對寄存器給予介紹。 ①控制寄存器(00H):

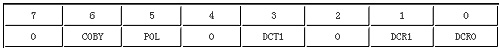

CCE——改變配置允許位,高電平有效。該位有效時允許CPU對配置寄存器1FH、2FH、3FH、4FH、9FH、AFH寫操作。 EIE——錯誤中斷允許位,高電平有效。該位一般置1,當總線上產生異常數量的錯誤時中斷CPU。 SIE——狀態改變中斷允許位,高電平有效。該位一般置0。 IE——中斷允許位,高電平有效。 INIT——軟件初始化允許位,高電平有效。該位有效時,CAN停止收發報文,TX0和TX1為隱性電平1。在硬件復位和總線關閉時該位被置位。 ②CPU接口寄存器(02H):

RSTST——硬件復位狀態位。該位由82527寫入,為1時硬件復位激活,不允許對82527訪問;為0時允許對82527訪問。 DSC——SCLK分頻位。該位為1,SCLK=XTAL/2;為0,SCLK=XTAL。 DMC——MCLK分頻位。該位為1,MCLK=SCLK/2;為0,MCLK=SCLK。 PWD——掉電模式使能位,高電平有效。 SLEEP——睡眠模式使能位,高電平有效。 MUX——低速物理層復用標志位。該位為1,ISO低速物理層激活,PIN24=VCC/2,PIN11=INT#(#表示取反);該位為0,PIN24=INT#,PIN11=P2.6。 CEN——時鐘輸出允許位,高電平有效。 ③標準全局屏蔽寄存器(06~07H)。該寄存器用于具有標準標識符的報文,或XTD置0的報文寄存器。該方式稱為報文接收濾波。當某位為1時,報文標識符的相應位必須匹配;為0時,不必匹配。 ④擴展全局屏蔽寄存器(08~0BH)。該寄存器用于擴展報文格式,或XTD置1的報文寄存器,其作用與③相同。

⑤總線配置寄存器(2FH): COBY——旁路輸入比較器標志位,高電平有效。 POL——極性標志位。為1,如果旁路輸入比較器,RX0的輸入邏輯1為顯性,邏輯0為隱性;為0,則反之。 DCT1——TX1輸出切斷控制位。為1,TX1輸出不被驅動,該模式用于1根總線的情況,2根差分導線短路;為0,TX1輸出被驅動。 DCR1——RX1輸入切斷控制位。為1,RX1與輸入比較器的反相端斷開,接至VCC/2;為0,RX1接至輸入比較器反相端。 DCR0——RX0輸入切斷控制位。作用與DCR1相同,此時RX0接至比較器同相端。

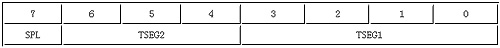

⑥位定時寄存器0(3FH); SJW——同步跳轉寬度位場,編程值1~3。 BRP——波特率分頻位場,編程值0~63。

⑦位定時寄存器1(4FH): SPL——采樣模式標志位。1表示每位采樣3次;0表示每位采樣1次。 TSEG1——時間段1位場,編程值2~15。 TSEG1——時間段2位場,編程值1~7。 波特率=XTAL/[(DSC+1)*(BRP+1)*(3+TSEG1+TSEG2)> ⑧報文寄存器(把每個寄存器的第1字節地址作為基址BASE)。

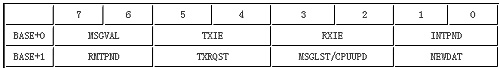

◇控制寄存器0,1(BASE+0,BASET+1) MSGVAL——報文寄存器有效標志位,高電平有效。10置位,01復位。 TXIE——發送中斷允許標志位,高電平有效。10置位,01復位。 RXIE——接收中斷允許標志位,高電平有效,10置位,01復位。 INTPND——中斷申請標志位,高電平有效。10置位,01復位。 RMTPND——遠程幀申請標志位,高電平有效。10置位,01復位。 TXRQST——請求發送標志位,高電平有效。10置位,01復位。 MSGLST——報文丟失標志位,只用于接收報文寄存器。10表示未讀報文被新報文覆蓋,01表示未覆蓋。 CPUUPD——CPU更新標志位,只用于發送報文寄存器。10報文不被發送,01報文可發送。 NEWDAT——新數據標志位。10表示向寄存器寫入了新數據,01表示無新數據寫入。 ◇仲裁寄存器0,1,2,3(BASE+2-BASE+5) 存儲報文標識符。

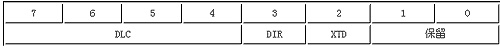

◇報文配置寄存器(BASE+6) DLC——數據長度編碼,編程值0~8。 DIR——方向標志位。1發送,0接收。 XTD——標準/擴展標識符標志位。1擴展標識符,0標準標識符。 ◇數據寄存器(BASE+7-BASE+14) 82527存儲報文時,8個數據字節均被寫入,未用到的字節數據是隨機的。 2硬件電路設計 智能節點的電路如圖1所示(圖中6264略去)。 在硬件設計中,由ADC0809完成對8路模擬置的轉換,與8051的信息交換采用查詢方式,地址BFF8~BFFFH,其時鐘可由ALE二分頻獲得;82527完成與CAN總線的信息交換。本設計中,旁路了輸入比較器,與8051的信息交換采用中斷方式,地址7F00~7FFFH,可以用82527的P1口和P2口對開關量采集或對繼電器進行控制。82C250提供82527和物理總線間的接口,提高接收和發送能力。可根據需要擴展程序存儲器。 3軟件設計

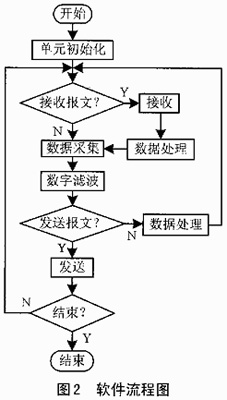

本設計軟件采用MCS-51匯編語言編寫,程序框圖如圖2所示。 82527的初始化程序如下: INT:MOVDPTR,#0FF02H MOVA,#00H MOVX@DPTR,A;SCLK=XTAL ;MCLK=SCLK,CLKOUT無效 MOVDPTR,#0FF00H MOVA,#41H MOVX@DPTR,A;置位CCE,INIT MOVDPTR,#0FF2FH MOVA,#48H MOVX@DPTR,A;旁路輸入比較器設置1位隱性,0為顯性,RX1無效 MOVDPTR,#0FF3FH; MOVA,#43H; MOVX@DPTR,A;SJW=2,BRP=3 MOVDPTR,#0FF4FH MOVA,#0EAH MOVX@DPTR,A;SPL=1,TSEG1=7,TSEG2=6此時波特率為100Kbps MOVDPTR,#0FF00H; MOVA,#01H MOVX@DPTR,A;禁止對配置寄存器的訪問 MOVDPTR,#0FF10H; MOVA,#55H; MOVX@DPTR,A; INCDPTR; MOVX@DPTR,A; ? ? ? MOVDPTR,#0FFF0H; MOVA,#55H; MOVX@DPTR,A INCDPTR; MOVX@DPTR,A;報文寄存器控制位初始化 MOVR0,#06H; MOVDPTR,#0FF06H; MOVA,#0FFH; L1:MOVX@DPTR,A;報文標識符需全部匹配 INCDPTR DJNZR0,L1; MOVDPTR,#0FF16H; MOVA,#8CH;報文寄存器1可發送8個字節擴展報文 MOVX@DPTR,A; MOVDPTR,#0FF26H; MOVA,#84H; MOVX@DPTR,A;報文寄存器2可接收8個字節擴展報文 MOVDPTR,#0FF00H; MOVA,#00H; MOVX@DPTR,A;初始化結束 RET |

評論