基于stm32的數字示波器設計方案

0 引言

本文引用地址:http://www.j9360.com/article/201611/340656.htm隨著集成電路的發展和數字信號處理技術的采用,數字示波器已成為集顯示、測量、運算、分析、記錄等各種功能于一體的智能化測量儀器。數字示波器在性能上也逐漸超越模擬示波器,并有取而代之的趨勢。與模擬示波器相比,數字示波器不僅具有可存儲波形、體積小、功耗低,使用方便等優點,而且還具有強大的信號實時處理分析功能。因此,數字示波器的使用越來越廣泛。目前我國國內自主研發的高性能數字示波器還是比較少,廣泛使用的仍是國外產品。因此,有必要對高性能數字示波器進行廣泛和深入研究。

本文通過采用高速高性能器件,設計了一實時采樣率為60 msa/s的寬帶數字示波器。

1 數字示波器的性能參數設計

數字存儲示波器的指標很多,包括采樣率、帶寬、靈敏度、通道數、存儲容量、掃描時間和最大輸入電壓等。其中關鍵的技術指標主要有采樣率、垂直靈敏度(分辨率)、水平掃描速度(分辨率)。這幾項指標直接與所選a/d、fifo和高速運放器件的性能,以及電路設計有關。下面根據所選器件的性能參數,合理地分析和確定示波器的采樣率和分辨率。

1.1 采樣率與水平掃描分辨率

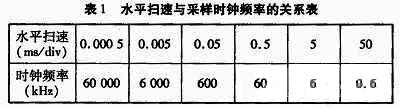

采樣率主要取決于a/d轉換器的轉換速率,常用每秒取樣點數sa/s(sample/second)來表示。本系統設計最高實時采樣率為60msa/ s,若進一步提高采樣率可采用文獻提出的等效采樣技術,不過等效采樣技術的軟硬件和價格成本很高。為了使示波器具有較高的信號波形分析細節,采用數字內插技術來恢復和重建信號波形。文獻中詳細論述了線性內插和正弦內插算法在示波器設計中的應用問題。因此,對這兩種內插算法不再詳細論述,在本文設計中直接引用文獻中的研究成果。根據文獻研究結果,取信號每周期采樣點數為20,插值倍數為4。水平顯示像素點數為400個,共10格。水平掃速與采樣時鐘頻率的關系表如下。

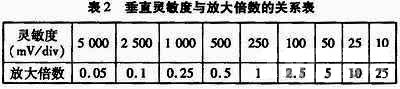

1.2 垂直靈敏度

垂直分辨率的高低直接影響數字示波器對波形細節的顯示,垂直分辨率越高,則示波器上的信號波形細節越小,它取決于a/d轉換精度和tft的顯示分辨率。本文設計中取最大采樣輸入電壓為2 vpp,垂直刻度為8格,共256個像素點,因此垂直精度為0.25 v/格。共設計9個靈敏度檔位,每檔靈敏度與程控放大倍數的關系如表2所示。

2 數字示波器的硬件設計

2.1 系統硬件總體框圖

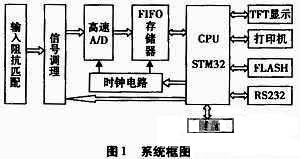

系統硬件總體框圖如圖1所示,主要由stm32控制單元,信號輸入阻抗匹配單元,信號調理單元,a/d采樣與fifo存儲單元,時鐘單元,tft顯示單元等組成。輸入信號經阻抗匹配后,送入信號調理單元,將信號的幅度放大或衰減到適合a/d采樣的范圍內,a/d采樣單元對幅度為2vpp的信號進行a/d采樣,并將采樣結果存入fifo單元中。cpu從fifo中讀存數據并進行內插運算,然后根據用戶通過鍵盤輸入的指令將信號波形顯示在tft液晶屏上。另外,cpu還可以將數據通過rs232接口上傳給上位機,或進行打印等處理。

2.2 輸入阻抗匹配電路

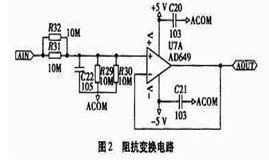

對于低速數據采集,由于信號反射對信號的傳輸過程影響微乎其微,所以低速數據采集系統良好的高阻抗性能,對提高系統的測量精確度有很大的意義。本設計中采用電壓跟隨器實現阻抗變換,數據采集阻抗變換電路的設計方案如圖2所示,其輸入阻抗為10mω。

2.3 信號調理電路

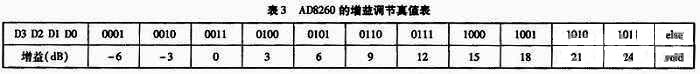

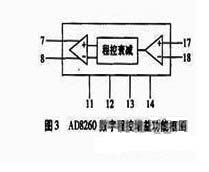

信號調理電路主要采用具有可變增益的數字程控放大器ad8260。ad8260是ad公司生產的一款大電流驅動器及低噪聲數字可編程可變增益放大器。該器件增益調節范圍為-6 db~+24 db,可調增益的-3 db帶寬為230mhz,可采取單電源或雙電源供電。主要用于數字控制自動增益系統、收發信號處理等領域。本設計主要使用其數字控制自動增益功能。ad8260內部的數字程控增益功能框圖如圖3所示。經阻抗匹配后的信號可直接輸入ad8260的17、18腳,經ad8260內部前端放大器6 db的固定增益放大,-30 db程控衰減以及末級放大器18 db固定增益放大后,由7和8腳輸出。第11、12、13、14腳為四位數字控制信號(d0、d1、d2、d3),與stm32的i/o口直接連接,實現增益控制。表3給出了ad8260增益調節真值表。

2.4 a/d和fifo電路

在數據采集電路設計中,選用bb公司的8位高速ad轉換器ads830e,最高采樣頻率為60 msa/s,最低采樣頻率為10 ksa/s。8位轉換精度的顯示分辨率為256格,能夠滿足所選用分辨率為640*480的tft顯示模塊。fifo存儲器采用idt7204高速緩存,其緩存深度達1 024 k。fifo存儲器是一種雙口的sram,沒有地址線,隨著寫入或讀取信號對數據地址指針進行遞加或遞減,來實現尋址。

2.5 時鐘電路

時鐘產生電路為ad轉換器提供一系列的采樣時鐘信號,共有8種頻率,分別對應著不同的水平掃速。時鐘產生電路主要由高穩定度的溫補晶振,分頻器74ls390,多路選擇器74f151以及分頻器74f74觸發器構成。基準時鐘信號由一塊60 mhz的溫度補償型有源晶體模塊提供,輸出的60 mhz信號經過分頻器的多次分頻得到8種不同的頻率,然后送入多路選擇器74f151。stm32通過對74f151的三根選通信號線進行控制來選擇所需的采樣頻率。另外,中央控制器采用stm32處理器,主頻設為80 mhz。顯示器采用分辨率為640*480的tft顯示模塊,與stm32之間采用spi接口。與其它上位機通信采用rs232口。

3 系統軟件設計

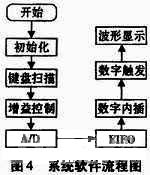

系統軟件設計采用模塊化設計方法,整個程序主要由初始化程序、人機交互菜單程序、鍵盤掃描程序、觸發程序、顯示程序和數據采集及頻率控制程序組成。系統軟件的流程圖如圖4所示。

4 實驗測試

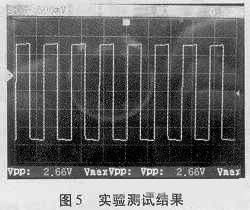

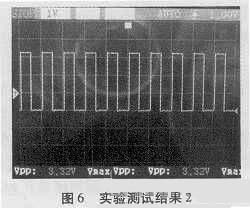

在實驗室對研制的樣品機進行了測試實驗,圖5和圖6分別顯示了頻率為16.2 khz和1 khz的方波信號。由測試數據分析可得:垂直靈敏度滿足要求,電壓測量誤差≤5%,輸入端輸入阻抗大于2 mω,實驗結果達到了設計要求。

5 小結

為實現一個高采樣率,寬頻帶的便攜式數字存儲示波器,設計了以stm32為控制核心的數字示波器。硬件平臺主要采用了ad8260數字程控增益放大器作為前端信號調理電路,ads830高速寬帶模數轉換器和idt7204高速緩存作為數字采集電路,以及信號波形采用了tft彩屏顯示。另外,通過采用數字內插的數字信號處理算法來重建和還原信號波形,進而改善了信號波形顯示細節。最后對研制樣品進行了實驗室測試,實驗結果表明硬件設計思路與軟件及算法的處理是正確的,性能參數達到設計要求,可以應用在工程實踐中。

數字示波器在信號顯示,處理以及帶寬等方面比傳統模擬示波器更有優勢,因此數字示波器是今后示波器發展的重要方向。本文采用stm32高性能arm處理器作為核心控制芯片,能夠滿足tft彩色波形顯示,數字插值算法處理等。通過采用高速ad和fifo器件,實現了高采樣率,寬頻帶的技術要求。

評論