如何用低成本的ARM Cortex-M微控制器讓家電變得更安全

電子部分參照另一個標準,即適用于各種應用領域的IEC60730自動電子控制標準。對于嵌入式系統開發人員,附件H對于嵌入式系統開發人員尤為重要,因為該附件是關于可編程器件。白色家電通常使用多個微控制器:一個微控制器負責管理控制臺,另一個管理閥門和電機控制。

本文引用地址:http://www.j9360.com/article/201611/323113.htm根據設備故障導致的危險程度,該標準將軟件分為A、B、C三類。如果家電安全不依靠軟件,則該家電屬于A類,如室內溫控器或照明控制器。相反,如果軟件用于防止安全隱患,如電子點火燃氣灶歸為C類。本文不探討C類。電子控制系統防止不安全操作的家電多數屬于B類,如洗衣機,其安全隱患與電控門鎖或電機熱關斷有關。

IEC60730附件H的表格 H.11.12.7 列出了B類和C類軟件需測試的微控制器元器件、需檢測的故障和接受的安全措施,檢測內容包括監視CPU(寄存器和程序計數器)、中斷(處理和執行)和時鐘頻率,檢驗易失性存儲器(RAM) 、非易失性存儲器(閃存和 EEPROM)、外部通信以及外設。

這些檢測均在微控制器引導過程中甚至在系統執行代碼前完成,主要原因是RAM測試具有‘破壞性’,可導致初始化的變量損壞。

在RAM檢測中,標準要求B類設備定期做單一位DC故障檢測(如嵌入存儲器固定故障或耦合故障)。因為多數入門級微控制器的SRAM無校驗位,所以該檢測必須由軟件來完成。March算法通過限定數量的測試來發現這些故障,March C測試最適合B類(使用10N次測試,N為被測試存儲地址的數量),但是March X(6N次測試)在某些特定情況也被測試機構接受。測試完成后,RAM存儲器內容被清除(因此,又稱為‘破壞性測試’)。

復位后執行March測試不會產生特別的問題。除略微降低開機速度外,沒有什么實際缺點,因為嵌入式SRAM很小,開機速度降低甚至都不會被注意到。

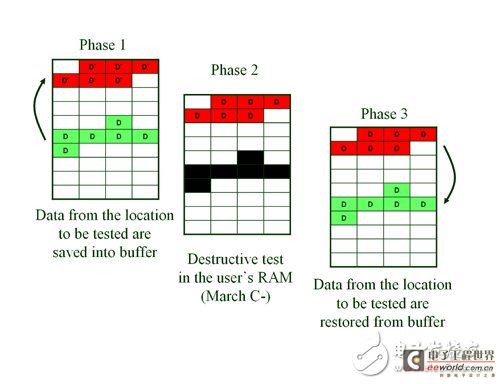

相反,如果在運行期間重復這個測試,可能會產生很大的問題。首先,測試必須透明:應用無需特定的協議即可處理RAM,好像沒有測試一樣。實際而言,這增加了下列條件:

· 測試必須是一個中斷處理程序(ISR),且給予最高的處理優先級,可禁止應用程序在測試過程中訪問數據。

· 必須配備緩存,以便提前備份被檢驗的RAM內容,最后在應用任務重新運行前恢復RAM內容。顯然,也必須定檢驗證緩存。

其次,應用任務暫停時間不宜過長。該測試通常分為若干個小測試,以限制占用頂層任務的時間。一次測試的地址不得少于3個連續地址(這是耦合故障測試覆蓋率的硬性要求),這表示不少于30次連續的March C算法讀寫操作。

雖然實際應用證明該解決方案效果不錯,而且在業界十分流行,但還是存在不少的缺點。

我們先從軟件工程角度剖析這些問題。結構化編程的優點略過,只分析相關的局限性問題:

· 封裝問題:C模塊必須將部分內部變量提高至全局變量,不再接受編譯器參照跨模塊訪問進行的完整校驗。

· 低任務隔離度和低模塊化:測試對每個安全關鍵的軟件模塊強制進行訪問測試,使增加新功能變得更加復雜。

如果將數據損壞的機率與讀寫次數聯系在一起,該解決方案的數據損壞風險是比較高的。雖然逆向冗余存儲安全關鍵變量可降低風險,但同時也會擴大存儲器B類測試的容量。

從微控制器資源角度看,測試代碼占用ROM和RAM空間,以及CPU帶寬:除正常處理任務外,如果內核臨時無法吸納測試負荷,就必須在家電運行關鍵階段終止測試。

最后,運行時RAM校驗會影響實時響應性(可能延遲甚至暫停其它中斷處理程序),并可能與低延時或緊急任務要求沖突。測試程序的代碼長度無法最小化:耗合故障測試對被測連續存儲地址的數量有下限要求。如果軟件必須管理地址解擾,使其符合存儲器物理布局,則復雜度更高。圖1所示是軟件如何在運行時處理部分RAM測試。

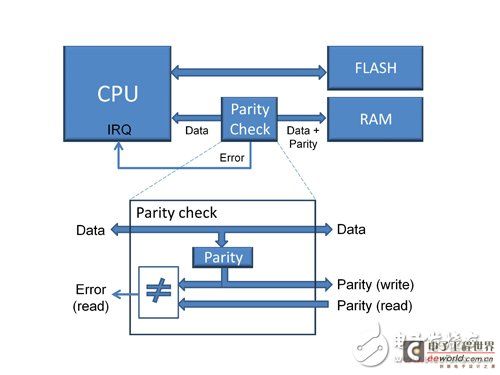

IEC60730標準另提供一個由硬件校驗位組成的解決方案。雖然這是一個標準的DRAM存儲器流程,但是很少用于通用微控制器。不過,先進的芯片制程節點使得該方法更具成本效益。

硬件測試解決方案的本質是在每個存儲地址增加一個校驗位:存儲器每寫一次,計算一次校驗位,并將校驗位計算值與數據存儲在一起。當讀取數據時,同樣計算校驗值,然后與參考值對比,如圖2所示。如果數值不同,無論是數據損壞還是校驗位損壞,中斷或異常信號線都會置位。處理器內核將使用一個專用安全中斷處理程序處理錯誤,并關閉家電的電源。第二步,內核可能重啟應用(熱復位)或停止家電運行,同時顯示檢修代碼。

該解決方案的優勢十分明顯。B類RAM校驗變得完全透明:

· 不影響軟件開發方法

· 不必開發某一個微控制器廠商專用的測試程序,只需開發一個在任何情況下都會出現的全局故障處理函數

· 無需專用的RAM分區和鏈接腳本

· 不占用CPU帶寬(校驗不會增加存儲器讀操作延遲)

· 最優的實時性能

最后一個優勢是該解決方案在啟動時無需進行完整的RAM校驗,而且在上電復位后,寄偶校驗立即激活,因此降低了引導時間。

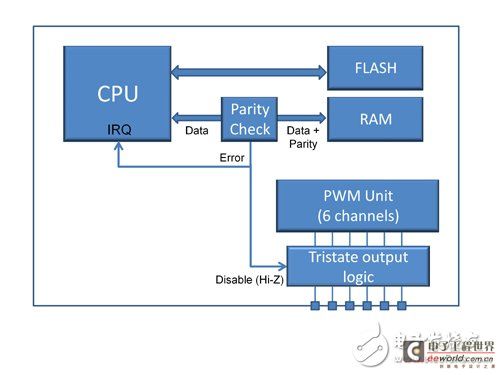

由于擁有高能效、靜音運行、高可靠性的特點,無刷電機被廣泛用于家電,但是需要復雜的控制算法和專用的PWM外設,需要特別注意故障防護和安全關機。因此,RAM校驗機制可提高可靠性和響應性,不是用軟件管理安全關閉功能,而是直接向PWM外設發送校驗錯誤信號,自動觸發緊急停機功能,避免系統時鐘和軟件相關的延遲。圖3所示框圖描述了一個實用的解決方案。

還必須注意系統的其它關鍵參數。電源監控系統可以設置電壓,如果Vdd 電壓降至預設電壓值,系統將發出一個中斷命令。同樣,時鐘安全系統檢查主時鐘運行是否正常,如果出現異常,則發出一個中斷命令。此外,當發生硬故障、在NMI處理程序內部出現錯誤或者在引導過程中發生總線故障時,Cortex內核進入鎖保護時態,在芯片級提供一個狀態顯示信號。這三個事件以及校驗值合并,產生一個內部緊急關斷信號,信號本身與外部斷路(break)輸入進行或運算。

該標準還需要一個防失效時鐘電路。當晶振失效時,時鐘安全系統外設(CSS)可自動將主時鐘切換到內部高速振蕩器,從而實現部分防失效功能。此外,還需要一個通過對比外部預計頻率與內部頻率來監視外部時鐘的方法。實時時鐘定時器可由LSI (內部低速)阻容振蕩器驅動,以便精確地測量主系統時鐘,發現晶體副諧波引起的50%的變化。在系統級,這可節省50/60Hz電網過零檢測電路的成本。

該標準提出一個獨立的時隙監視方案,防止CPU在程序計數器故障時失控,這是看門狗定時器的職責,多數微控制器均內置看門狗。但是,標準規定看門狗必須完全獨立。因此,意法半導體的32位Cortex-M STM32系列微控制器有兩個看門狗:第一個窗口看門狗使用主時鐘;第二個看門狗使用獨立的內部振蕩器,通過閃存內的選項字節啟動。這種設計可確保在晶體失效時,無論時鐘電路配置如何,都能確保至少有一個看門狗在運行。

最后,微控制器還內置一個32位硬件CRC計算器,可大幅加快閃存內容完整性檢查,同時將相關CPU負荷(在運行時占用的時間)降至可忽略不計的水平。該外設甚至可以用DMA控制器驅動。在微控制器運行期間,閃存數據完整性檢查可在后臺進行。

硬件校驗長期以來只用于計算機DRAM模塊和高可靠性系統。該方法被引進嵌入式市場的通用微控制器,如基于Cortex-M0的STM32F0x產品,隨著系統監控和安全功能數量日益增加,該方案可簡化產品認證、安全開發的執行,最重要一點是使家電變得更安全。

評論