I2C總線學習終結,開始SPI總線的學習

帶著這個問題,我在圖書館找了好幾天的資料。終于弄懂了。

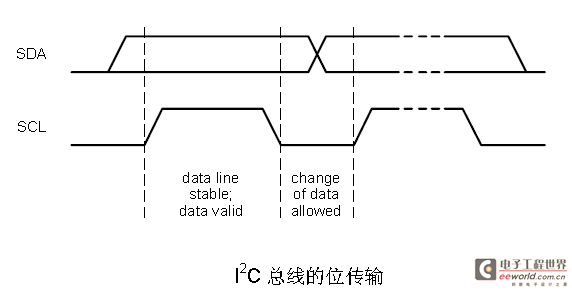

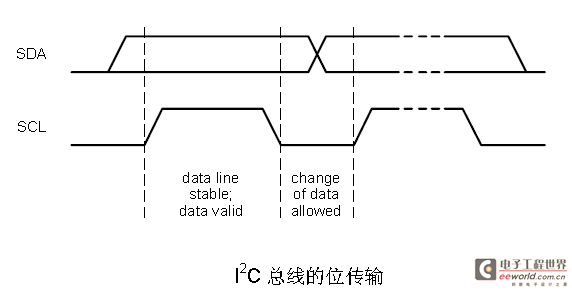

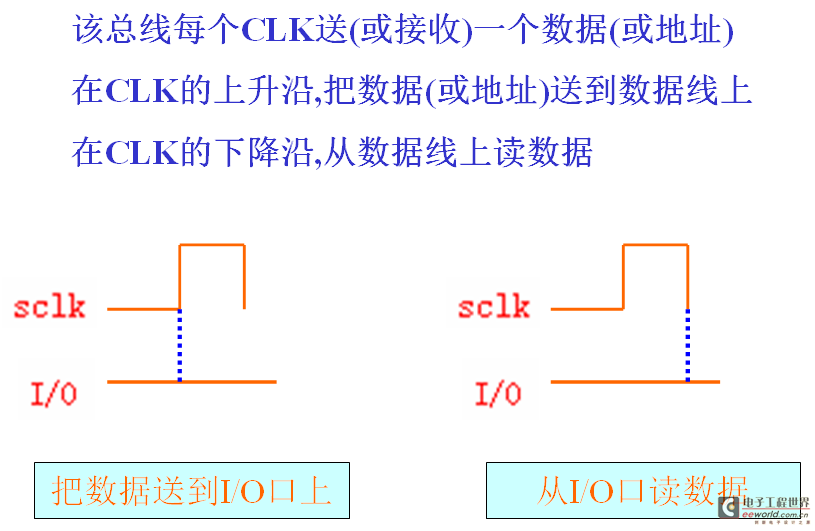

每bit數據定義

下面再來看一下IIC總線時序的具體定義:

其中, 是數據建立的時間;

是數據建立的時間; 是數據保持時間。上升沿將數據送到SDA線上,

是數據保持時間。上升沿將數據送到SDA線上, 是建立時間。高電平期間數據穩定,等待下降沿讀取SDA線上的數據。下降沿從SDA線上讀取數據,下降沿之后的

是建立時間。高電平期間數據穩定,等待下降沿讀取SDA線上的數據。下降沿從SDA線上讀取數據,下降沿之后的 是保持時間。

是保持時間。

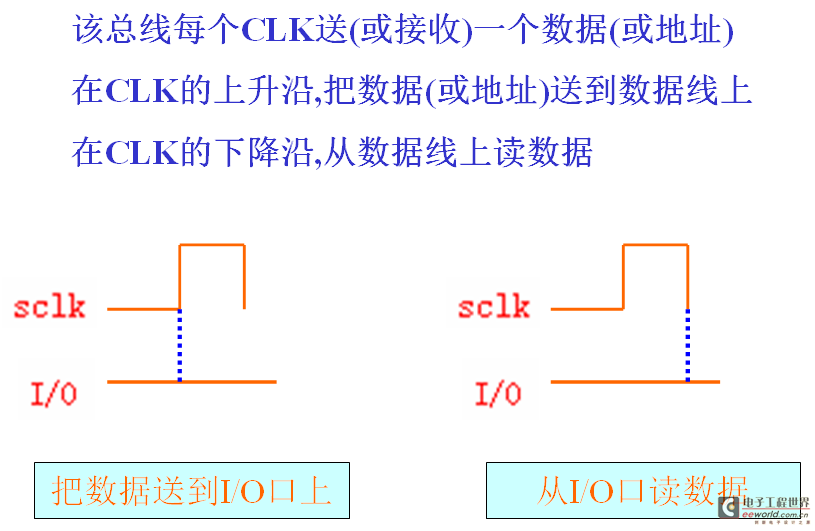

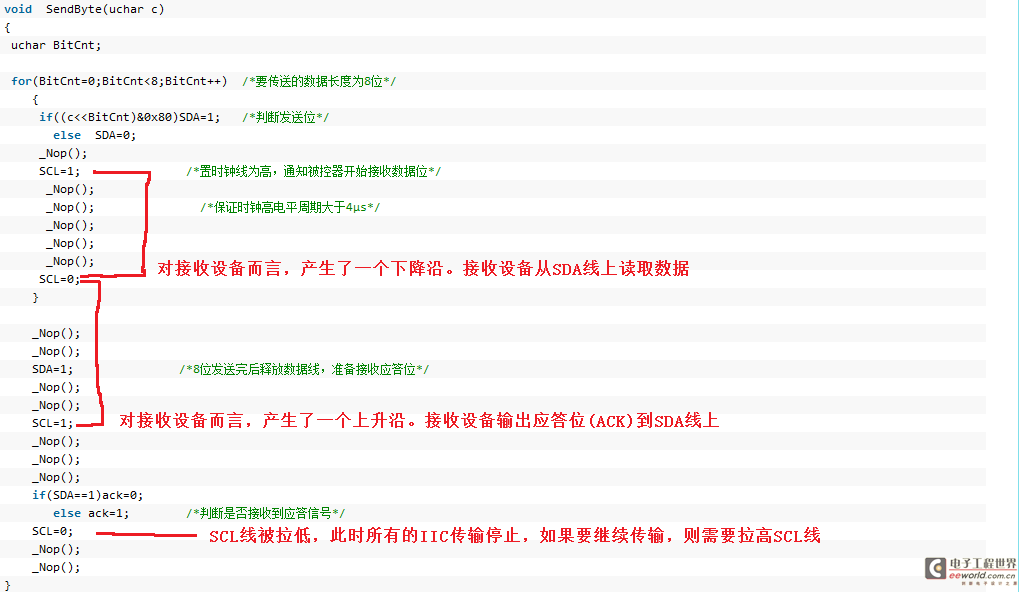

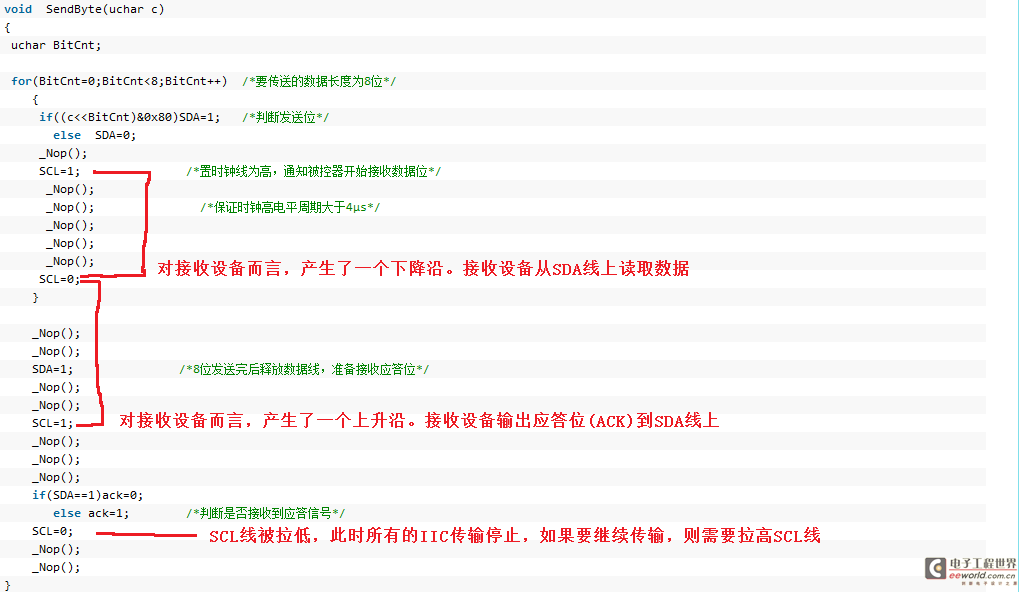

下面是發送數據的時序變化具體分析。

再來看一下接收數據時的時序的變化。

IIC總線協議的學習暫告一段落,開始SPI總線的學習!

帶著這個問題,我在圖書館找了好幾天的資料。終于弄懂了。

每bit數據定義

下面再來看一下IIC總線時序的具體定義:

其中, 是數據建立的時間;

是數據建立的時間; 是數據保持時間。上升沿將數據送到SDA線上,

是數據保持時間。上升沿將數據送到SDA線上, 是建立時間。高電平期間數據穩定,等待下降沿讀取SDA線上的數據。下降沿從SDA線上讀取數據,下降沿之后的

是建立時間。高電平期間數據穩定,等待下降沿讀取SDA線上的數據。下降沿從SDA線上讀取數據,下降沿之后的 是保持時間。

是保持時間。

下面是發送數據的時序變化具體分析。

再來看一下接收數據時的時序的變化。

IIC總線協議的學習暫告一段落,開始SPI總線的學習!

評論